Verilog实战:HDL语言详解与ASIC设计实例

版权申诉

121 浏览量

更新于2024-07-03

收藏 228KB PDF 举报

本资源是一份名为"HDL语言与ASIC原理:Verilog设计实例1.pdf"的文档,主要介绍了Verilog硬件描述语言在ASIC设计中的应用。Verilog是广泛用于数字系统设计的一种高级硬件描述语言,它被用于描述电子系统的逻辑行为,特别是在集成电路(Integrated Circuit,IC)特别是应用特定集成电路(Application-Specific Integrated Circuit,ASIC)的设计过程中。

文档的第一部分着重于逻辑设计的基础,通过实例来讲解。首先,半加器的原理图被详细展示,包括其输入(a、b)和输出(c_out、sum)以及Verilog代码实现,如`module Add_half_0_delay...`,其中涉及到了`xor`和`and`操作。这个模块展示了基本逻辑门的使用,即半加器由异或(XOR)和与(AND)逻辑门组成。

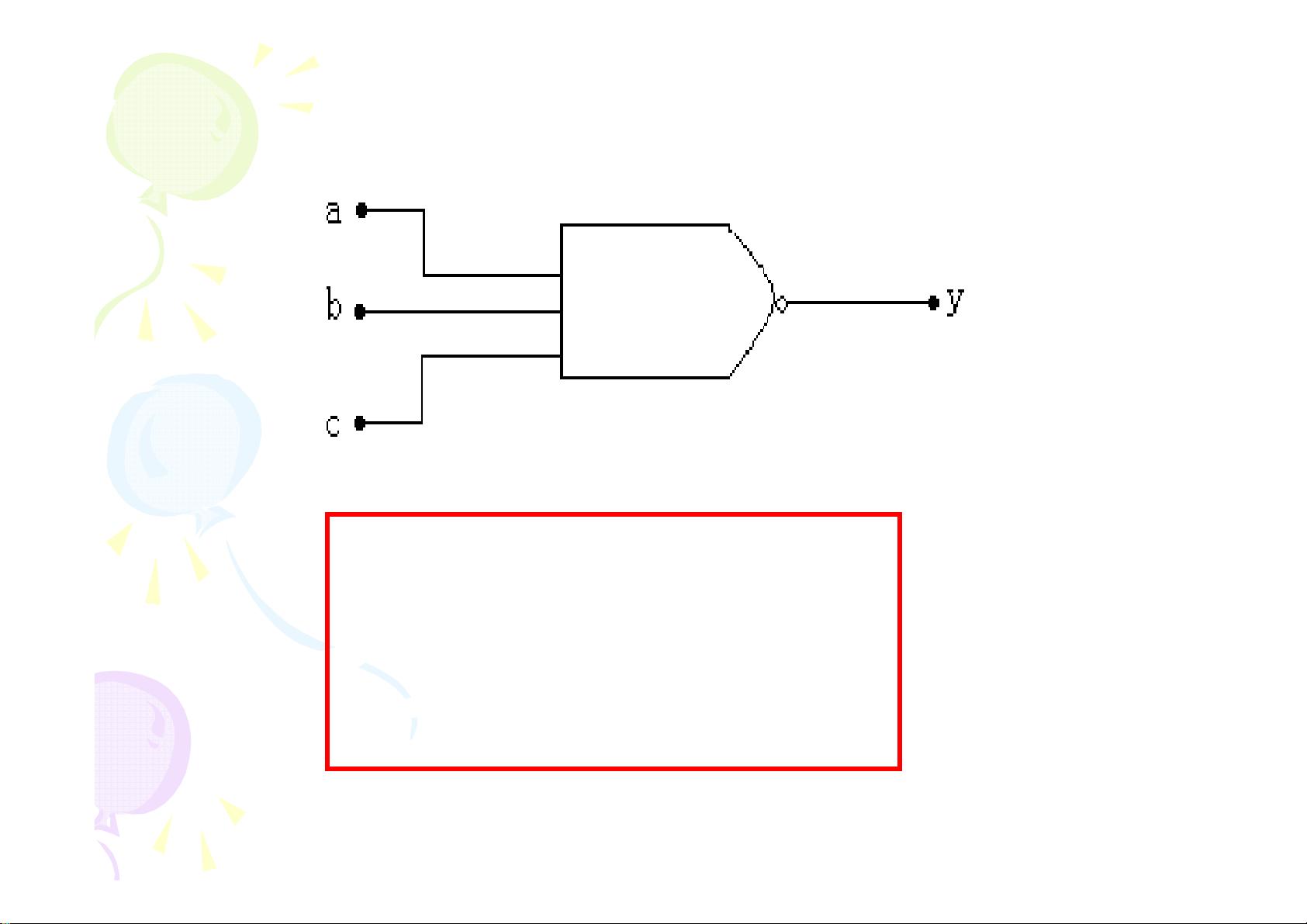

接着,文档介绍了三输入与非门的Verilog原语化举例,强调了如何使用`nand`函数来表示这种门的功能。这展示了如何通过组合基本门原语来构建更复杂的逻辑功能。

进一步,文档涉及到有5输入的与非门(AOI),其功能和连接方式的声明,同时提到了用`wire`变量来管理和连接这些门。全加器电路作为复杂度提升的例子,其门级电路原理图被详细展示,其中包括全加器模块`Add_full_0_delay`,该模块内部使用了两个延迟未考虑的半加器模块`Add_half_0_delay`。

全加器是一个重要的数字逻辑电路,它能够处理二进制数的相加,对于计算机和数字信号处理系统至关重要。通过全加器的示例,学习者可以理解如何将基础逻辑单元模块化并组合成具有完整功能的电路。

这份文档提供了实用的Verilog设计实例,适合初学者了解和实践HDL语言,逐步掌握ASIC设计中的基本原理和技巧。阅读和实践这些实例有助于理解逻辑门行为、模块化设计和系统级建模,是进行数字电路设计的重要参考资料。

2021-09-21 上传

2021-09-21 上传

2022-06-18 上传

2021-09-21 上传

2022-05-07 上传

2021-09-21 上传

2021-09-21 上传

C2000,28335Matlab Simulink代码生成技术,处理器在环,里面有电力电子常用的GPIO,PWM,ADC,DMA,定时器中断等各种电力电子工程师常用的模块儿,只需要有想法剩下的全部自

1436 浏览量

2025-01-04 上传

智慧安全方案

- 粉丝: 3844

- 资源: 59万+

最新资源

- Java职位面试之Java基础知识

- MPEG基础和协议分析指南

- RealTime OS Systems

- ATA-6 hard disk operation

- 微软软件测试面试考题

- c#数据结构 第一章概述ppt

- C++初学者的最佳资源PDF

- 长春理工大学应用光学课件.pdf

- MyEclipse+6+Java+开发中文教程_免费电子版.pdf

- 在VC中利用Kodak控件采集图像

- DB2数据库学习手册

- STL编程指南--详细的sgi参考手册

- 计算机网络统考串讲(习题部分)

- Oracle9i Database Administration Fundamentals I Ed 2.0.pdf

- unix C 字符串处理学习

- Oracle9i+数据库管理基础+IIVol.2.pdf