低成本FPGA解决方案:IP摄像机的高清与WDR设计

需积分: 0 134 浏览量

更新于2024-08-31

收藏 476KB PDF 举报

随着视频监控市场的快速发展,技术挑战层出不穷,从模拟向数字摄像机的转变、高清(HD)视频的普及、宽动态范围(WDR)传感器的应用,以及对IP连接的需求,都对系统的性能和成本提出了新的要求。本文探讨了如何利用现场可编程门阵列(FPGA)构建低成本的IP监视摄像机,特别是采用低成本的Altera Cyclone III FPGA作为核心组件。

首先,从模拟到数字的过渡是关键步骤,因为高清视频必须是数字化的,这需要高性能的数字信号处理器(DSP)来支持H.264等高效压缩算法,以提供高帧率和分辨率。同时,宽动态范围(WDR)传感器在不同光照条件下能捕捉到丰富的图像细节,这对于实时处理和监控至关重要。

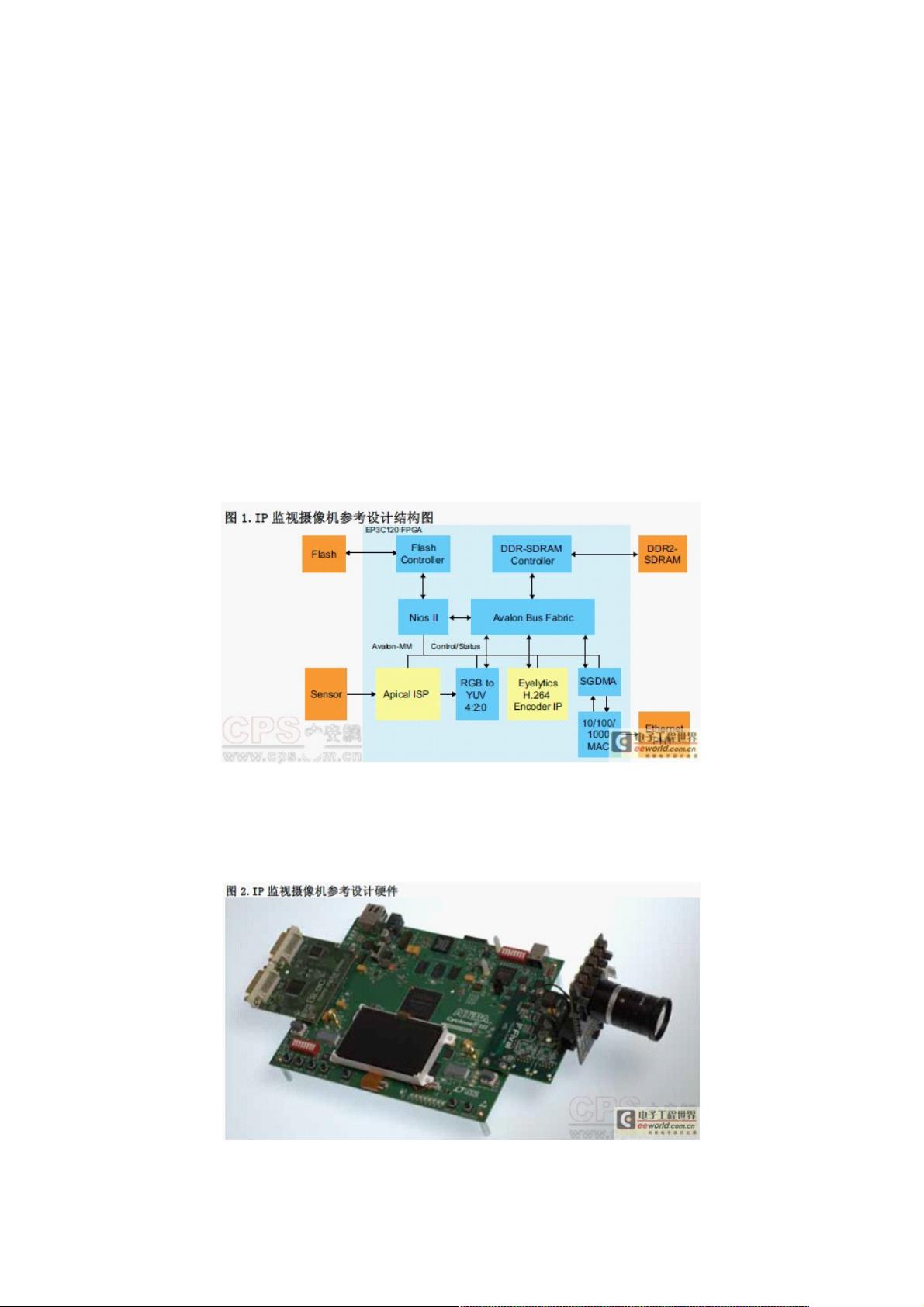

文章的核心部分是IP监视摄像机的参考设计,它构建在Cyclone IIIEP3C120开发板上,结合了Altera的硬件和多家合作伙伴的知识产权。设计流程包括:Aptina MT9M033 WDR传感器捕获图像数据,Apical的图像传感器流水线(ISP)进行预处理,输出YUV 4:2:0格式的数据并存入外部DDR2 SDRAM的帧缓冲区,利用Altera的VIP套件进行进一步的视频和图像处理。EyeLytics的内核负责以H.264格式对视频进行编码,支持高码率的视频流传输。此外,通过Altera的TSE MegaCore功能,SGDMA控制器实现了高速的以太网通信,确保了数据的实时传输至远程客户端。

这个参考设计充分展示了如何在保持高清晰度和宽动态范围的同时,利用FPGA实现低成本、高性能的IP摄像机解决方案,使得监控系统能够在各种复杂环境中稳定工作,并适应市场需求的不断变化。对于监控与报警系统的设计者和开发者来说,这是一个极具价值的学习和实践案例。

2021-05-18 上传

2021-07-13 上传

2021-04-27 上传

2021-05-24 上传

点击了解资源详情

点击了解资源详情

2021-07-13 上传

2020-08-30 上传

weixin_38690275

- 粉丝: 7

- 资源: 972

最新资源

- Raspberry Pi OpenCL驱动程序安装与QEMU仿真指南

- Apache RocketMQ Go客户端:全面支持与消息处理功能

- WStage平台:无线传感器网络阶段数据交互技术

- 基于Java SpringBoot和微信小程序的ssm智能仓储系统开发

- CorrectMe项目:自动更正与建议API的开发与应用

- IdeaBiz请求处理程序JAVA:自动化API调用与令牌管理

- 墨西哥面包店研讨会:介绍关键业绩指标(KPI)与评估标准

- 2014年Android音乐播放器源码学习分享

- CleverRecyclerView扩展库:滑动效果与特性增强

- 利用Python和SURF特征识别斑点猫图像

- Wurpr开源PHP MySQL包装器:安全易用且高效

- Scratch少儿编程:Kanon妹系闹钟音效素材包

- 食品分享社交应用的开发教程与功能介绍

- Cookies by lfj.io: 浏览数据智能管理与同步工具

- 掌握SSH框架与SpringMVC Hibernate集成教程

- C语言实现FFT算法及互相关性能优化指南