FPGA实现的32位高速浮点乘法器:流水线优化与性能提升

163 浏览量

更新于2024-09-01

收藏 410KB PDF 举报

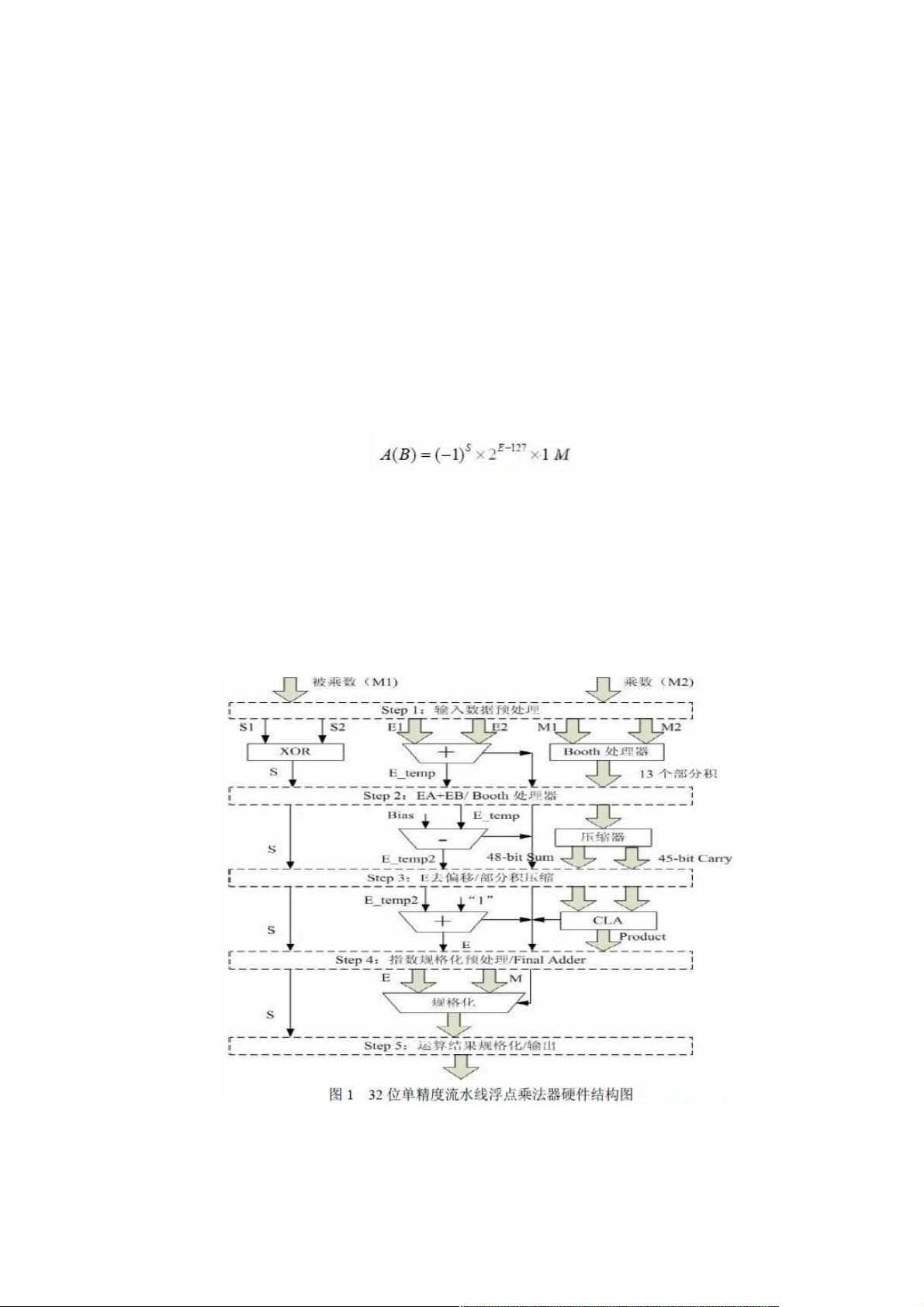

本文介绍了一种基于FPGA的32位高速流水线浮点乘法器设计,该设计遵循IEEE754浮点标准,旨在提高微处理器性能。设计采用了新型基4布思算法,结合改进的4:2压缩结构和部分积求和电路,以实现Carry Save形式的部分积压缩。然后利用Carry Look-ahead加法器快速求得最终乘积。通过时序仿真,该乘法器能够在80MHz的频率下稳定运行,并已在浮点FFT处理器中得到应用。

1. 引言

随着数字技术的发展,对高性能微处理器的需求不断增长,其中乘法器的速度和精度至关重要。浮点运算,特别是遵循IEEE754标准的浮点运算,因其大动态范围、高精度和简洁的运算规则,成为高性能计算的重要组成部分。本文提出的32位浮点乘法器设计正是针对这一需求,旨在优化浮点运算性能。

2. 运算规则与系统结构

2.1 浮点数表示

遵循IEEE754单精度格式,浮点数由三部分组成:符号位、指数位和尾数位。在32位浮点数中,指数为8位,尾数为23位,还有一个隐藏的1位。

2.2 硬件结构

为满足高速运算需求,设计采用了流水线技术,充分利用FPGA的并行处理能力。5级流水处理使得数据在多个阶段并行处理,提高了运算速度。设计包括指数处理模块(E_Adder)和其他关键模块。

3. 主要模块设计与仿真

3.1 指数处理模块(E_Adder)

E_Adder模块处理浮点数的指数部分,采用8位超前进位加法器完成指数相加、去偏移等操作。指数偏移值Bias=127是IEEE754标准中预设的。指数的规格化操作与尾数乘积紧密关联,通过优化设计,能够快速得到乘积的指数部分。

4. 布局与优化

设计中采用的基4布思算法能有效减少计算步骤,4:2压缩结构减少了部分积的存储需求,Carry Save形式的部分积压缩则降低了加法器的延迟。Carry Look-ahead加法器通过提前计算进位,进一步减少了延迟,确保了整个系统的高速运行。

5. 结果与应用

时序仿真验证了该乘法器的稳定性,能在80MHz的时钟频率下工作。实际应用中,该设计已被集成到一个浮点FFT处理器中,显示了其在实时信号处理领域的潜力。

6. 总结

该高速流水线浮点乘法器设计结合了先进的算法和FPGA的优势,实现了高效的浮点运算。这种设计方法为高性能计算和信号处理提供了重要的硬件支持,具有广泛的应用前景。未来的研究可能会进一步优化设计,提升效率和灵活性,以适应更多复杂的计算任务。

2021-07-13 上传

2020-10-16 上传

2023-09-07 上传

2023-05-12 上传

2024-08-16 上传

2023-07-09 上传

2023-07-18 上传

2023-06-12 上传

2023-05-29 上传

weixin_38699492

- 粉丝: 8

- 资源: 946

最新资源

- 批量文件重命名神器:HaoZipRename使用技巧

- 简洁注册登录界面设计与代码实现

- 掌握Python字符串处理与正则表达式技巧

- YOLOv5模块改进 - C3与RFAConv融合增强空间特征

- 基于EasyX的C语言打字小游戏开发教程

- 前端项目作业资源包:完整可复现的开发经验分享

- 三菱PLC与组态王实现加热炉温度智能控制

- 使用Go语言通过Consul实现Prometheus监控服务自动注册

- 深入解析Python进程与线程的并发机制

- 小波神经网络均衡算法:MATLAB仿真及信道模型对比

- PHP 8.3 中文版官方手册(CHM格式)

- SSM框架+Layuimini的酒店管理系统开发教程

- 基于SpringBoot和Vue的招聘平台完整设计与实现教程

- 移动商品推荐系统:APP设计与实现

- JAVA代码生成器:一站式后台系统快速搭建解决方案

- JSP驾校预约管理系统设计与SSM框架结合案例解析