Xilinx FPGA视频时序控制器IP使用指南

版权申诉

"该资源是Xilinx公司提供的关于Video Timing Controller v6.2 LogiCORE IP的用户指导手册,旨在帮助开发者理解和使用该IP核进行FPGA开发,特别是在VGA时序控制方面。"

在Xilinx FPGA开发中,Video Timing Controller (VTC) IP核是一个至关重要的组件,它主要用于处理视频显示相关的时序控制任务。以下是该IP核的一些关键知识点:

1. **IP Facts**: 该章节提供IP核的基本信息,包括VTC v6.2的核心功能、特性概述以及可能的应用场景。

2. **产品规格**: 这部分详细阐述了VTC遵循的视频标准(如VESA、HDMI等),性能参数,如时钟速度、带宽需求等。同时,它也展示了资源利用率,包括FPGA逻辑单元、存储器资源的占用情况。

3. **核心接口与寄存器空间**: VTC的核心设计包括了多个接口,如像素输入/输出接口、时钟输入/输出、配置接口等。寄存器空间定义了用于配置IP核的各个控制寄存器,这些寄存器可调整IP的行为以适应不同的视频时序。

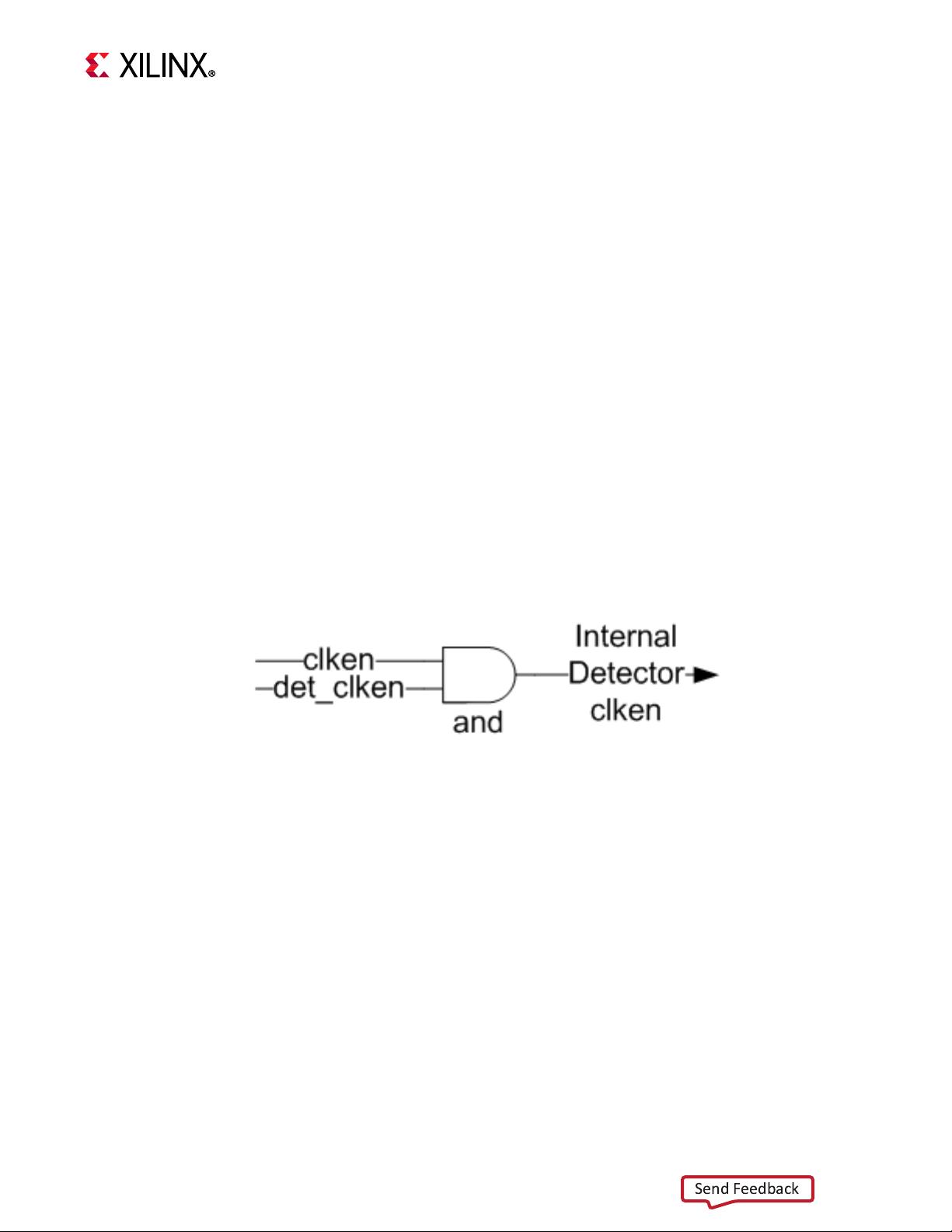

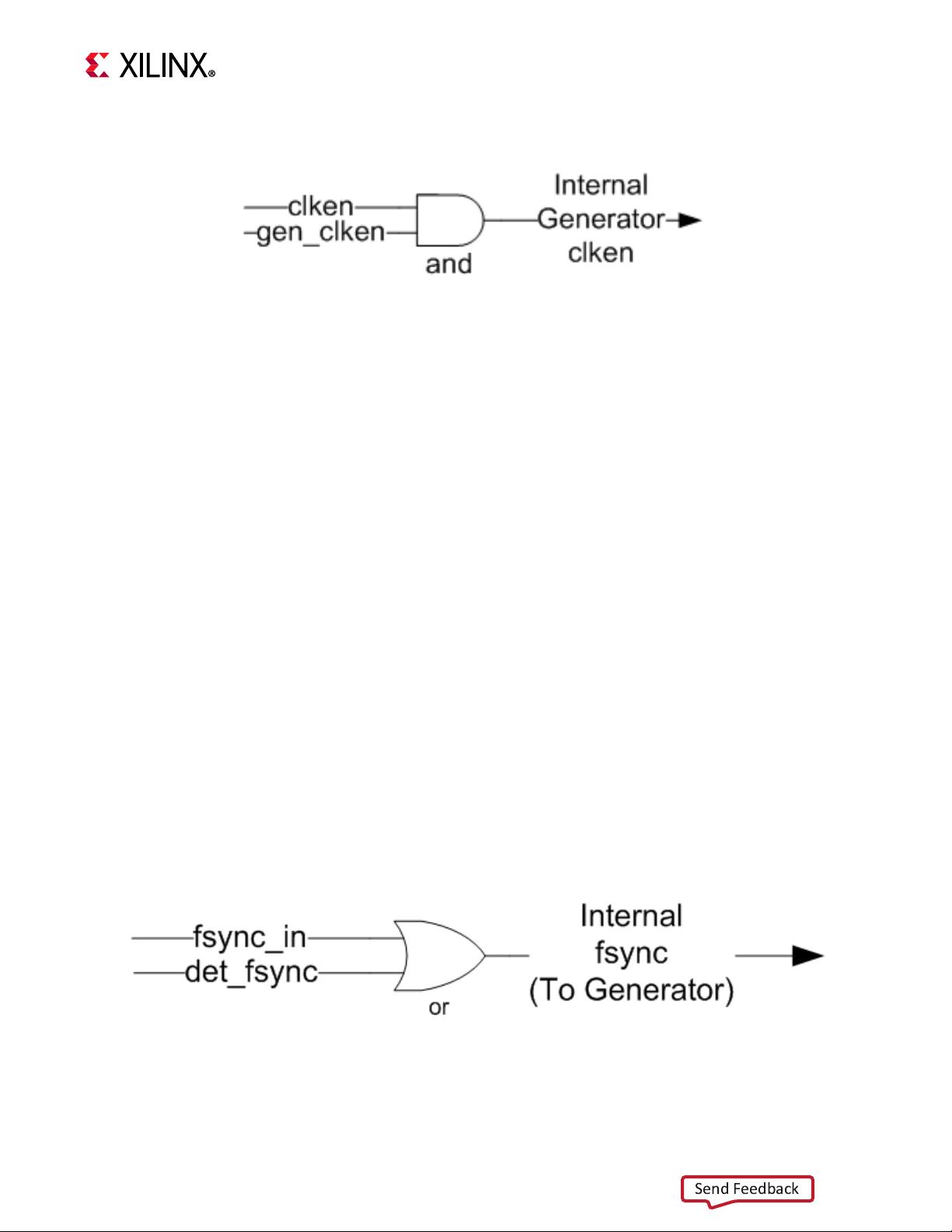

4. **基本架构**: 描述了VTC的内部结构,包括控制信号与时序,以及如何通过这些信号来同步和驱动VGA显示器。控制信号如HSync、VSync、DE(数据有效)等,是确保视频数据正确传输的关键。

5. **设计流程步骤**: 提供了定制和生成IP核的详细步骤,包括使用图形用户界面(GUI)进行配置,设置约束条件,进行仿真,以及后续的综合和实现过程。

6. **示例设计**: 包含了一个或多个示例设计,这些设计展示了如何将VTC IP集成到实际的FPGA设计中,为开发者提供了实践参考。

7. **测试平台**: 提供了演示测试平台的信息,用于验证IP核的功能正确性和兼容性。这包括软件模拟和硬件测试,确保设计在实际环境中的工作性能。

8. **升级指南**: 针对那些需要将设计迁移到Vivado Design Suite的开发者,提供了迁移和升级的详细步骤。

"pg016 Video Timing controller LogiCORE IP Product Guide" 是一份全面的文档,涵盖了从理解VTC工作原理到实际设计应用的各个环节,对于在Xilinx FPGA上处理视频时序控制的开发者来说,是一份宝贵的参考资料。通过学习这份指南,开发者能够有效地利用VTC IP核实现高效的视频处理和显示功能。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-03-23 上传

2019-03-08 上传

2013-01-08 上传

2019-11-24 上传

2024-11-26 上传

2019-04-25 上传

风中月隐

- 粉丝: 2w+

- 资源: 35

最新资源

- F5-模拟器 F5-模拟器.zip

- HTML5+CSS+JS精品网页模板 大学生期末大作业 Web前端网页制作

- node-card-game:多人浏览器游戏

- Scripts_public:适用于客户或我们的所有小型开发脚本

- Perfect-Stripe:服务器端Swift 3 Stripe API

- Android系统原理与开发要点详解-培训课件.rar

- 行业资料-电子功用-利用时基集成电路的高性能电子镇流器的介绍分析.rar

- PyCoders:这是我使用 Bootstrap 制作的 PyCoders 博客

- udemy_regex:学习正则表达式

- 机械设计空调保护器底板焊接检测(sw20可编辑+工程图)非常好的设计图纸100%好用.zip

- 游泳池及公共浴池水系统管道及配件(2022版)共2页.pd

- RealRichard_D

- 【WordPress插件】2022年最新版完整功能demo+插件2019-10-11.zip

- websocket-mock:用于单元测试的 WebSocket API 的简单模拟

- ansible-role-kafka:Ansible角色,用于管理Apache Kafka的安装和配置

- 行业分类-外包设计-接触透镜的包装件的介绍分析.rar