Xilinx Zynq 7000入门教程:Vivado Design Suite实践

需积分: 9 120 浏览量

更新于2024-07-19

收藏 4.49MB PDF 举报

"Xilinx Zynq 7000系列嵌入式处理器硬件设计教程"

Xilinx Zynq 7000系列是一款高度集成的系统级芯片(SoC),结合了可编程逻辑(FPGA)与双核或四核ARM Cortex-A9处理系统(PS),提供了强大的异构计算能力。这个入门级别的教学文档,"UG940-Xilinx zynq tutorial" 是针对Xilinx Vivado Design Suite的一个教程,适用于那些想要学习如何在Zynq平台上进行硬件设计和嵌入式处理器编程的初学者。

该文档在2017年进行了两次更新,版本分别为2017.1和2017.2。虽然内容在2017.2版本中没有重大变化,但确保了与最新版本的Vivado Design Suite兼容性。Vivado Design Suite是Xilinx开发的一款综合性设计环境,用于FPGA和SoC的设计、实现、仿真、调试以及硬件编程。

教程涵盖了嵌入式处理器的硬件设计,包括以下几个主要部分:

1. **编程和调试嵌入式处理器**:这部分内容可能涉及如何配置和编程Zynq SoC的处理系统,以及如何使用Vivado工具进行调试。

2. **硬件和软件要求**:在开始设计之前,需要明确所需的硬件设备,如开发板和计算机配置,以及软件环境,包括Vivado Design Suite和可能的软件开发工具链(如ARM交叉编译器和JTAG接口工具)。

3. **教程设计描述**:详细介绍了教程中所用到的设计实例,帮助读者理解Zynq SoC设计的基本流程。

4. **查找教程设计文件**:指导用户如何获取和组织设计文件,这对于遵循教程步骤进行实践操作至关重要。

5. **实验一:构建Zynq-7000 AP SoC处理器设计**:

- **介绍**:简述实验目标和预期成果。

- **步骤1:启动Vivado IDE并创建项目**:讲解如何启动Vivado环境,并设置一个新的项目,这是所有设计的基础。

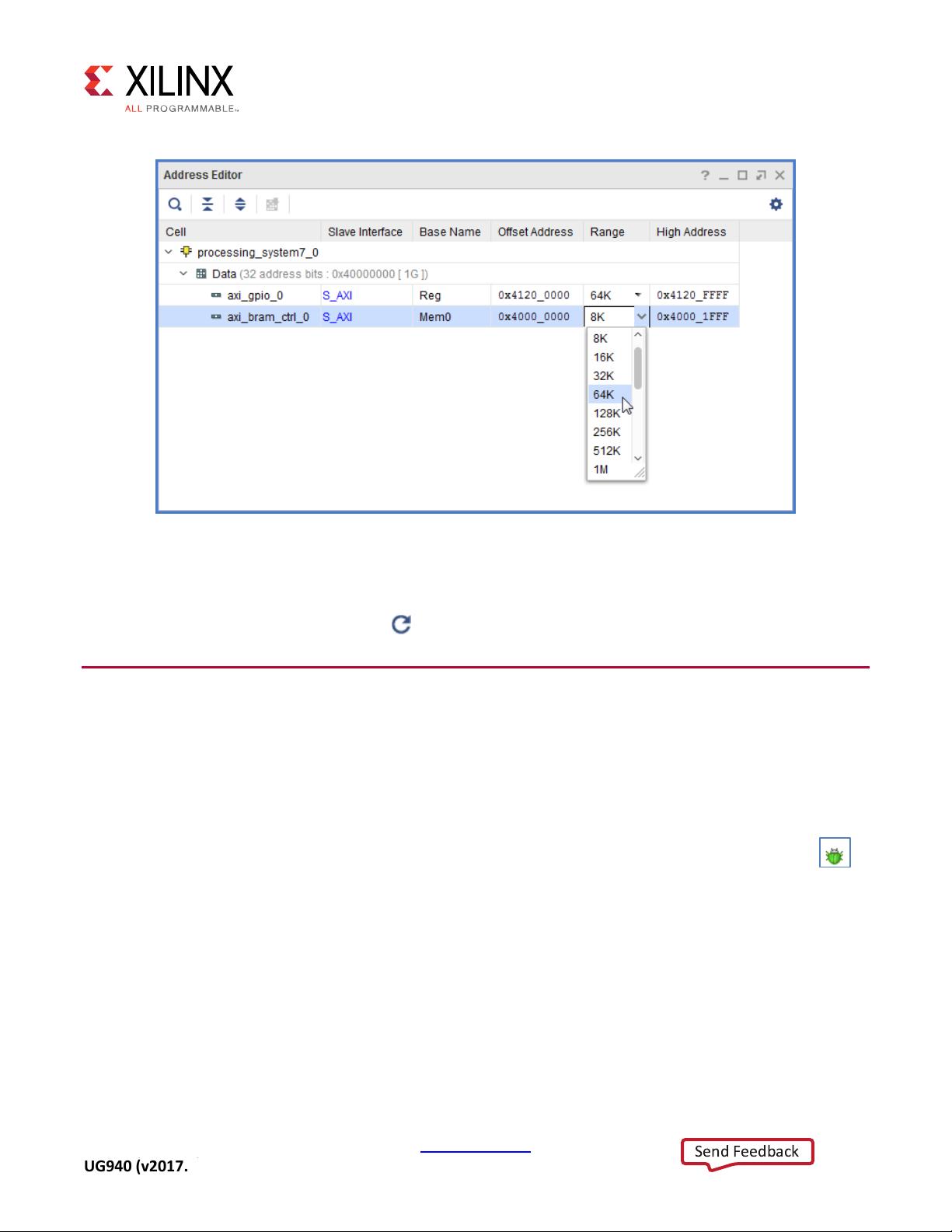

- **步骤2:创建IP Integrator设计**:介绍如何使用IP Integrator工具来集成不同的硬件模块,如处理器、内存接口、外设等。

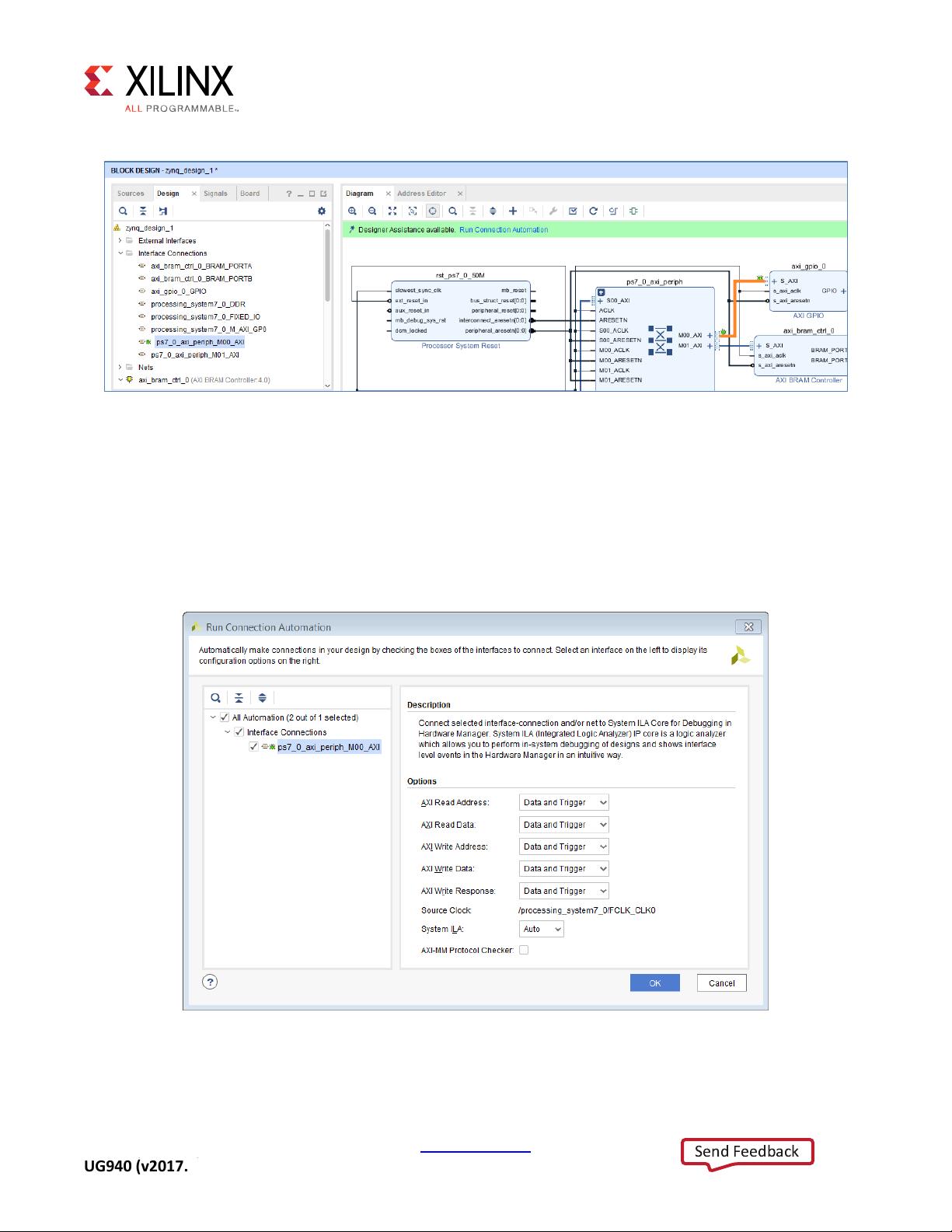

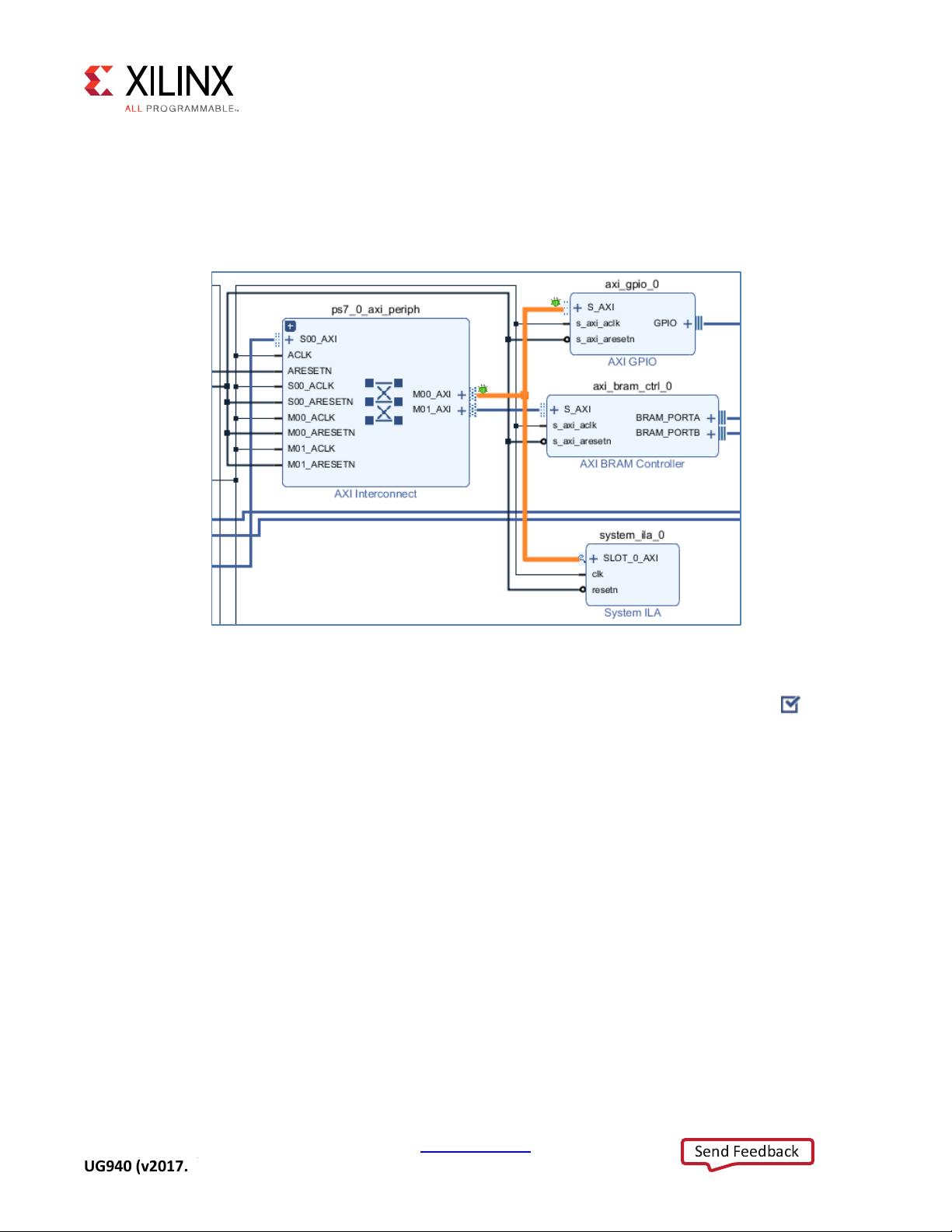

- **步骤3:调试Block Design**:演示如何使用Vivado的调试工具来检查和验证设计的正确性。

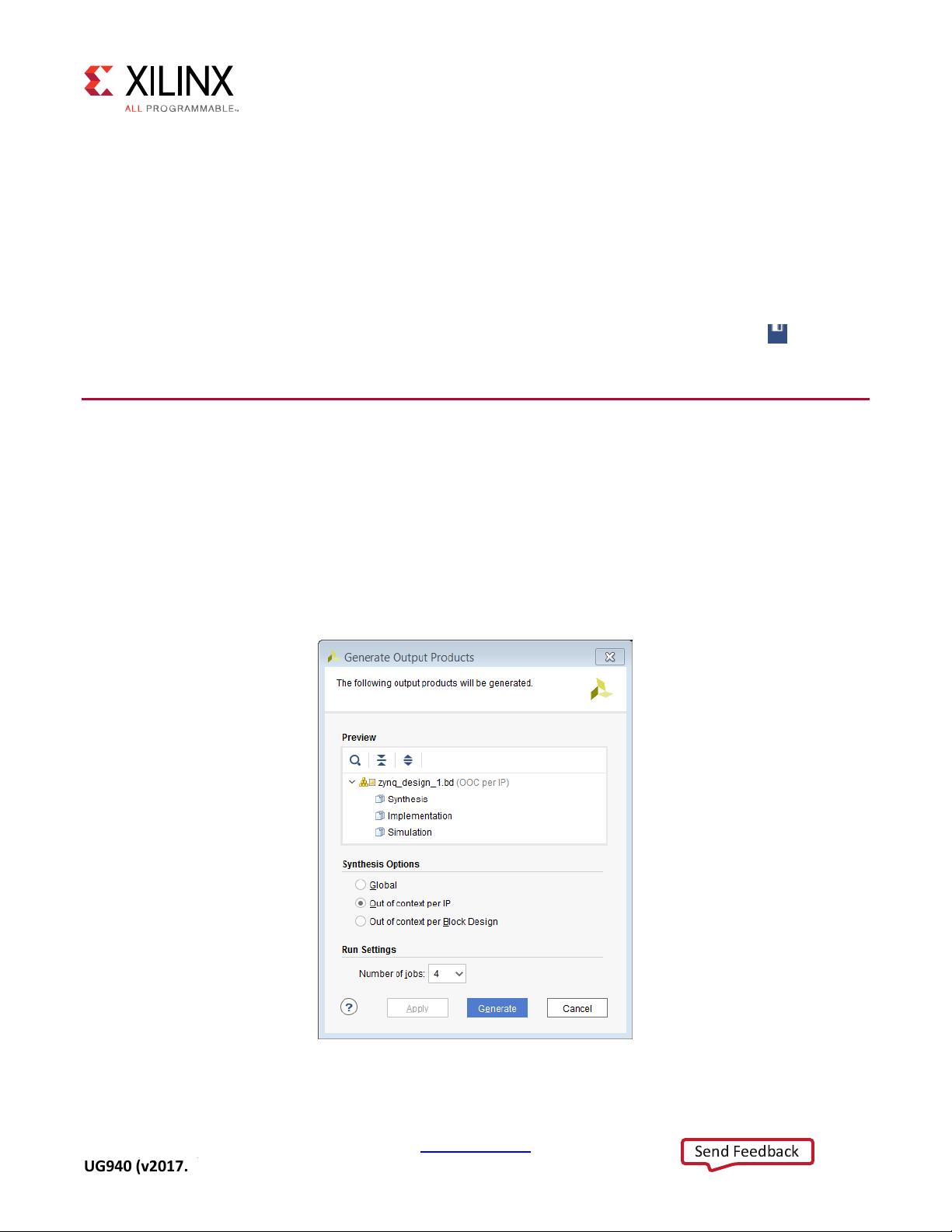

- **步骤4:生成HDL设计文件**:说明如何将Block Design转换为硬件描述语言(HDL,如Verilog或VHDL)代码。

- **步骤5:实现设计**:指导如何使用Vivado工具进行综合、布局布线,以及生成比特流文件,这是最终编程到FPGA中的硬件配置。

通过这个教程,学习者可以掌握如何在Vivado环境中搭建一个基本的Zynq SoC设计,包括创建IP核、连接硬件组件、调试设计以及生成可编程文件。此外,教程可能还涉及了软件开发的初步概念,如编写和下载Bootloader,以及在ARM处理器上运行简单的应用程序。

"UG940-Xilinx zynq tutorial"为开发者提供了一个全面的起点,使他们能够理解和利用Xilinx Zynq 7000系列的强大功能,进行嵌入式系统的开发和实现。

2016-04-27 上传

2021-09-29 上传

2023-06-22 上传

2023-07-02 上传

2023-06-20 上传

2023-08-15 上传

2023-11-24 上传

2023-10-13 上传

2023-06-10 上传

qq_27891597

- 粉丝: 0

- 资源: 2

最新资源

- 新型智能电加热器:触摸感应与自动温控技术

- 社区物流信息管理系统的毕业设计实现

- VB门诊管理系统设计与实现(附论文与源代码)

- 剪叉式高空作业平台稳定性研究与创新设计

- DAMA CDGA考试必备:真题模拟及章节重点解析

- TaskExplorer:全新升级的系统监控与任务管理工具

- 新型碎纸机进纸间隙调整技术解析

- 有腿移动机器人动作教学与技术存储介质的研究

- 基于遗传算法优化的RBF神经网络分析工具

- Visual Basic入门教程完整版PDF下载

- 海洋岸滩保洁与垃圾清运服务招标文件公示

- 触摸屏测量仪器与粘度测定方法

- PSO多目标优化问题求解代码详解

- 有机硅组合物及差异剥离纸或膜技术分析

- Win10快速关机技巧:去除关机阻止功能

- 创新打印机设计:速释打印头与压纸辊安装拆卸便捷性