Verilog实现的8位简单计算器:加减乘除与开根

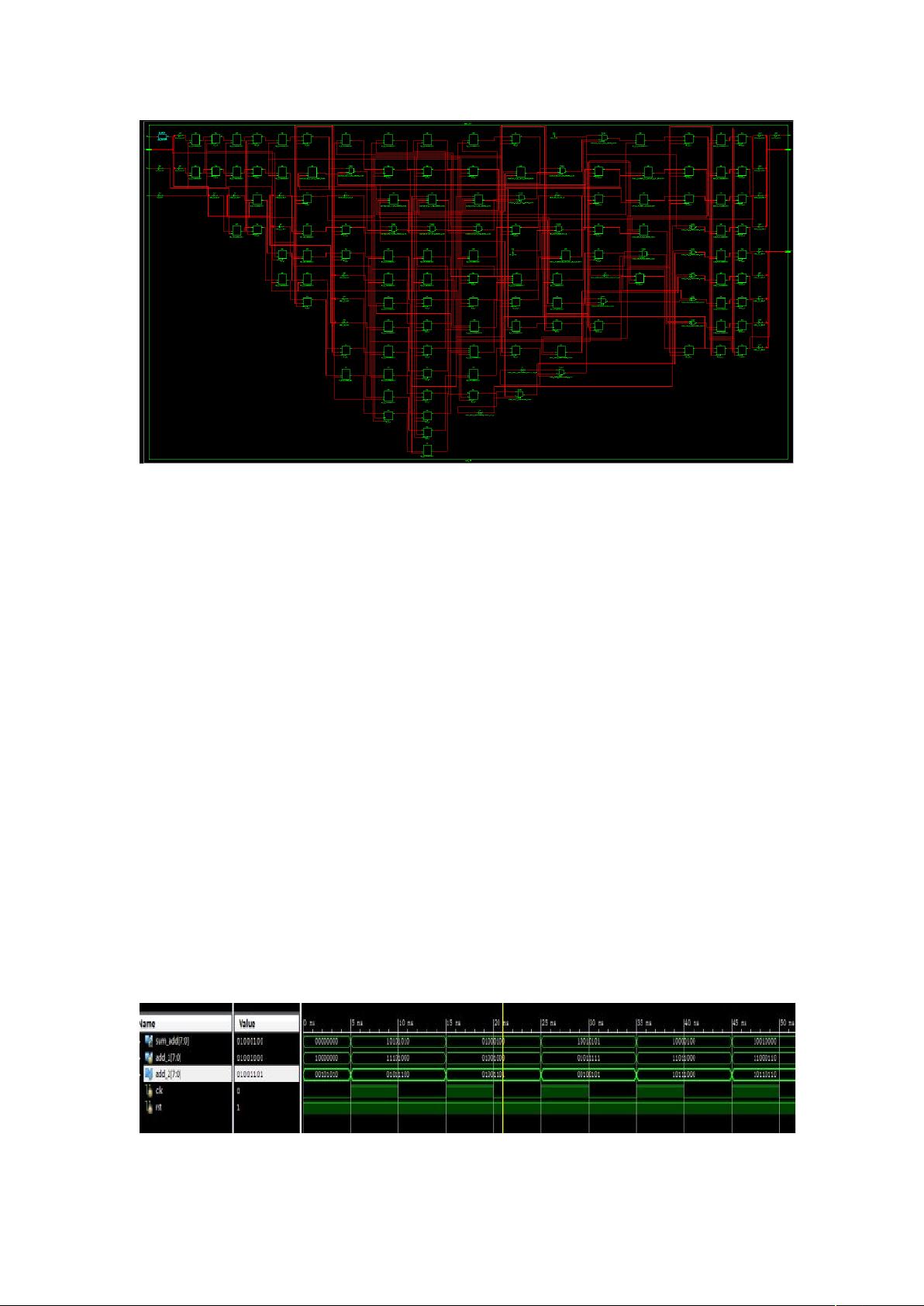

该文档详细介绍了如何使用Verilog语言设计一个简单的计算器,涵盖了8位二进制的加、乘、平方、除、开根号五种运算。实验中,Verilog HDL语言被用来编写代码并进行仿真。加法器模块基于全加器原理,除法器利用Moore状态机实现多次循环以求得商和余数,根号器则采用逐次逼近法进行迭代计算。实验还探讨了扩展方法,如将8位计算器扩展至16位,以及通过管脚约束将仿真转化为硬件实现,使用Spartan3E FPGA作为硬件平台。此外,还介绍了如何通过修改平方器来增加指数运算功能。

1. Verilog语言介绍

Verilog HDL是一种硬件描述语言,被广泛应用于数字系统设计,允许描述从门级到行为级的电子系统。它遵循IEEE标准,具有丰富的设计库和易学习的特点,支持模块化设计,便于复用和组合不同功能的模块。

2. 计算器模块设计

- 加法器模块:基于全加器实现,能处理8位二进制的加法操作。

- 乘法器模块:执行两个输入信号的乘法运算。

- 平方器模块:对第一个输入信号进行平方计算。

- 除法器模块:使用Moore状态机进行除法运算,通过多次迭代得到商和余数。

- 根号器模块:应用逐次逼近法,通过迭代计算找到最接近的数字,分别输出3位的商和4位的余数。

3. 实验优化

- 位数扩展:将8位计算器扩展到16位,增强计算器的处理能力。

- 输入类型扩展:通过调整仿真信号,支持负数和小数的计算。

- 硬件软件结合:通过管脚约束,将设计从软件仿真转移到实际的FPGA硬件平台上,如Spartan3E,利用按钮和LED显示计算过程。

- 功能增强:通过修改平方器,增加了指数运算功能。

4. 仿真与验证

实验通过random函数生成随机输入信号进行仿真,验证各模块的功能正确性。输出信号为二进制形式,确保计算结果的准确无误。

5. 结论

基于Verilog的简单计算器设计展示了如何使用硬件描述语言实现复杂的计算操作,包括基础的算术运算以及更高级的开根号功能。通过模块化设计和优化,不仅实现了基本的计算需求,还提供了扩展性和硬件实现的可能性,对于理解和应用FPGA设计有重要的教学价值。

108 浏览量

2022-07-14 上传

133 浏览量

2022-11-16 上传

2017-07-03 上传

2022-10-13 上传

190 浏览量

130 浏览量

2022-06-16 上传

是益毛啊

- 粉丝: 1

最新资源

- 老板数据库的管理与应用

- Matlab文件导航工具:跨平台目录管理新体验

- Topshelf实现Windows服务开发快速指南

- 全栈技术项目源码合集,助力学习与开发

- PHP实现Slack回发机器人Slacker

- zdict:掌握多种词典的强大Python在线框架

- Twilio代理协助支付:Python实现的概念验证应用

- MesaggeApp:CSS技术应用与前端开发实践

- MATLAB命令窗口增强:文件资源管理与快速操作

- 海康摄像头CH_WEB3.0控件开发包1.1.0版本介绍

- VB实现禁用与更换桌面属性的简易教程

- 基于Spring Boot与Vue的课程管理评价系统设计

- 揭秘巴科特·康托尔:Python技术的光辉

- 64位PACS影像浏览器:无需安装,直接使用

- JCash:开源Java资金管理应用详解

- QSufsort算法:字符串排序的高效实现