DDR3存储技术详解:从IP核配置到数据读写

需积分: 5 102 浏览量

更新于2024-06-18

收藏 3.12MB PPTX 举报

"DDR3存储器技术讲解及其在FPGA中的配置与调试方法"

DDR3(Double Data Rate Third Generation Synchronous Dynamic Random-Access Memory)是一种高速、低功耗的内存技术,广泛应用于各种数字系统,包括计算机、服务器以及嵌入式系统等。本章将深入探讨DDR3内存的实例应用,主要分为三个方面:DDR3 IP核的配置与仿真、基于在线逻辑分析仪的DDR3数据读写调试,以及基于UART命令的DDR3批量数据读写。

1. DDR3 IP核配置与仿真:

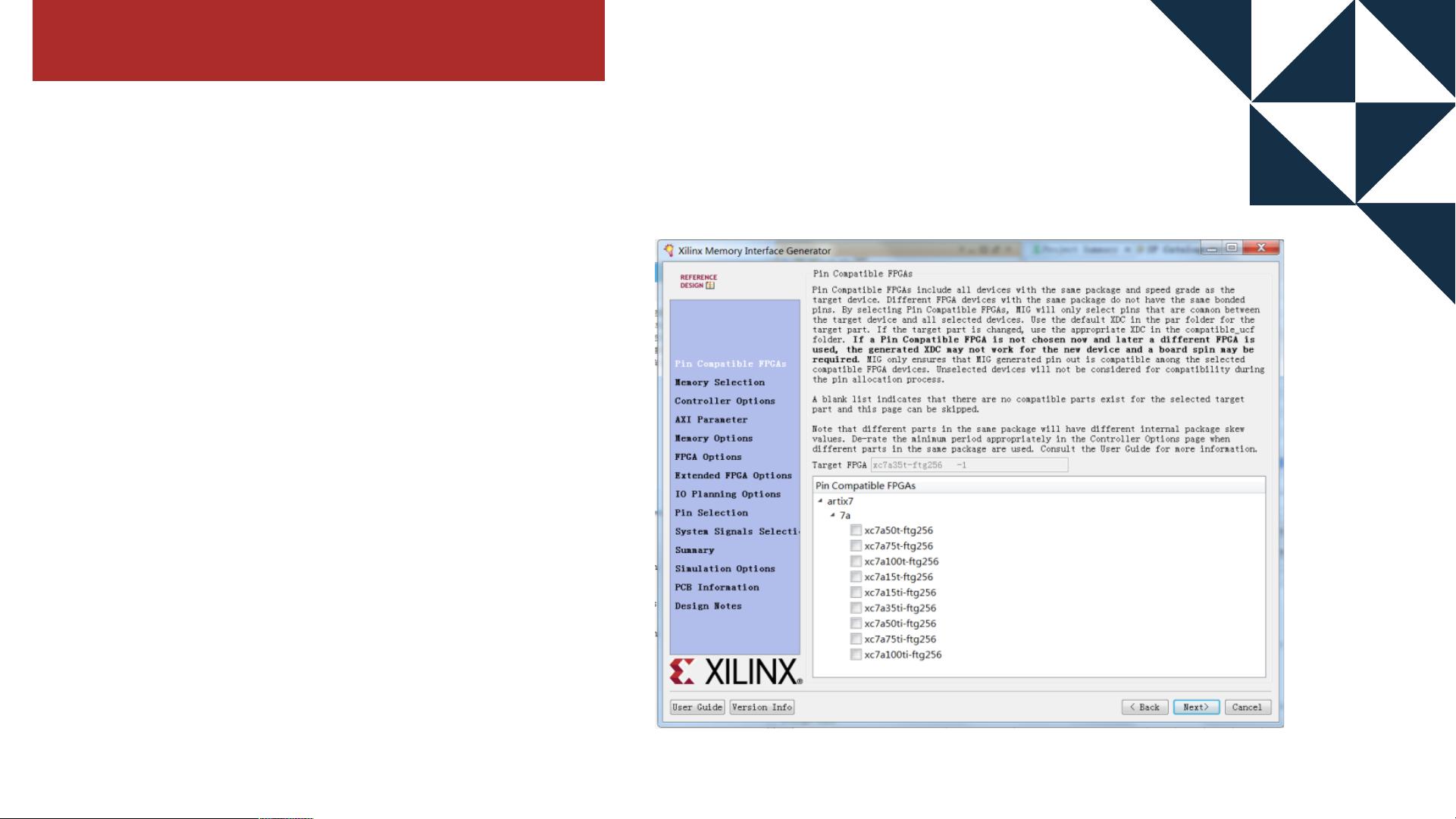

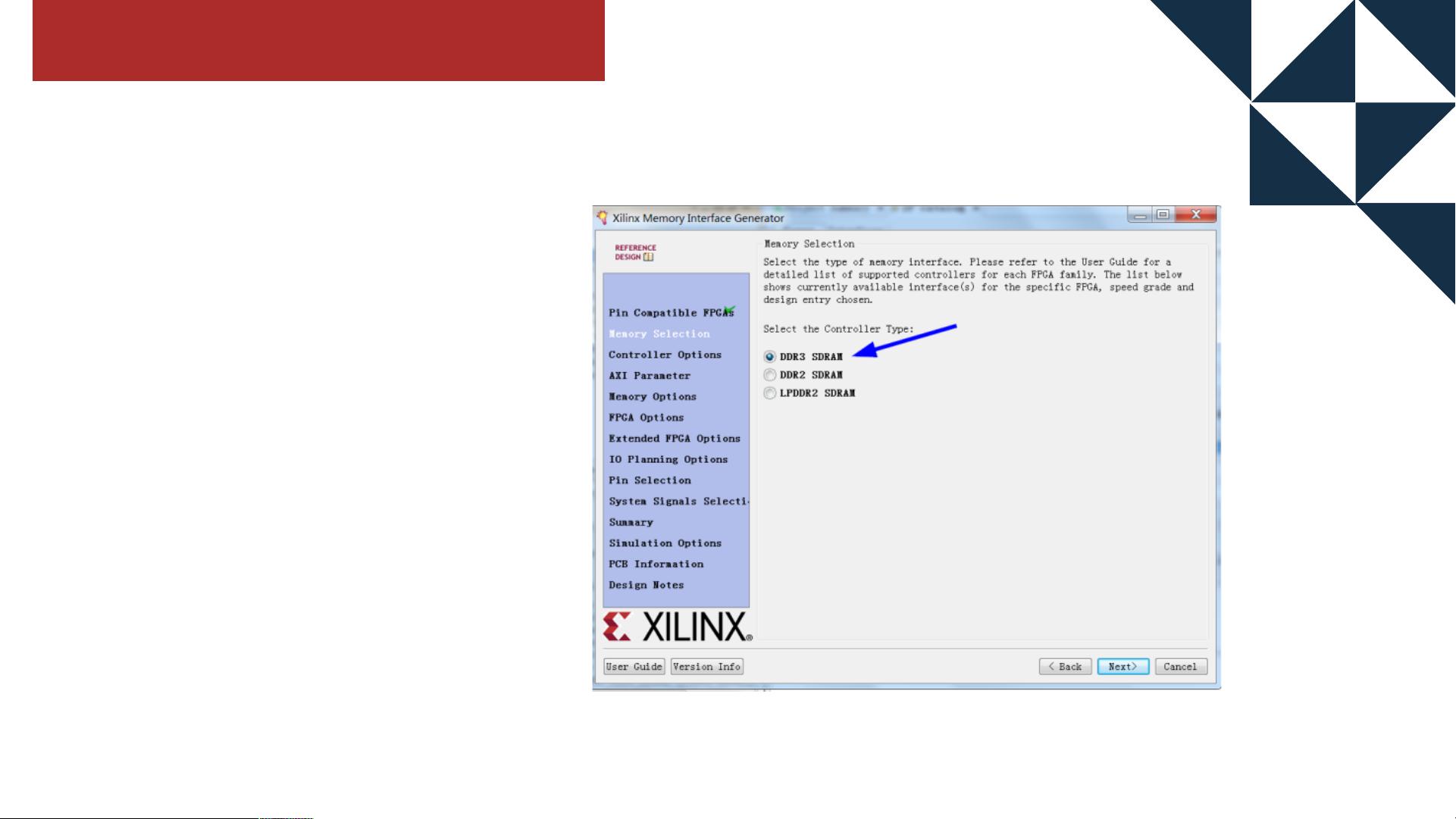

DDR3 IP核是FPGA设计中用于控制DDR3内存的关键组件。在Xilinx FPGA设计中,可以使用Memory Interface Generator (MIG)工具来配置DDR3 IP核。首先,在FlowNavigator面板的Project Manager下打开IP Catalog,找到并双击MemoryInterfaceGenerator(MIG7Series) IP核。MIG会自动匹配设计中使用的FPGA型号、速度等级、综合工具和设计输入语言。在配置过程中,应确保正确设置器件家族、器件型号和速度等级,同时在Output Options页面选择“Create Design”,为IP核指定一个合适的组件名称,如“mig_7series_0”,并设置控制器的数量。

2. DDR3 IP核配置的详细参数:

在Options for Controller0页面,需要设置关键参数,如DDR3存储器驱动的时钟周期,通常设置为2500ps(400MHz),内存型号如MT41K128M16XX-15E,这是一款常见的DDR3 SDRAM芯片,其接口电压为1.5V。这些参数的精确设置对于保证DDR3内存与FPGA之间的正确通信至关重要。

3. 基于在线逻辑分析仪调试DDR3数据读写:

在实际系统中,为了确保DDR3内存的正确工作,通常会使用在线逻辑分析仪进行数据读写的调试。这一步骤可以帮助开发者检测和分析DDR3的数据传输,包括地址、命令和数据线上的信号,以验证时序是否符合DDR3标准,及时发现并解决问题。

4. 基于UART命令的DDR3批量数据读写:

通过UART(通用异步收发传输器)接口,可以实现对DDR3内存的远程控制和批量数据操作。这种方式常用于嵌入式系统中,允许系统主机通过串行通信接口向DDR3发送读写命令,实现灵活的数据管理。

DDR3内存的实例应用涵盖了从IP核配置、仿真到实际系统的调试与控制,这些步骤都是确保系统性能和稳定性的重要环节。理解并掌握这些知识点,对于设计和优化包含DDR3内存的FPGA系统具有重要意义。

2021-11-11 上传

2301_79436204

- 粉丝: 0

- 资源: 85

最新资源

- JavaScript实现的高效pomodoro时钟教程

- CMake 3.25.3版本发布:程序员必备构建工具

- 直流无刷电机控制技术项目源码集合

- Ak Kamal电子安全客户端加载器-CRX插件介绍

- 揭露流氓软件:月息背后的秘密

- 京东自动抢购茅台脚本指南:如何设置eid与fp参数

- 动态格式化Matlab轴刻度标签 - ticklabelformat实用教程

- DSTUHack2021后端接口与Go语言实现解析

- CMake 3.25.2版本Linux软件包发布

- Node.js网络数据抓取技术深入解析

- QRSorteios-crx扩展:优化税务文件扫描流程

- 掌握JavaScript中的算法技巧

- Rails+React打造MF员工租房解决方案

- Utsanjan:自学成才的UI/UX设计师与技术博客作者

- CMake 3.25.2版本发布,支持Windows x86_64架构

- AR_RENTAL平台:HTML技术在增强现实领域的应用