DDR2 PCB布局指南:关键规则与信号组分析

需积分: 9 84 浏览量

更新于2024-07-25

收藏 783KB PDF 举报

"DDR2的PCB布线规则主要涉及DDR技术的发展阶段、DDR2的主导地位、DDR2布局设计的关键点以及Micro和Freescale的设计指南。在DDR2的PCB布局中,理解信号组的分类、电源分配、PCB叠层设计以及阻抗控制是非常重要的。"

DDR2的PCB布线规则详细说明如下:

1. **DDR技术的演变**:从SDRAM到DDR,再到DDR2和DDR3,内存技术不断演进。DDR2在当前应用中占据主导地位,但随着技术发展,DDR3逐渐成为主流。不同代的DDR内存主要区别在于内部预存取技术,但外部接口速率基本相似。

2. **信号速率理解**:DDR的时钟频率(clock)与数据传输速率(data)是相关的,例如,时钟频率为266MHz时,数据传输速率也是266MHz,因为一个完整周期包含'0'和'1',所以BitRate为533MHz。

3. **信号组分类**:

- 数字信号组:包括DQ、DQS和DM,每个字节为一个Lane组,如DQ0~DQ7、DQS0和DM0。

- 地址信号组:ADDRESS,包含所有地址线。

- 命令信号组:CAS#、RAS#、WE#,分别对应列地址选择、行地址选择和写使能。

- 控制信号组:CS#(片选)、CKE(时钟使能)。

- 时钟信号组:CK和CK#,为DDR工作提供同步时钟。

4. **电源与接地**:Micro公司的建议中,VSS为数字地,VSSQ为信号地,通常视为等效。VDD是核心电源,VDDDQ用于DQ和I/O供电,也视为等效。

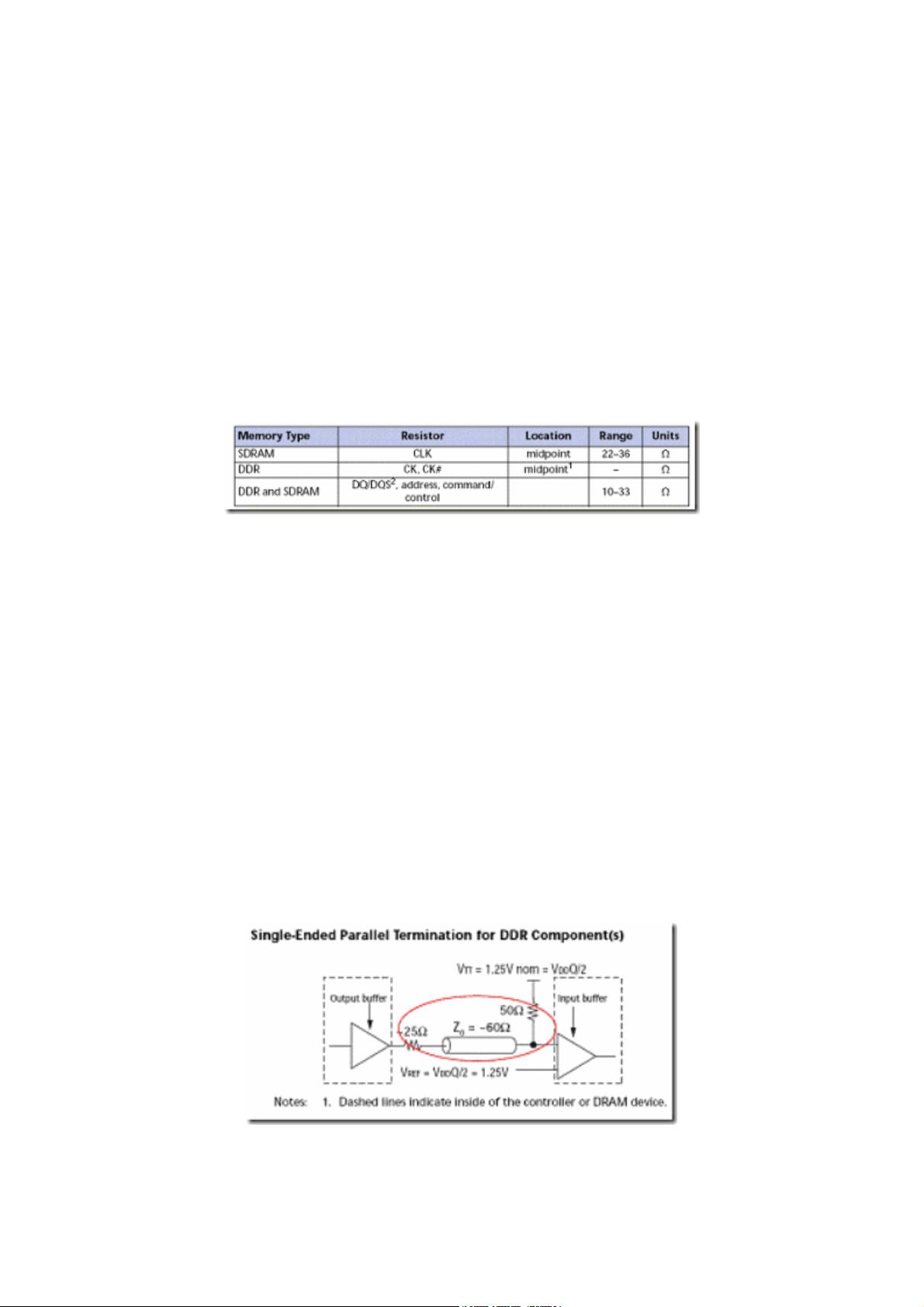

5. **PCB叠层设计**:推荐使用6层PCB,具体分布未详述,但通常会包括电源层、地层和信号层。PCB的阻抗控制在50~60欧姆,以确保信号质量。

6. **阻抗匹配**:确保信号线的阻抗匹配至关重要,以减少反射和信号损失,提高数据传输的准确性。

7. **配合文档**:文章内容与lql-003-DDRDesignerChecklist.doc配合使用,提供完整的DDR设计原则。

DDR2的PCB布线规则是基于信号的分类、电源分配、地线处理、PCB叠层设计以及阻抗控制等多方面的综合考虑,以确保高速内存系统的稳定性和可靠性。正确遵循这些规则能够有效防止信号干扰,提高系统性能。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2013-08-13 上传

2022-04-19 上传

2012-08-22 上传

2014-06-04 上传

2011-08-16 上传

shixiaoqiang520

- 粉丝: 0

- 资源: 2

最新资源

- Excel-VBA实用技巧范例-利用VBA标准功能操作文件.zip

- 施工管理资料表格-060501_成套电柜、控制柜(屏、台)和动力、照明配电箱(盘)安装检验批质量验收记录表

- BPMNspector-fixSeqFlow:修复 BPMN 模型中的序列流问题

- 离散控制Matlab代码-ihss:不精确的等级量表分离

- 基于EKF扩展卡尔曼滤波的GPS信号数据跟踪matlab仿真+代码操作视频

- CC3200 智能插头能量测量和控制解决方案-电路方案

- ant-design-vue-4.0.0-beta.2.zip

- Excel-VBA实用技巧范例-设定工作簿基本信息.zip

- A2_smvs.zip

- Mixtape:我的混音带项目

- 水利水电施工组织设计-沪崇苏立交桥梁全套施工组织设计

- vb坐标 转换 七参数 四参数

- Camel-CXF-CXFRS-Demo

- 离散控制Matlab代码-cic:Athey和Imbens(2006)变化中变化模型的Stata实施

- 任务管理器屏蔽映像名称易语言源码

- 快递物流app ui .ai素材下载