74HC138译码器详解:功能、特性与应用

需积分: 33 47 浏览量

更新于2024-09-15

收藏 205KB DOC 举报

"这篇文档主要介绍了74HC138这款高速CMOS译码器的详细信息,包括其功能、参数、特性和应用。"

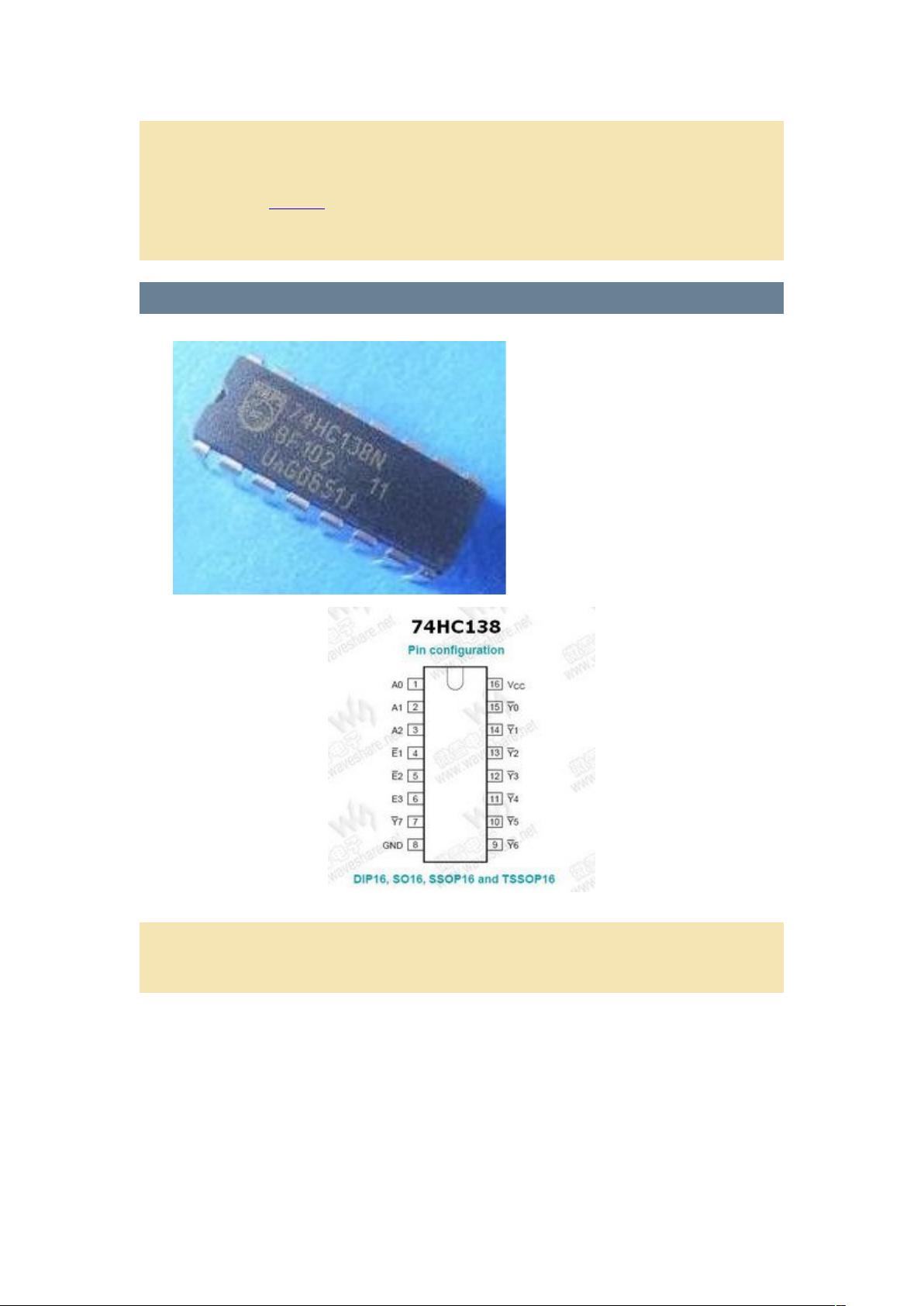

74HC138是一款广泛应用于硬件开发中的3线-8线译码器,适用于高速电路环境。它具有3个二进制加权地址输入(A0, A1, A3),在使能状态下,能够根据这些输入的组合生成8个互斥的低电平有效输出(Y0至Y7)。74HC138的独特之处在于它有3个使能输入端——E1、E2和E3。正常工作时,E1和E2需要置低,E3需要置高,否则所有输出都将保持高位状态。这种复合使能设计使得74HC138易于扩展,只需4片芯片加上1个反相器,就可以构建一个1-32线的译码器。

此外,74HC138还可以作为8输出的多路分配器使用。如果选择一个低有效使能输入作为数据输入,而其他使能输入作为选通信号,即可实现此功能。不过,未使用的使能输入端必须保持在正确状态,即低有效或高有效,以避免对输出造成影响。

74HC138的工作电压范围为2.0V到6.0V,具有正向驱动电流能力,典型值为+/-5.2mA,并具有12ns的传输延迟时间(在5V电压下)。这款芯片采用CMOS技术,适合低功耗或电池供电的应用。它具有反相输出特性,与74HC238逻辑功能相同,但输出极性相反。74HC138符合JEDEC标准no.7A,是存储器芯片译码选择的常见选项,且具有低有效互斥输出、ESD保护等特点,符合HBMEIA/JESD22-A114-C和MMEIA/JESD22-A115-A的静电放电防护标准。该芯片的封装形式多样,包括SO16, SSOP16, DIP16, 和 TSSOP16。

同时,文档中还提到了74HC165,这是一款高速CMOS器件,与74HC138类似,遵循JED标准,但其具体功能和特性在当前摘要中并未详细展开。74HC165通常用于串行到并行转换,例如在数据采集系统或长数据线的处理中。

74HC138在电子设计中扮演着重要的角色,特别是在数字逻辑系统和微处理器系统中,它可以用来解码地址线,选择特定的设备或内存位置。其多路分配功能和灵活的使能输入设计,使得它在各种应用场合都能表现出色。在进行硬件设计时,了解并掌握74HC138的特性与操作方法是至关重要的。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2023-06-09 上传

2023-06-01 上传

2019-05-06 上传

2013-02-17 上传

2020-04-22 上传

江海汇

- 粉丝: 10

- 资源: 12

最新资源

- [计算机科学经典著作].Addison.Wesley.Bjarne.Stroustrup.The.C++.Programming.Language.Third.Edition.pdf

- [计算机科学经典著作].Addison.Wesley.Bjarne.Stroustrup.The.C++.Programming.Language.Special.Edition.pdf

- 关于C #委托的讲解(很不错哦)

- DHT的P2P搜索定位技术研究.pdf

- 数据挖掘概念与技术 韩家伟.pdf

- ajaxpdf电子书

- JavaScript规范 ECMA266

- 商业企业进销存管理软件系统需求

- 不要问了网络连接手机接入点

- 基于事件驱动的无线传感器网络动态分簇路由协议

- J2ME GAMING中文版

- The Personal Software ProcessSM (PSPSM) Body of Knowledge, Version 2.0

- 数据库系统概论答案,所有的哦

- bbs系统设计文档(学习资料)

- MS OFFICE EXCLE VBA使用技巧

- rfc4566 SDP(Session Description Protocol0