"基于CMOS工艺的触发器设计与Hspice仿真分析"

需积分: 0 81 浏览量

更新于2023-12-28

12

收藏 933KB DOC 举报

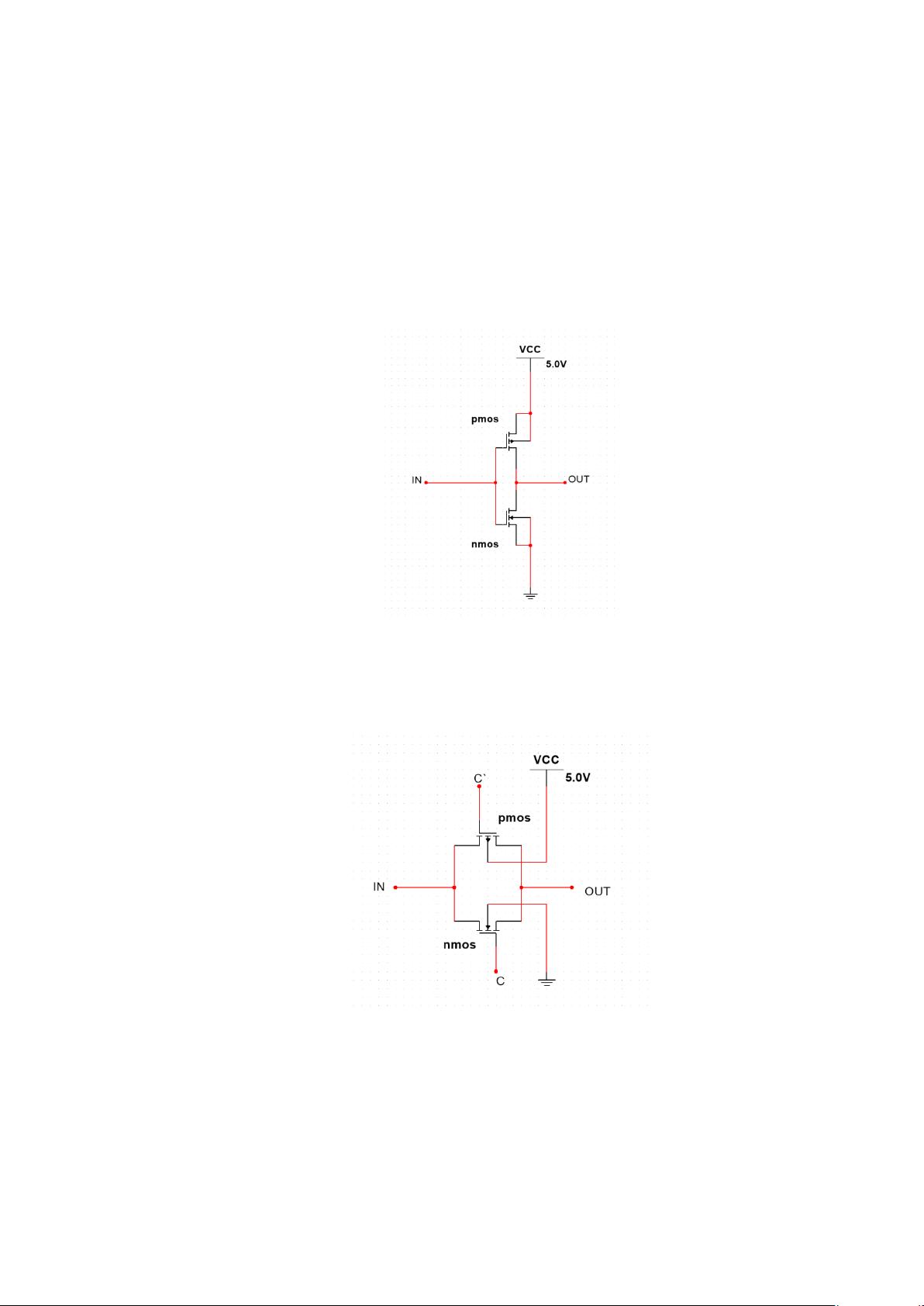

本次集成电路课程设计报告基于半导体集成电路和数字电路等课程的知识,利用Hspice软件完成了CMOS工艺触发器的设计。通过该课程设计,我们熟悉并掌握了集成电路芯片电路设计及模拟的方法和技巧。具体来说,设计了用传输门构成的电平触发D触发器和图2所示的边沿触发器,并进行了详细的电路原理分析。在编写Hspice网表文件时,我们采用了32nm的工艺,并进行了瞬态波形仿真分析以进行功能验证。随后,我们改变了负载,并进行了瞬态波形模拟,进行性能分析。在测量电路的功耗和延时方面,我们进行了性能分析,并尝试改变管子的尺寸(W或L),再次进行了瞬态波形、负载能力和功耗延时的仿真。通过这些实际的设计和仿真操作,我们成功地掌握了集成电路的设计和模拟方法。

在设计思路和方案部分,我们首先介绍了触发器的基本原理和特点,然后详细讲解了CMOS构成的非门和传输门,接着分别介绍了电平D触发器和边沿触发器的设计方法。针对各种电路的设计,我们进一步编写了Hspice的网表文件,包括传输门、非门和电平D触发器等部分,并对这些电路进行了详细的说明和分析。通过这些分析,我们深入理解了不同类型触发器的设计原理和仿真方法,同时也巩固了对CMOS工艺的理解和应用。

在进行电路仿真分析时,我们首先验证了电平触发D触发器和边沿触发器的功能,通过瞬态波形仿真进行了验证。这一步骤是非常重要的,因为它直接影响到电路的整体性能和稳定性。随后,我们通过改变负载进行了电路性能分析,观察并分析了在不同负载下的电路响应情况。通过这些仿真实验,我们深入了解了电路的性能特点和参数的变化规律,为进一步优化和改进电路性能提供了重要的数据和参考。

在测量电路的功耗和延时方面,我们通过仿真分析得出了电路的实际功耗和延时,并对这些数据进行了分析和比较。在性能分析的过程中,我们不断改进和优化了电路的设计和参数,以提高电路的整体性能和稳定性。在改变管子尺寸的仿真实验中,我们通过不同的管子尺寸(W或L)进行了瞬态波形、负载能力和功耗延时的仿真,以评估不同参数对电路性能的影响并优化电路设计。通过这些多方面的实验和仿真,我们深入研究了不同参数对电路性能的影响规律,并进一步掌握了集成电路设计和性能优化的方法和技巧。

通过本次集成电路课程设计,我们不仅深入学习了集成电路和CMOS工艺的知识,还在Hspice软件的实际操作中获得了丰富的经验。通过分析和仿真不同类型触发器的设计和性能,我们进一步夯实了集成电路设计和模拟的理论基础,并提高了实际操作的能力。最后,我们对课程设计中的成果和经验进行了总结和归纳,进一步深化了对集成电路设计和仿真的理解。通过本次课程设计,我们在集成电路领域迈出了重要的一步,为今后的学习和研究打下了坚实的基础。

点击了解资源详情

900 浏览量

171 浏览量

141 浏览量

141 浏览量

131 浏览量

216 浏览量

104 浏览量

140 浏览量

Heart.f

- 粉丝: 2

最新资源

- 掌握PerfView:高效配置.NET程序性能数据

- SQL2000与Delphi结合的超市管理系统设计

- 冲压模具设计的高效拉伸计算器软件介绍

- jQuery文字图片滚动插件:单行多行及按钮控制

- 最新C++参考手册:包含C++11标准新增内容

- 实现Android嵌套倒计时及活动启动教程

- TMS320F2837xD DSP技术手册详解

- 嵌入式系统实验入门:掌握VxWorks及通信程序设计

- Magento支付宝接口使用教程

- GOIT MARKUP HW-06 项目文件综述

- 全面掌握JBossESB组件与配置教程

- 古风水墨风艾灸养生响应式网站模板

- 讯飞SDK中的音频增益调整方法与实践

- 银联加密解密工具集 - Des算法与Bitmap查看器

- 全面解读OA系统源码中的权限管理与人员管理技术

- PHP HTTP扩展1.7.0版本发布,支持PHP5.3环境

已收录资源合集

已收录资源合集