JESD204 PHY v4.0 www.xilinx.com 14

PG198 October 4, 2017

Chapter 2: Product Specification

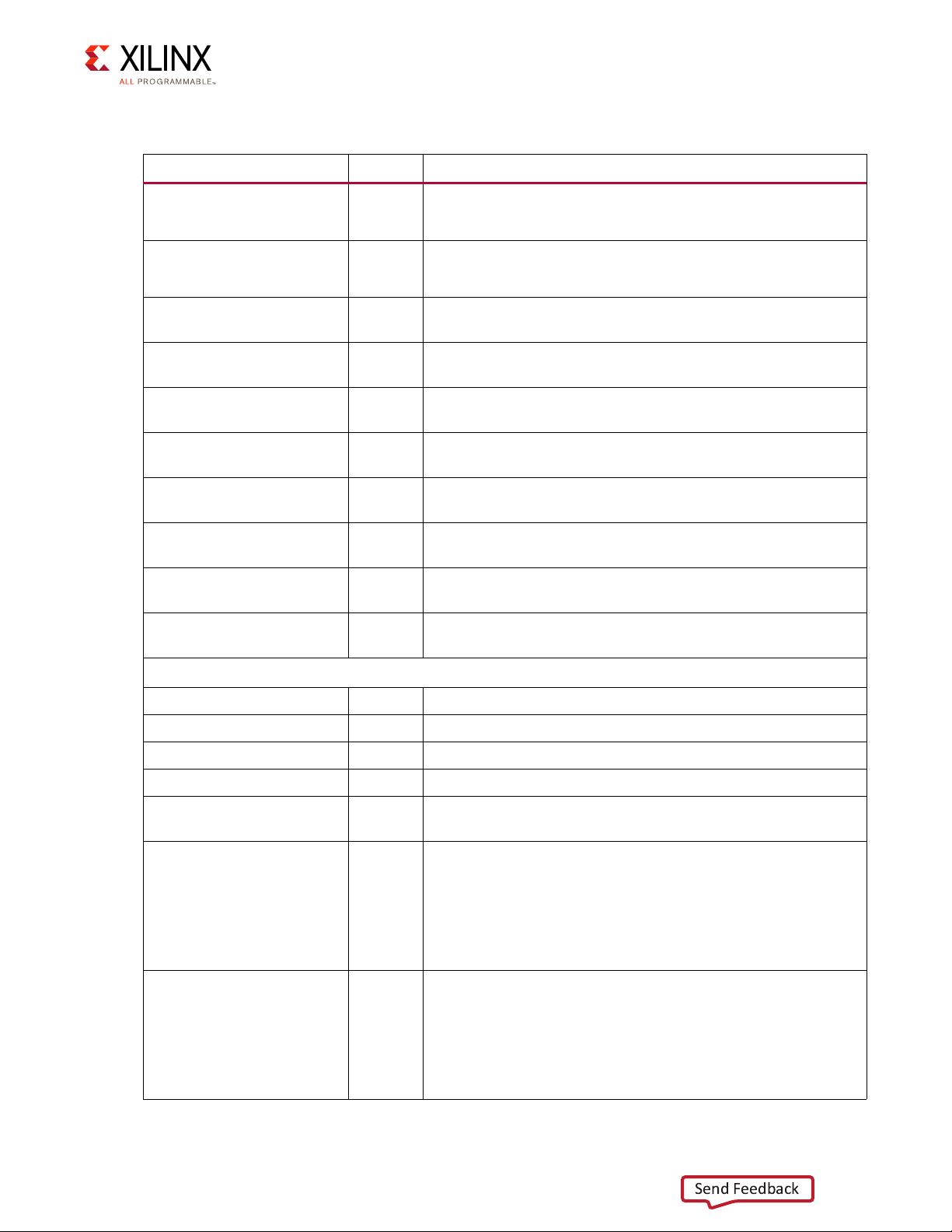

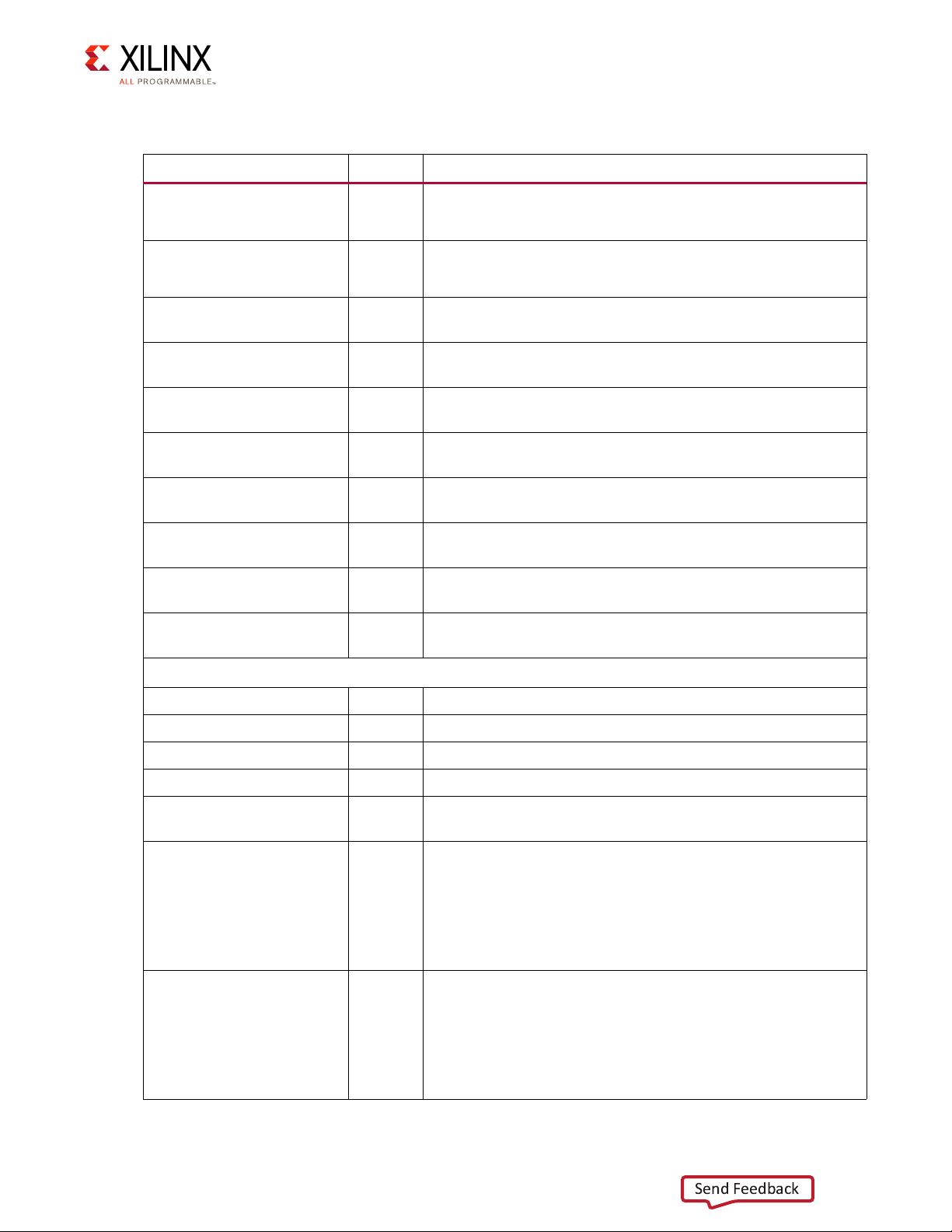

commonM_qpll_clk_in

In

Clock input for the QPLL (Quad M). Always present.

Note: This port is only applicable to 7-Series devices.

commonM_qpll_refclk_in

In

Reference clock input for the QPLL (Quad M). Always present.

Note: This port is only applicable to 7-Series devices.

commonM_pll0_clk_in

In

Reference clock input for the PLL (Quad M). Only present when

PLL0 is selected.

commonM_pll0_refclk_in

In

Clock input for the PLL (Quad M). Only present when PLL0 is

selected.

commonM_pll1_clk_in

In

Clock input for the PLL (Quad M). Only present when PLL0 is

selected.

commonM_pll1_refclk_in

In

Reference clock input for the PLL (Quad M). Only present when

PLL1 is selected.

commonM_qpll0_clk_in

In

Clock input for the QPLL (Quad M). Only present when QPLL0

is selected.

commonM_qpll0_refclk_in

In

Reference clock input for the QPLL (Quad M). Only present

when QPLL0 is selected.

commonM_qpll1_clk_in

In

Clock input for the QPLL (Quad M). Only present when QPLL1

is selected.

commonM_qpll1_refclk_in

In

Reference clock input for the QPLL (Quad M). Only present

when QPLL1 is selected.

Resets

tx_reset_gt

In

Tx channel datapath asynchronous logic reset.

rx_reset_gt

In

Rx channel datapath asynchronous logic reset.

tx_sys_reset

In

Tx channel datapath and PLL asynchronous logic reset.

rx_sys_reset

In

Rx channel datapath and PLL asynchronous logic reset.

qpll_reset_out

Out

Reset output from transceiver logic to reset Common Block.

Present only when QPLL selected.

qpll0_reset_out

Out

Reset output from transceiver logic to reset QPLL0 Common

Block when QPLL0 is selected or the AXI-4 Lite Management

Interface is enabled and at least one channel is using either

QPLL0 or QLL1.

Note: This port is only applicable to UltraScale and

UltraScale+ devices.

qpll1_reset_out

Out

Reset output from transceiver logic to reset QPLL1 Common

Block when QPLL1 is selected or the AXI-4 Lite Management

Interface is enabled and at least one channel is using either

QPLL0 or QLL1.

Note: This port is only applicable to UltraScale and

UltraScale+ devices.

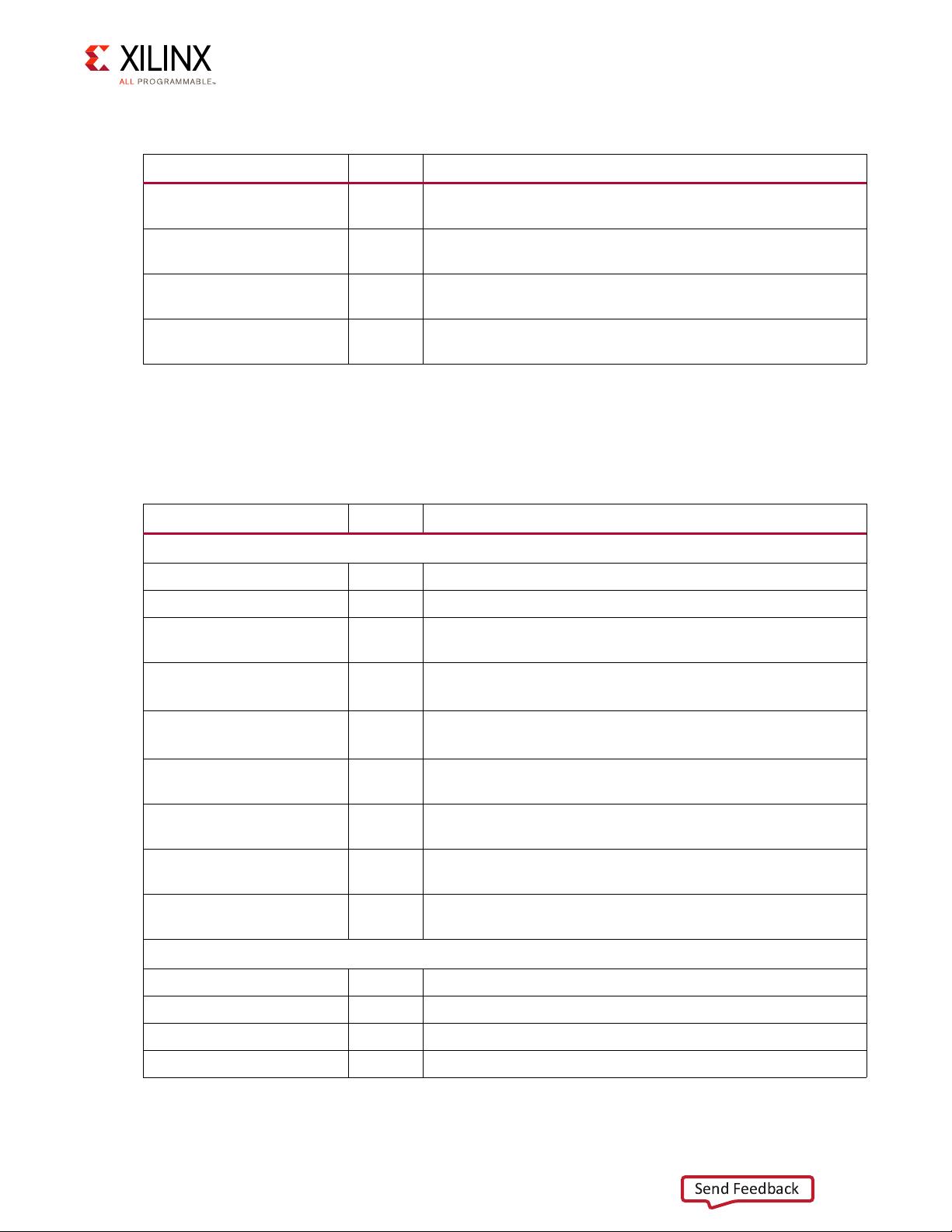

Table 2‐3: Common Clock and Reset Ports for JESD204B Configurations (Shared Logic in

Example Design)

Signal Name Direction Description