FPGA实现BP神经网络图像压缩:并行乘累加单元设计

182 浏览量

更新于2024-08-30

收藏 277KB PDF 举报

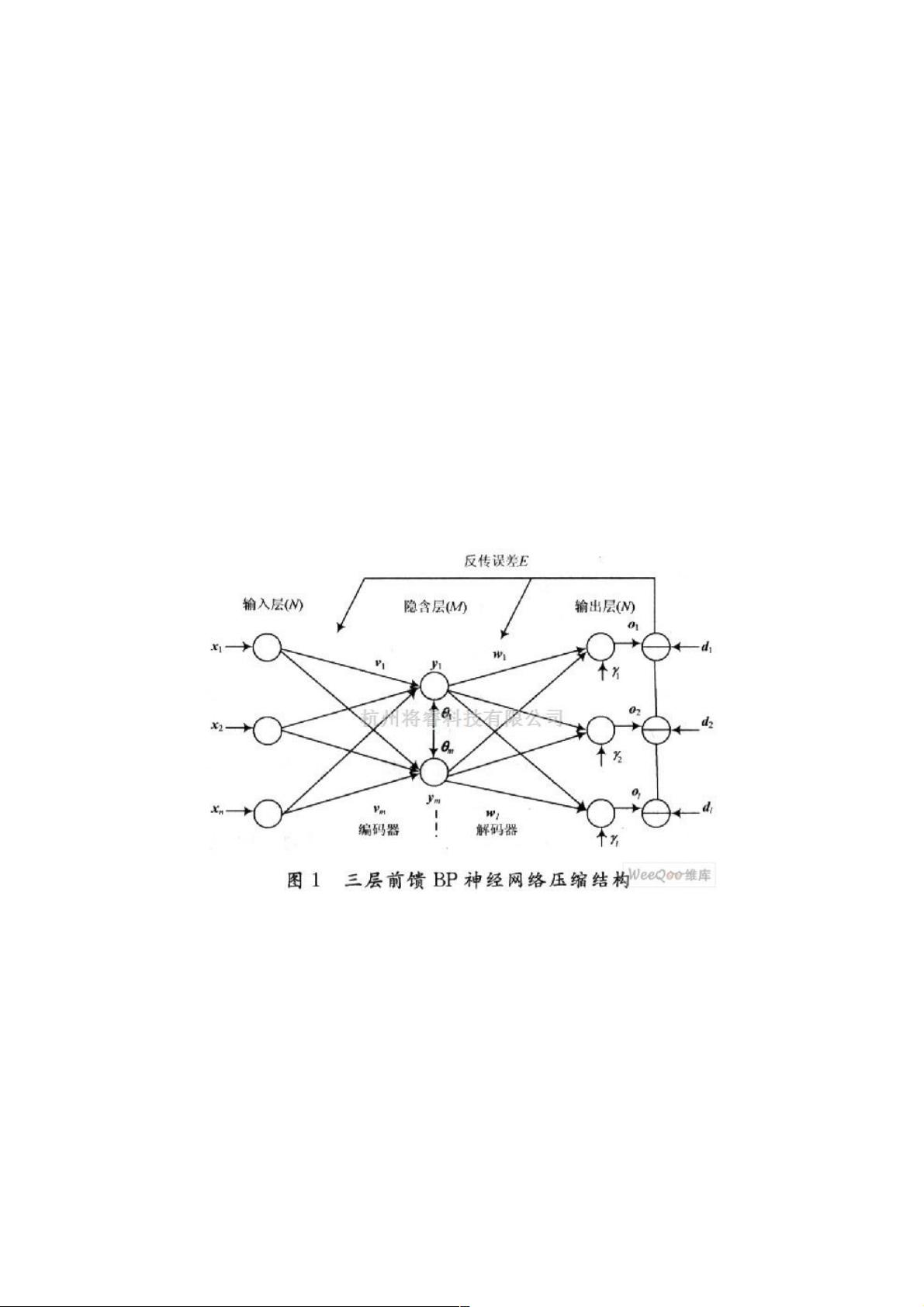

本文主要探讨了在EDA/PLD(电子设计自动化/可编程逻辑器件)环境中,利用BP(误差反向传播)神经网络进行图像压缩算法的设计,特别是关注其中的乘累加单元在FPGA(现场可编程门阵列)平台上的实现。神经网络,尤其是多层前馈BP神经网络,因其强大的信息处理能力和自适应学习特性,被广泛应用在图像压缩领域。

在图像压缩中,BP神经网络的优势显著。首先,它具备巨量并行处理的能力,可以同时处理大量像素,提高了压缩效率。其次,神经网络的信息处理和存储功能整合,减少了中间数据的存储需求,节约了存储空间。自组织自学习功能使得网络能够在训练过程中不断优化自身参数,适应不同的图像特征,从而达到更好的压缩效果。

相比之下,传统的数字信号处理器(DSP)如固定结构的指令执行方式,其资源利用率低,难以满足神经网络的并行计算需求。而FPGA则提供了灵活的硬件架构设计,能够根据实际应用调整数据处理的位宽,实现真正的并行计算。随着FPGA技术的发展,其处理能力的增强使得在FPGA上实现高效且可扩展的BP神经网络图像压缩成为可能。

文章的核心部分着重讨论了如何将BP神经网络的算法转换为FPGA硬件实现,包括乘累加单元的设计与优化,以及如何在有限的硬件资源下实现高效的图像数据压缩。这包括了神经网络权重的存储、输入输出数据的处理流程、以及误差反向传播机制的硬件映射等关键步骤。此外,文中可能还会涉及FPGA设计工具的选择、布线策略、性能分析和优化等方面的内容。

总结来说,本文提供了一种将BP神经网络应用于图像压缩的FPGA设计方法,旨在提高压缩性能,降低硬件资源消耗,为实际的嵌入式或实时图像处理系统提供了有价值的设计参考。通过深入理解和利用FPGA的优势,可以推动EDA/PLD领域在图像压缩等领域的技术创新。

102 浏览量

115 浏览量

228 浏览量

228 浏览量

127 浏览量

152 浏览量

154 浏览量

169 浏览量

102 浏览量

weixin_38705252

- 粉丝: 6

最新资源

- MySQL C++库源代码详解与编译指南

- Android FoldableLayout展开动画效果学习指南

- C#中MessageBoxIndirect的使用教程与示例

- Java实现的企业内部QQ聊天系统解决方案

- 汉化版Dependency Walker 2.1.3790深度剖析PE模块依赖性

- 电极原生CocoaPod Spec容器发布者使用指南

- 洛天依官方MMD模型Ver1.1版本发布

- Delphi实现点对点UDP通讯技术实例解析

- 高效名片与资料管理查询小程序

- Oracle Tuxedo服务调用与数据封装开发指南

- 深入解析Java编码问题及解决方案

- Horspool字符串匹配技术的输入增强应用解析

- 上海交通大学ASP.NET程序设计教程源代码解析

- 轻松录制游戏与工作视频的LiveRecorder工具

- 全面了解Windows API的参考资料

- Android侧滑菜单实现与应用指南