时序逻辑电路设计:从N进制到M进制计数器转换

版权申诉

148 浏览量

更新于2024-07-03

收藏 3.49MB PPT 举报

"该资源是关于数字电子技术基础的第六章——时序逻辑电路的下半部分,主要讨论了如何设计和构建不同进制的计数器,包括如何使用已有的N进制芯片来组成M进制计数器,以及面对M>N和M<N的情况时的不同构造方法。"

在数字电子技术中,时序逻辑电路是一种重要的电路类型,它不仅存储当前状态,还根据输入信号和内部状态的变化来产生输出。本资料主要关注的是计数器的构建,特别是如何利用现有的N进制计数器实现M进制计数器。

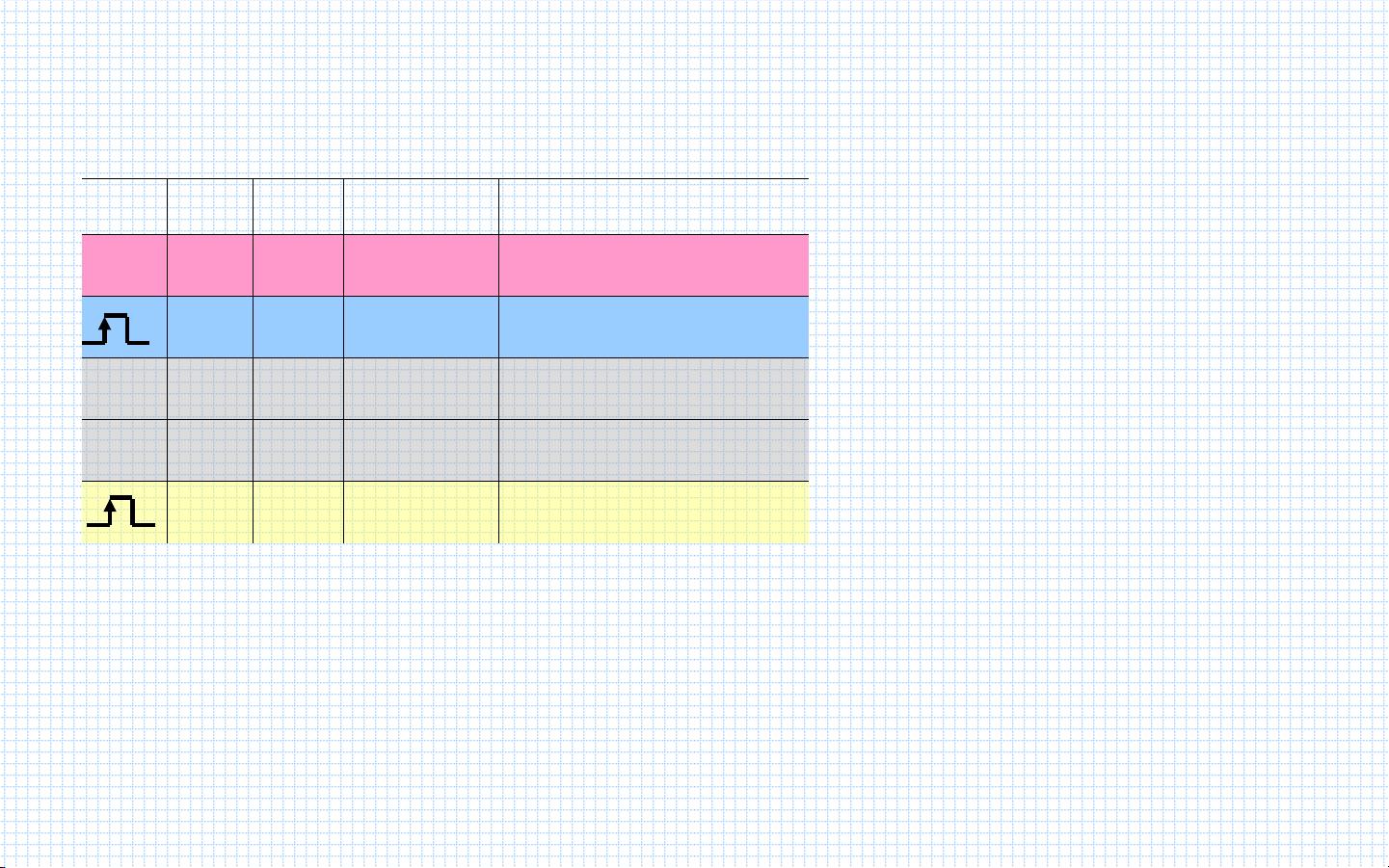

对于M<N的情况,即需要构建的计数器的进制比现有芯片的进制小,可以通过在计数循环中跳过N-M个状态来实现。有两种主要方法:置零法和置数法。置零法包括同步和异步两种方式,其中异步置零法通常在时钟脉冲作用时间较短时使用,而在计数过程中通过一个额外的信号强制所有计数状态清零。而置数法则是预先设定计数器到特定状态,例如可以设置为0000或1001等,使得计数器在新的循环中从这个预设状态开始。

当M>N时,即需要构建的计数器进制大于单个芯片的进制,有两种基本策略。一是将M分解为两个较小的因数N1和N2,分别构建N1和N2进制的计数器,然后通过串行或并行进位方式连接。串行进位方式是将低位计数器的进位输出作为高位计数器的时钟,而并行进位方式则使用同一时钟,低位计数器的进位输出作为高位计数器的计数控制信号。二是当M不能分解为较小的因数时,可以先用两个芯片组成N×N的计数器,再通过整体置零或置数的方法调整到所需的状态。

以74160这个十进制计数器为例,可以利用异步置零法将其改造成六进制计数器,也可以通过并行或串行进位方式将两片74160接成一百进制计数器。在实际应用中,选择哪种方法取决于系统需求和计数范围,以及对速度和复杂性的考虑。

总结来说,本资料深入探讨了时序逻辑电路中的计数器设计,涵盖了不同进制转换的技巧和策略,对于理解和设计数字电路系统具有很高的实用价值。理解这些内容对于电子工程师和相关领域的学生来说至关重要,因为它们是数字系统设计的基础,特别是在处理数据处理、定时和顺序控制等任务时。

2022-06-12 上传

2022-06-02 上传

2022-06-10 上传

wxg520cxl

- 粉丝: 25

- 资源: 3万+

最新资源

- 开源通讯录备份系统项目,易于复刻与扩展

- 探索NX二次开发:UF_DRF_ask_id_symbol_geometry函数详解

- Vuex使用教程:详细资料包解析与实践

- 汉印A300蓝牙打印机安卓App开发教程与资源

- kkFileView 4.4.0-beta版:Windows下的解压缩文件预览器

- ChatGPT对战Bard:一场AI的深度测评与比较

- 稳定版MySQL连接Java的驱动包MySQL Connector/J 5.1.38发布

- Zabbix监控系统离线安装包下载指南

- JavaScript Promise代码解析与应用

- 基于JAVA和SQL的离散数学题库管理系统开发与应用

- 竞赛项目申报系统:SpringBoot与Vue.js结合毕业设计

- JAVA+SQL打造离散数学题库管理系统:源代码与文档全览

- C#代码实现装箱与转换的详细解析

- 利用ChatGPT深入了解行业的快速方法论

- C语言链表操作实战解析与代码示例

- 大学生选修选课系统设计与实现:源码及数据库架构