"北京大学计算机系高级计算机系统结构:主存系统性能及优化"

需积分: 0 71 浏览量

更新于2024-01-14

收藏 5.34MB PDF 举报

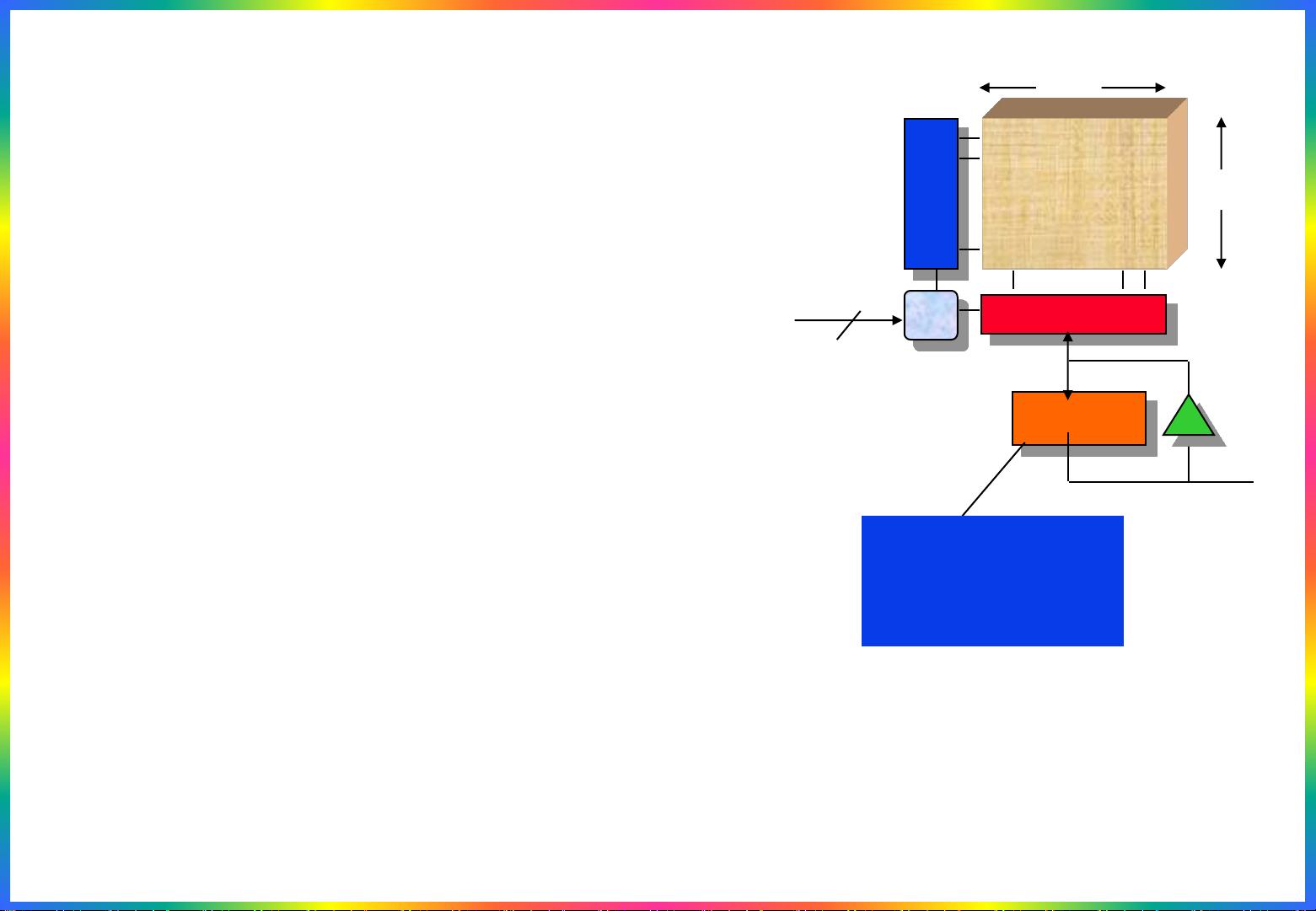

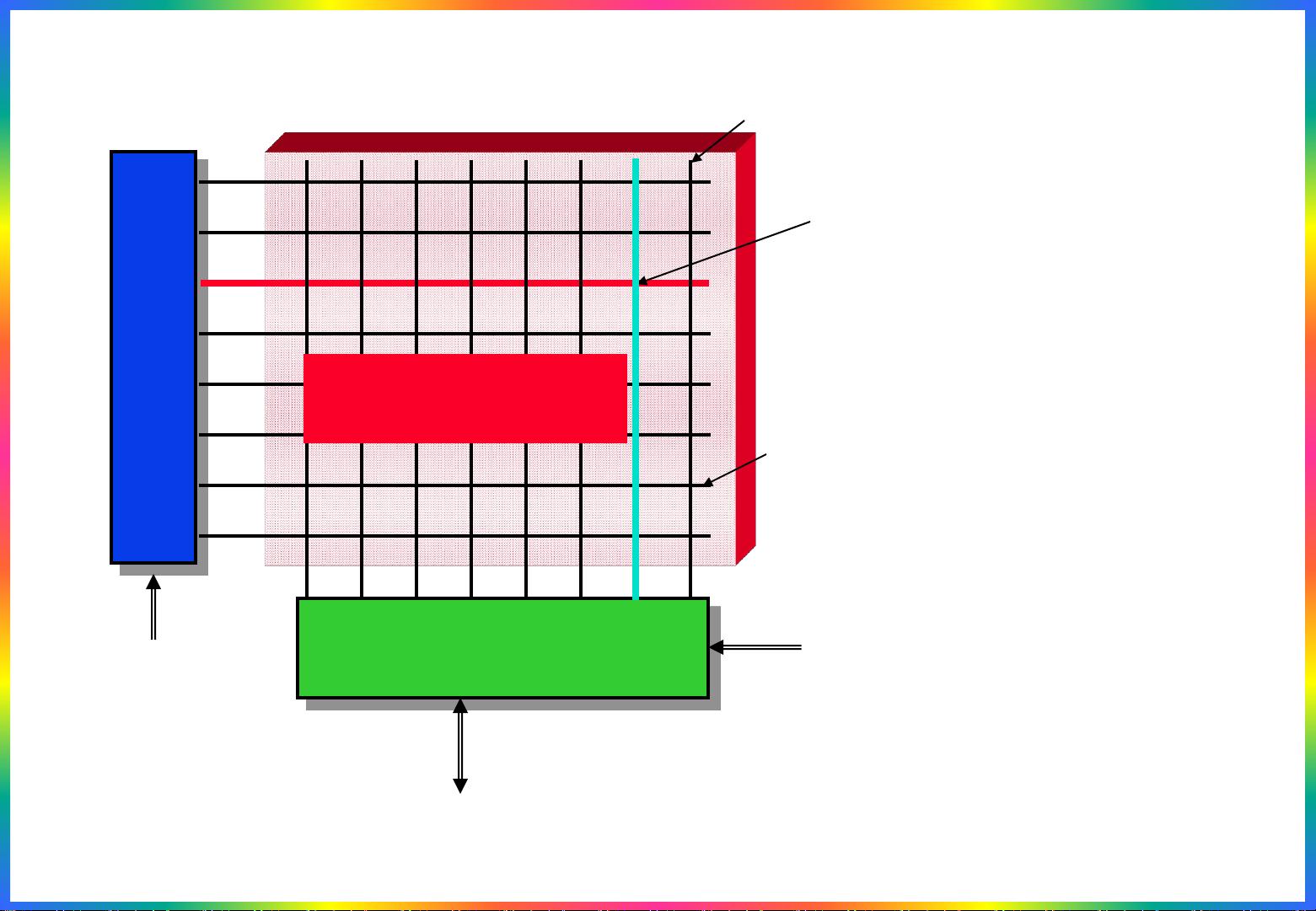

北大计算机系高级计算机系统结构课件chx14-arch08-mm1中提到了主存(DRAM)的延迟差距问题以及如何解决这个问题的方法。根据该课件,主存的延迟差距问题导致性能下降,因此需要采取一些措施来缓解这个问题。在这方面,处理器架构师采用了将快速缓存存储器(cache)放置在CPU和DRAM之间的方式,以建立一个称为“内存层次结构”的体系架构。

内存层次结构是一种将不同速度和容量的存储器层次化地组织起来的方式。在这个层次结构中,主存(DRAM)被放置在最底层,而位于CPU和主存之间的是一些速度更快但容量较小的缓存存储器。通过这种层次化的存储结构,可以提高系统的整体性能。

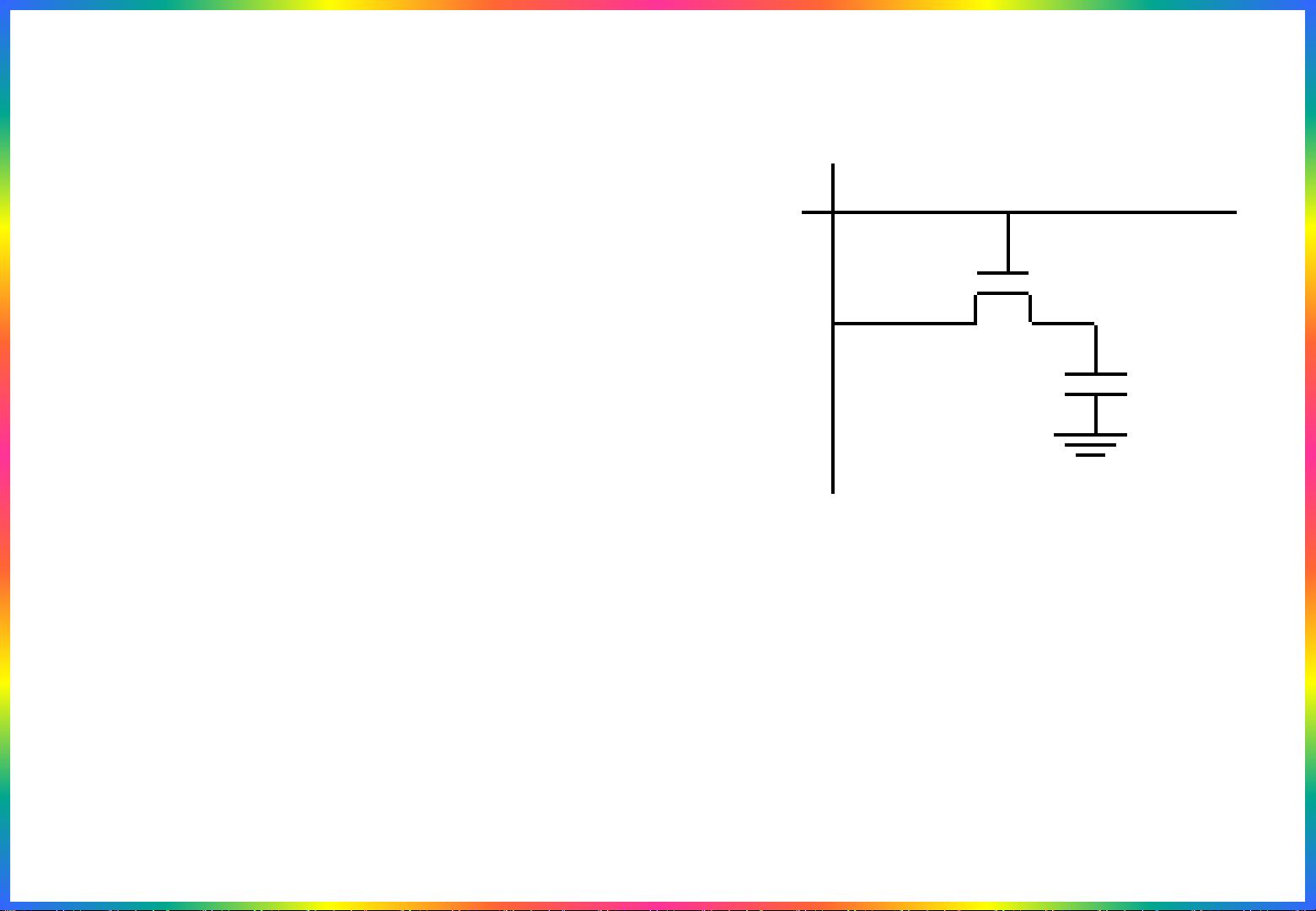

主要问题是如何在内存层次结构中管理数据的访问。访问内存的延迟主要与缓存未命中的惩罚时间(Cache Miss Penalty)有关。当CPU需要访问一个地址而该地址在缓存中没有找到时,就会发生缓存未命中。为了处理这个问题,系统需要从主存中将数据调入缓存,以便下次能够更快地访问。

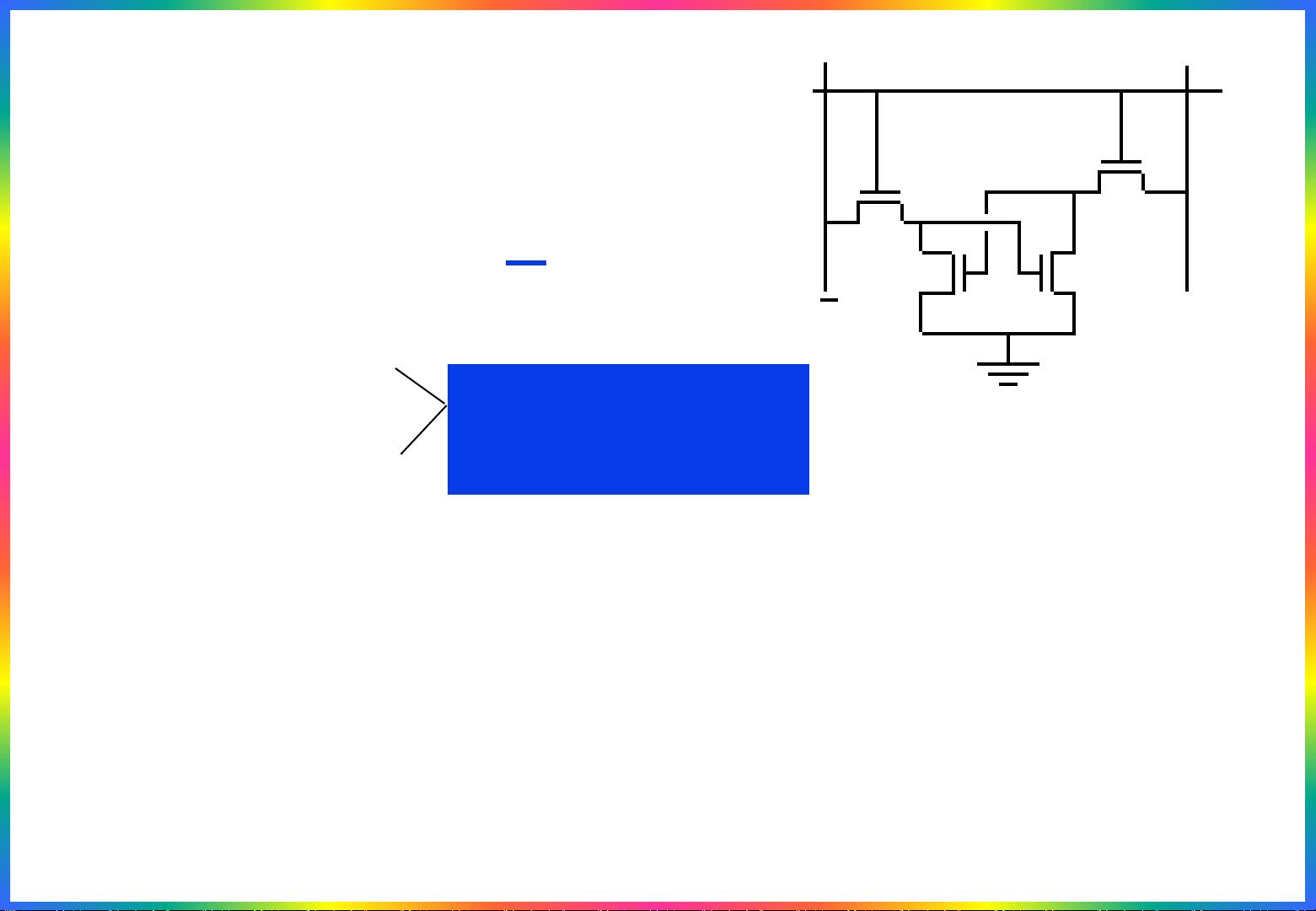

在具体的实现中,内存层次结构可以通过在CPU和主存之间插入多级的缓存来实现。每一级缓存的速度更快但容量较小,而它们之间通过一些特定的算法来控制数据的传输和管理。这些算法可以根据预取策略、替换策略和写回策略等不同的要求进行优化。

此外,为了更好地提高内存层次结构的性能,还可以通过设计和选择合适的内存控制器来减小延迟。内存控制器负责控制数据在内存和缓存之间的传输,在传输过程中需要考虑数据的一致性和有效性。

总的来说,通过构建内存层次结构,可以有效地解决主存(DRAM)延迟差距问题,提高系统的性能。然而,要实现一个高效的内存层次结构并不容易,需要考虑多种因素,如缓存替换策略、内存控制器设计以及预取算法等。随着技术的发展和需求的增加,内存层次结构的设计和优化也面临着新的挑战和机遇。因此,研究人员需要不断地深入研究这个领域,以提高计算机系统的性能和效率。

2022-08-03 上传

2022-08-03 上传

2022-08-04 上传

2024-10-02 上传

2023-07-14 上传

2023-07-08 上传

2023-05-29 上传

2023-08-17 上传

2023-05-25 上传

小明斗

- 粉丝: 41

- 资源: 329

最新资源

- Angular程序高效加载与展示海量Excel数据技巧

- Argos客户端开发流程及Vue配置指南

- 基于源码的PHP Webshell审查工具介绍

- Mina任务部署Rpush教程与实践指南

- 密歇根大学主题新标签页壁纸与多功能扩展

- Golang编程入门:基础代码学习教程

- Aplysia吸引子分析MATLAB代码套件解读

- 程序性竞争问题解决实践指南

- lyra: Rust语言实现的特征提取POC功能

- Chrome扩展:NBA全明星新标签壁纸

- 探索通用Lisp用户空间文件系统clufs_0.7

- dheap: Haxe实现的高效D-ary堆算法

- 利用BladeRF实现简易VNA频率响应分析工具

- 深度解析Amazon SQS在C#中的应用实践

- 正义联盟计划管理系统:udemy-heroes-demo-09

- JavaScript语法jsonpointer替代实现介绍