VerilogHDL入门指南:建模技巧揭秘

需积分: 10 110 浏览量

更新于2024-07-22

收藏 8.03MB PDF 举报

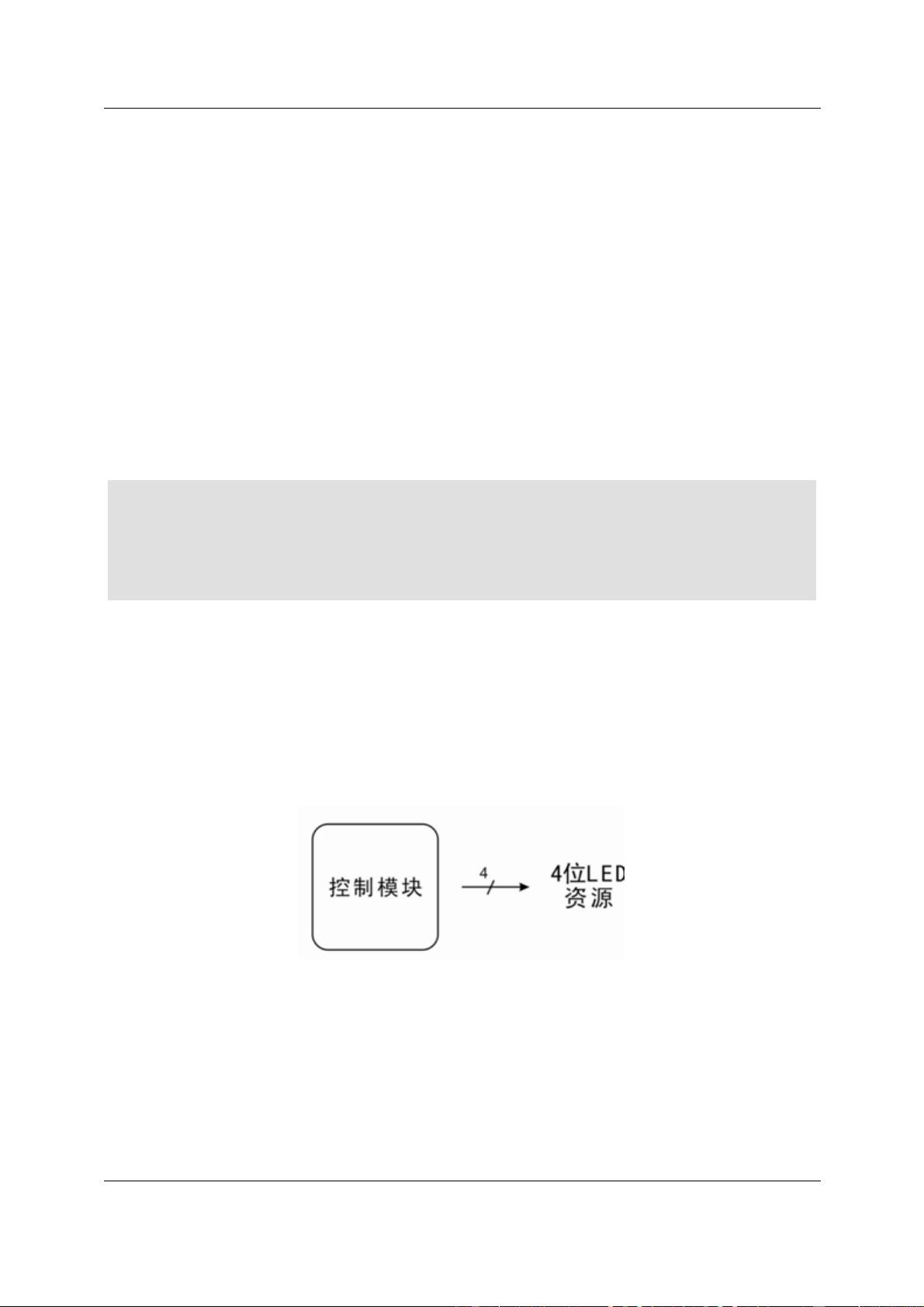

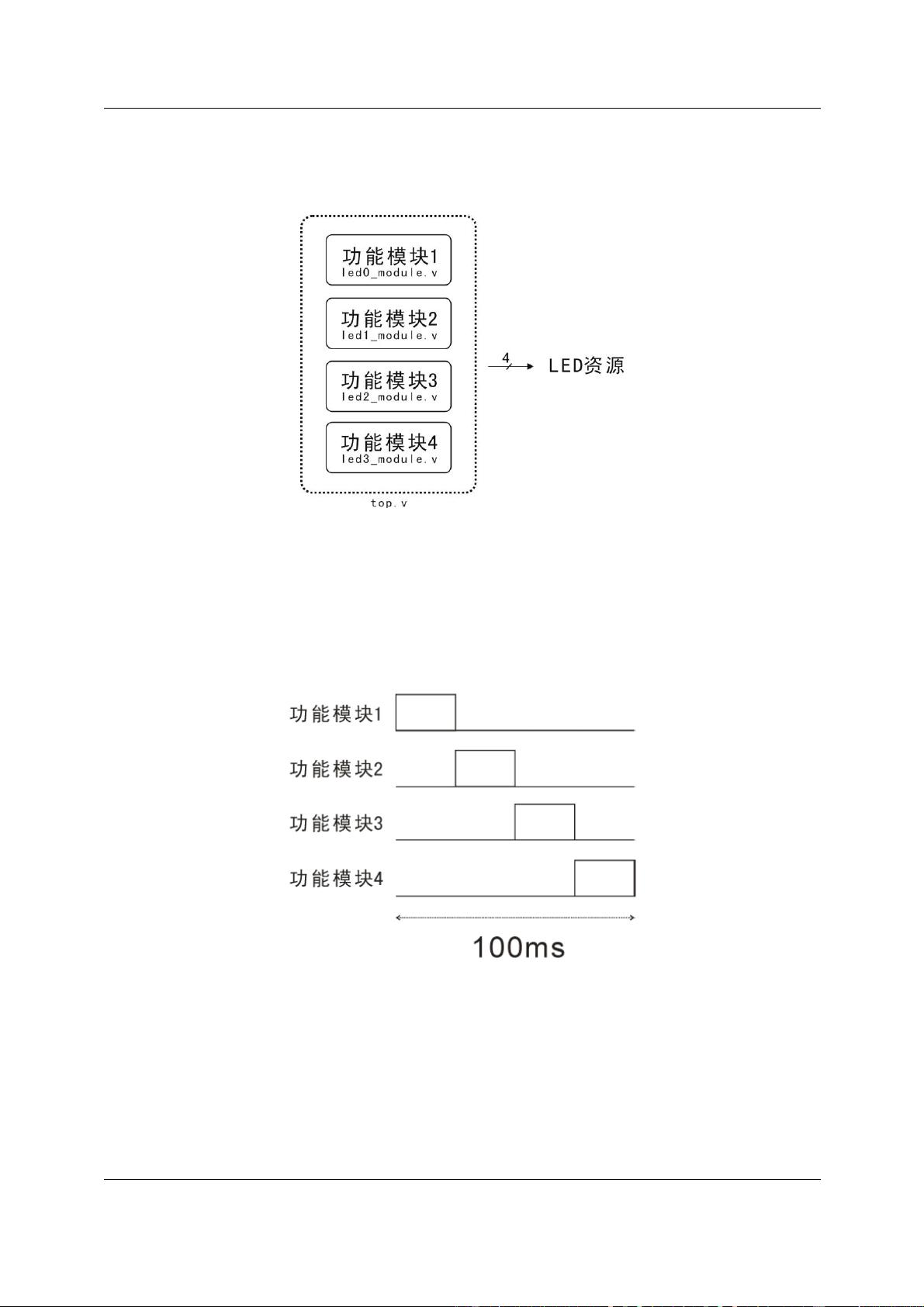

Verilog HDL是一种广泛应用于数字电路设计和FPGA开发的硬件描述语言。"Verilog HDL那些事儿_建模篇(for DB4CE15)"这本书旨在帮助初学者理解和掌握Verilog HDL的基本建模技巧,这是一个至关重要的基础概念。在FPGA设计中,模块化建模就像使用乐高积木一样,Verilog HDL充当了搭建和组织这些逻辑块的工具。然而,如果不了解建模策略和技巧,即使是高级语言也可能无法充分发挥其潜力。

建模并非简单的模块定义,而是需要对电路功能进行清晰、直观的抽象和组织。理解RTL(Register Transfer Level)设计,即从寄存器传输级别进行思考,是学习的关键。然而,仅仅参考他人的代码并不足以解决问题,除非你能完全理解他人设计的意图和实现方法。实际上,如果缺乏建模技巧,即使阅读再多的代码,也可能如同“半死不活的受折磨”,因为你可能只是在复制他人的工作,而非真正掌握设计过程。

这本书强调了建模技巧的重要性,因为它直接影响到代码的可读性、可维护性和效率。好的设计应该不仅让开发者自己能够轻松理解,也应使其他人能够快速跟进。作者倡导代码的表达力、整洁性和结构化,认为这在Verilog HDL中与时序分析和功能仿真同样重要,甚至更为关键。通过有效的建模,Verilog HDL的能力可以超越其他高级编程语言,特别是在表达复杂系统行为和优化资源利用方面。

对于初学者来说,之所以在学习Verilog HDL和FPGA时遇到困难,主要原因往往在于未能掌握良好的建模技巧。因此,这本教程致力于通过实例和深入讲解,帮助读者建立起坚实的建模基础,从而避免在学习过程中陷入困境,提升设计能力和自信心。

109 浏览量

点击了解资源详情

点击了解资源详情

点击了解资源详情

125 浏览量

163 浏览量

109 浏览量

630 浏览量

wangrui6268

- 粉丝: 0

最新资源

- 奥斯卡桂:Angular CLI 项目开发快速入门指南

- 芯片制造中倒装焊技术的设备与解决方案解析

- Go开发的cmus歌词查看器

- PracticalShootingSimulatorWindows隐私政策概述

- 企业数字神经网络系统:营销人员的学习利器

- Bo-Blog新年模板发布,独特设计引领网页潮流

- React项目迁移指南:Create React App快速入门

- Java源码实例:FontSelection功能实现与源码分析

- 企业战略实施与价值最大化指南

- 使用Go开发的Bladerunner实现远程SSH命令行自动化

- 验证通2010示例net版源代码深度解析

- Primefaces UI SNMP流量监控器部署于Wildfly容器

- Golang打造去中心化网络存档工具Hermes-Archiver

- 《公司用电组组长行为规范考评表》深度分析与应用指南

- 安卓应用开发:实现连续GPS定位绘制功能

- 化学机械抛光技术与SiO2抛光浆料研究新进展