FPGA实现的数控振荡器设计与应用

版权申诉

80 浏览量

更新于2024-08-04

收藏 216KB DOCX 举报

"本文主要探讨了基于FPGA的数控振荡器(NCO)的设计与实现,采用CORDIC算法实现正交数字混频器中的NCO,以提高频率分辨率和速度,适应高速数字通信的需求。文章介绍了CORDIC算法的原理,阐述了在FPGA中设计NCO的顶层电路结构,以及如何利用流水线技术优化设计。"

基于FPGA的数控振荡器设计是现代通信系统中的关键组成部分,特别是在软件无线电中,它们提供了灵活的频率合成和高精度的相位控制。数控振荡器的主要任务是生成正交的正弦和余弦样本,这对于正交数字混频器至关重要。传统的实现方式是通过查表法,即利用查找表(LUT)存储预计算的正余弦值,根据相位累加器的输出作为地址来获取相应的信号样本。然而,这种方法对于高分辨率和高速率的需求来说,既消耗大量的存储资源,又受限于外部RAM的读取速度。

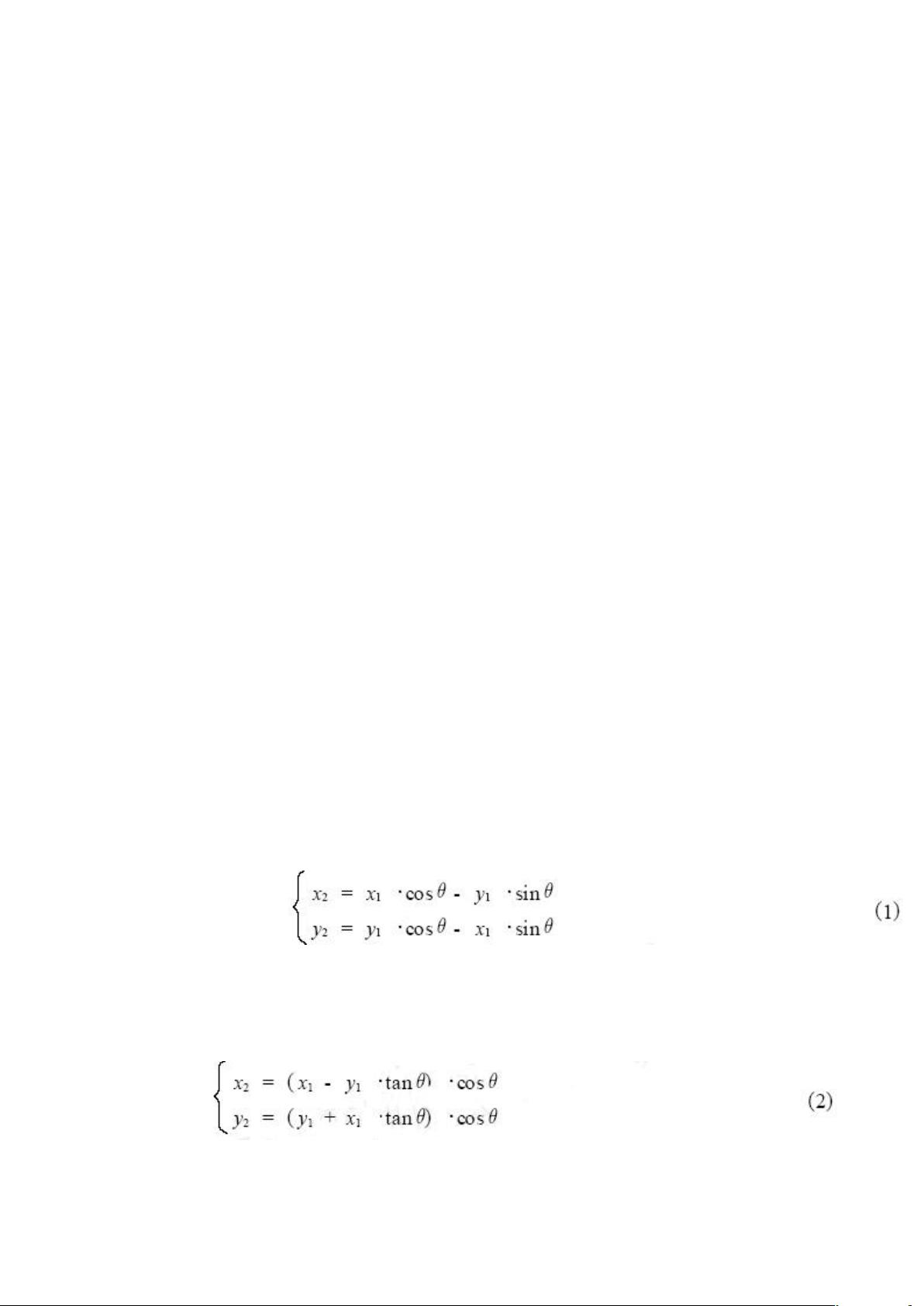

CORDIC(协调旋转数字计算机)算法提供了一种替代方案,它是一种迭代算法,用于计算复数的乘法、除法、反正切等运算,无需大规模存储器即可生成正弦和余弦信号。在NCO的应用中,CORDIC算法能够逐步调整相位,生成所需的正余弦样本。通过迭代,算法能够在每次步骤中对相位进行微小的旋转,从而实现高分辨率的频率合成。在FPGA实现中,可以将CORDIC算法与流水线结构相结合,以提高运算速度并减少延迟。

在FPGA设计中,顶层电路通常包括相位累加器、CORDIC算法单元以及可能的输出调理模块。相位累加器接收频率控制字,并根据该字累加生成当前相位。这个相位信息被输入到CORDIC算法单元,经过一系列迭代后产生正余弦样本。流水线技术的引入允许在不同的时钟周期内处理不同阶段的迭代,从而实现更高的输出速率。

文章还指出,为了优化NCO的性能,可以考虑使用固定点表示法来节省硬件资源,同时通过精细调整算法参数以确保输出信号的正交性和精度。在实际应用中,还需要考虑噪声和非理想因素的影响,例如量化噪声和器件非线性,这些都需要在设计过程中加以补偿或抑制。

基于FPGA的数控振荡器设计利用CORDIC算法能有效地解决高速、高精度需求,避免了大容量存储器的使用,降低了对外部RAM速度的依赖。这种实现方式为软件无线电和高速数字通信系统提供了高效、灵活的频率合成解决方案。

358 浏览量

点击了解资源详情

157 浏览量

2021-11-18 上传

2023-03-31 上传

129 浏览量

122 浏览量

2022-11-01 上传

2022-05-28 上传

南抖北快东卫

- 粉丝: 84

- 资源: 5586

最新资源

- npp_7.4.2_Installer.zip

- Mapquiz-Front

- 行业文档-设计装置-木丝水泥板为免脱模板的混凝土墙体缺陷检测探针.zip

- frontend-mentors-social-proof-section

- Adaptive-Kalman-Filter.rar_adaptive kalman_kalman_卡尔曼滤波_自适应 卡尔曼_

- 【容智iBot】6容智信息·Infodator数字化生产力供应商.rar

- webcomponents-material:可重用的Custom元素库

- matlab标注字体代码-SynthTextHindi:此仓库包含用于生成印地语合成文本图像的代码

- FindNet-IP.zip

- FreeJeweled-开源

- obscenity:Obscenity是RubyRubinius,Rails(通过ActiveModel)和Rack中间件的亵渎性过滤器

- TestNG_Allure_best

- 【容智iBot】5容智信息成功案例分享——柯尼卡美能达数字化生产力项目.rar

- [已归档]一个可以轻松保存和恢复Android组件状态的库。-Android开发

- worker:高性能Node.jsPostgreSQL作业队列(也适用于使PostgreSQL触发器生成的作业将函数触发到另一个工作队列中)

- 正弦电气 EM329A用户手册.zip