Vivado IP核实战:组合逻辑电路设计与烧录

需积分: 0 123 浏览量

更新于2024-06-30

收藏 9.42MB DOCX 举报

本篇文档主要介绍了实验四,即使用Xilinx Vivado工具的IP核实现组合逻辑电路的设计与应用。首先,我们了解到IP核是一种硬件描述语言程序,它代表了特定电路功能的可重用模块,可以在不同半导体工艺中移植,Vivado工具提供了丰富的IP库,如数学运算、信号处理等,以提高设计效率。

实验的主要目的是让学生熟悉Vivado的相关操作,学习如何利用IP核进行组合逻辑电路的设计,包括基本的逻辑门(如与门、或门)以及更复杂的电路,如8421代码转换电路和数码管转换组合逻辑电路。实验中,学生需要在Vivado的Block Design环境中进行以下实践:

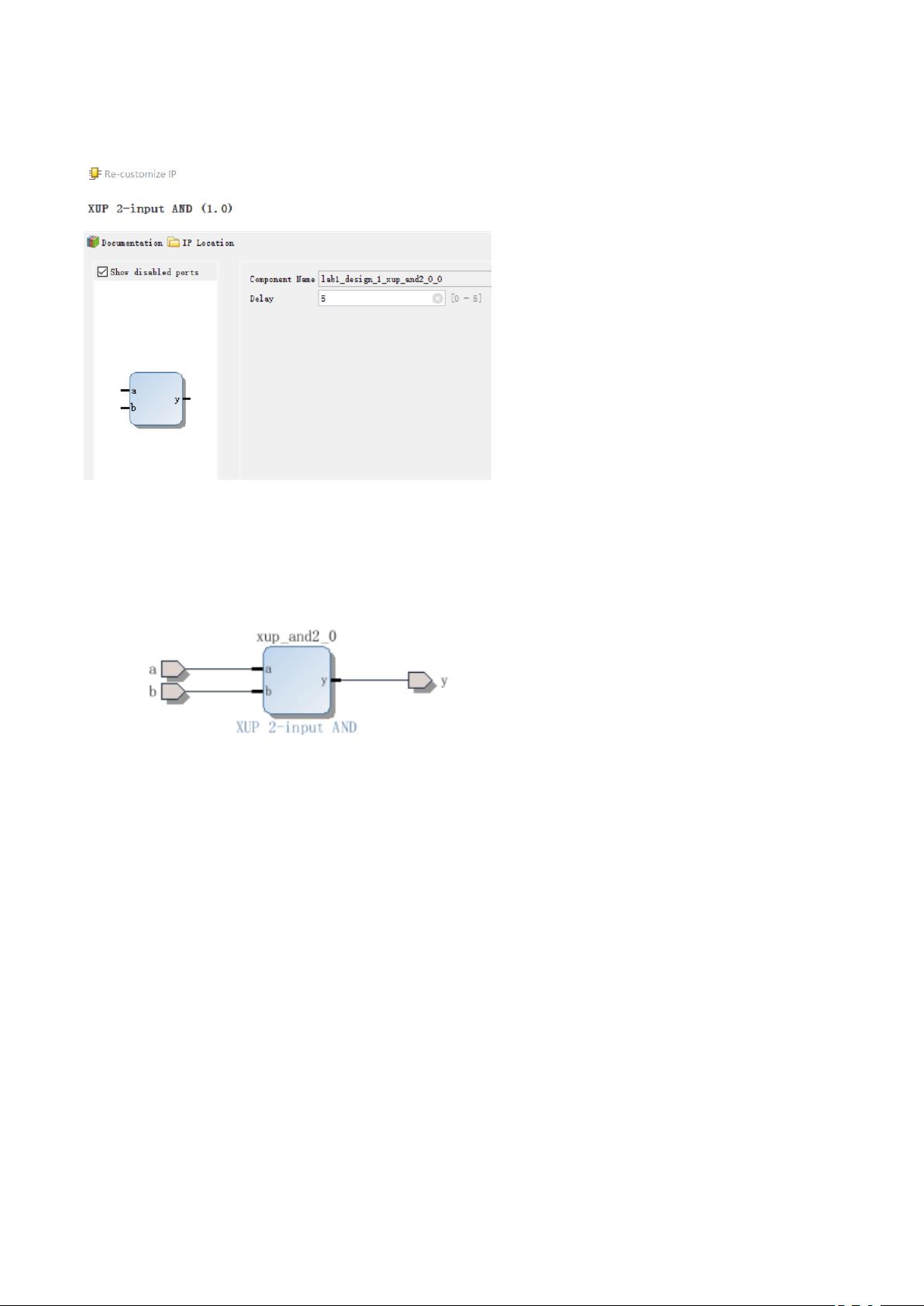

1. 实验一:与门逻辑实现

- 创建新工程并导入与门IP核

- 设置与门输出延迟,将输入(a, b)和输出(y)设为外部端口

- 通过validate design进行自动纠错

- 创建HDLWrapper并生成.v设计文件

- 分配管脚,可通过约束文件或synthesized design自动完成

2. 实验二:三位二进制数与门逻辑实现

- 模仿实验一,但输出为三位二进制数的与门

3. 实验三:或门逻辑实现

- 同样使用IP核,设计或门逻辑并烧录到basys3板

4. 实验四:8421代码转换电路

- 设计一个电路,能够处理十进制转二进制的8421编码

5. 实验五:数码管转换组合逻辑电路

- 最后一个实验是实现数码管显示的组合逻辑控制,将数字信号转化为对应的数码管显示

在整个实验过程中,需要注意Vivado Block Design不允许输入/输出引脚悬空,所有无用引脚都需要连接到无效电平。实验所需的器材包括Vivado软件和basys3开发板,这是进行实际硬件实验的基础。

通过这个实验,学生不仅锻炼了Vivado工具的使用技巧,还掌握了硬件描述语言和IP核在实际电路设计中的应用,提升了他们的系统集成能力和电路设计理解。

2022-08-08 上传

2022-08-08 上传

149 浏览量

2022-08-08 上传

2022-08-08 上传

2022-08-08 上传

2022-08-08 上传

145 浏览量

2022-08-08 上传

城北伯庸

- 粉丝: 35

- 资源: 315

最新资源

- maven-repo:Seafle android应用程序使用的Maven库

- 亮丽色彩抽象艺术插画复古欧美风ppt模板.zip

- 五边形创意简约线条年终工作汇报ppt模板.rar

- java web文件上传-下载-查看操作.rar

- NEWPIP:应用程序

- 法扎

- 蓝色软件销售公司网页模板

- 行业资料-交通装置-一种抽水马桶放水阀.zip

- TranslateBundle:Symfony捆绑包,用于使用不同的网络翻译器翻译文本

- 文泰2015软件.rar

- 互联网社交媒体产品易信介绍宣传ppt模板.rar

- 绿色娱乐商务公司网页模板

- carloshrabelo.github.io

- 正在绘制图纸的设计师背景图片PPT模板

- java基于springboot+mybatis职教务管理系统

- ScHOolY-frontend:用于学校的单页Web应用程序