安路科技EAGLE FPGA锁相环(PLL)使用教程

需积分: 15 101 浏览量

更新于2024-09-09

收藏 667KB PDF 举报

"TN305_EAGLE PLL用户指南_V1.0.pdf,这份文档是上海安路信息科技有限公司提供的EAGLE FPGA锁相环(PLL)使用指南,旨在帮助用户理解和操作EAGLE系列FPGA中的PLL硬核IP模块。文档详细介绍了PLL的功能、端口描述以及动态配置等关键内容。"

在EAGLE FPGA系列中,PLL(Phase Locked Loop)是用于时钟管理的重要组成部分。每个EAGLE FPGA芯片内建有4个多功能锁相环,分别命名为PLL0到PLL3,它们位于芯片的四个角落,以提供高性能的时钟管理功能。这些PLL能够执行时钟分频、倍频、输入与反馈时钟对齐,以及生成多相位时钟输出,并支持动态相位调整和PLL的动态参数配置。

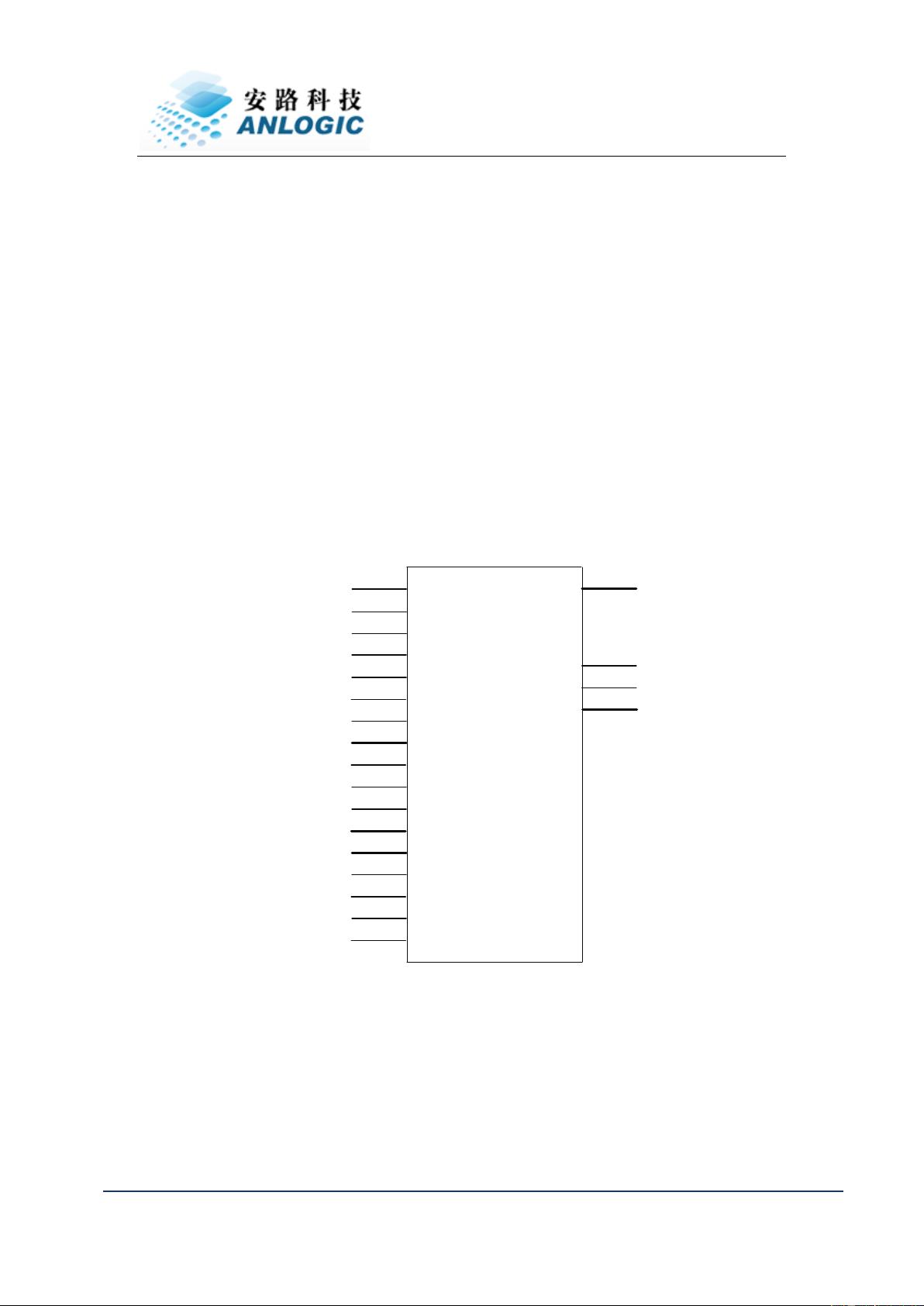

EG_PHY_PLL是EAGLE FPGA内部的具体 PLL 实现,它具有多个输入和输出端口。例如,`stdby` 输入用于控制PLL是否进入待机模式,`refclk` 是PLL的参考时钟输入,`fbclk` 是反馈时钟输出,`reset` 用于复位PLL,而`clkc` 输出PLL产生的时钟信号。其他如`extlock`表示PLL是否已锁定,`psdone` 通知动态相位移位是否已完成,`psclk`、`psdown`、`psstep` 和 `psclksel` 则用于动态相位调整。

动态相位调整是EAGLE PLL的一个重要特性,允许在运行时调整时钟相位,以优化系统性能或应对时钟抖动。这一过程可以通过`psclk`、`psdown`、`psstep` 和 `psclksel` 这些输入端口来控制,实现相位的增加或减少,以及选择特定的输出相位进行调整。

此外,EAGLE PLL还提供了动态配置接口,包括`dclk`、`dcs`、`dwe`、`di`、`daddr` 和 `do` 端口,用于在运行时更改PLL的参数。`dclk` 是动态配置时钟,`dcs` 作为片选信号,`dwe` 作为写使能,`di` 用于写入配置数据,`daddr` 设定读写地址,而`do` 输出动态配置的结果。

通过这些接口,用户可以灵活地对EAGLE FPGA的PLL进行编程,以适应不同的应用需求,例如改变时钟频率、调整相位关系或启用频率步进调制(SSC,Spread Spectrum Clocking)以减少电磁干扰。

EAGLE PLL用户指南为开发者提供了详细的操作指南和接口描述,帮助他们充分利用EAGLE FPGA的时钟管理能力,实现高效、稳定和灵活的系统设计。这份文档是理解和使用EAGLE系列FPGA PLL不可或缺的参考资料。

299 浏览量

275 浏览量

286 浏览量

550 浏览量

302 浏览量

3120 浏览量

651 浏览量

808 浏览量

kaiseradler

- 粉丝: 0

- 资源: 4

最新资源

- 金色农业农场公司网站模板

- ELT2023-12-5最新版本,v3.2344.0

- 中转方案最优遗传算法.zip

- 电话销售时如何找到拿主意的人

- FSL_project

- Test builds-开源

- draft-rpki-checklists

- Qt信号槽中的信号传递对比

- 移动:Loop的React Native应用

- WumpusHunters:StackExchange Codegolf 上 Wumpus 狩猎山王的源代码

- Meta pkg-开源

- Web-Scraping

- Consul1.17版本

- 营销管理理论与实践PPT

- Project2-2_G9:DKE 9组项目存储库

- git原理详解及实用指南-每章独立.rar