STM32F103RBT6时钟分布详解与五大模块应用

需积分: 25 115 浏览量

更新于2024-09-16

收藏 140KB DOCX 举报

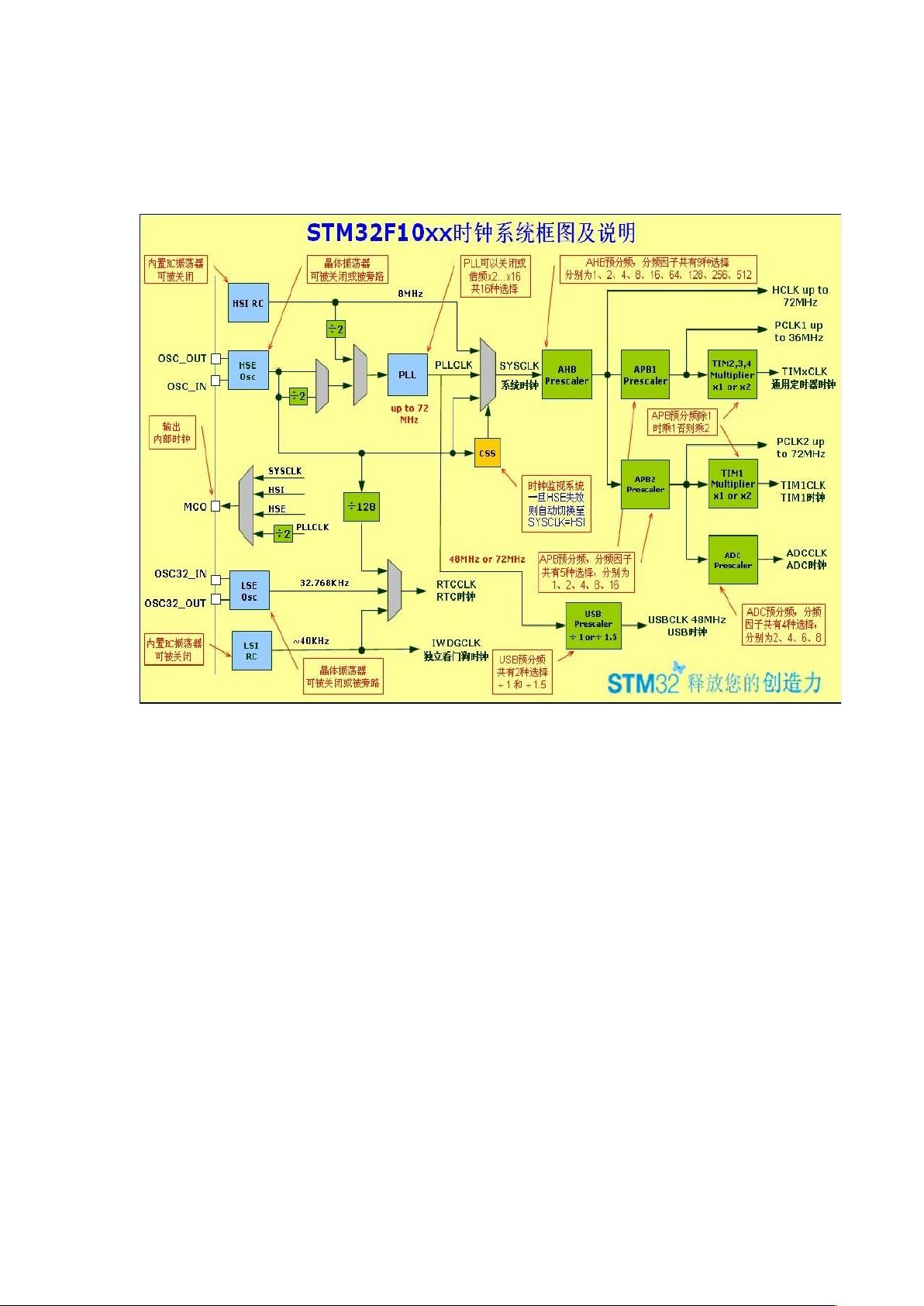

STM32的时钟分布详解主要围绕STM32F103RBT6这款微控制器展开,该系列芯片的高效时钟管理对于确保其各个外设能正确、高效地运行至关重要。STM32中的时钟系统主要包括以下五个核心时钟源:

1. **HSI (High Speed Internal Oscillator)**:内部高速RC振荡器,提供8MHz的基本时钟频率。

2. **HSE (High Speed External Oscillator)**:高速外部时钟,可以接入石英/陶瓷谐振器或外部时钟源,频率范围在4MHz到16MHz,具有更高的精度和稳定性。

3. **LSI (Low Speed Internal Oscillator)**:低速内部振荡器,频率为40kHz,主要用于低功耗模式下的辅助时钟。

4. **LSE (Low Speed External Oscillator)**:低速外部振荡器,专用于接32.768kHz的石英晶体,常用于精确的时间基准。

5. **PLL (Phase-Locked Loop)**:锁相环倍频器,接受HSI/2、HSE或HSE/2作为输入,可进行2到16倍频,但最大输出频率不超过72MHz,提供了高精度的时钟输出。

系统时钟SYSCLK是STM32的核心时钟,可供大部分器件工作。它可以选择来自PLL、HSI或HSE,最高可达72MHz。SYSCLK通过AHB(Advanced High Performance Bus)总线分频器进一步分配给五个主要模块:

- **HCLK (High Clock)**:分频后供给AHB总线、CPU内核、内存和DMA,频率最高可达72MHz。

- **Cortex定时器时钟**:经过8分频后供给Cortex处理器的系统定时器。

- **PCLK (Peripheral Clock)**:直接用于Cortex的空闲运行时钟。

- **APB1分频器**:用于APB1外设(如电源接口、CAN、USB等)以及Timer2、3、4的1或2倍频。

- **APB2分频器**:为APB2外设(如UART1、SPI1、ADC1等)、Timer1和ADC2以及所有普通和第二功能IO口提供时钟,有时还会为ADC提供2、4、6、8分频。

整个时钟管理系统的设计旨在实现灵活且高效的时钟配置,确保在各种应用场景下都能满足不同外设的性能需求。理解这些时钟源和它们的分配机制对于STM32的硬件设计、软件编程和系统优化至关重要。掌握时钟管理能让开发人员更好地控制功耗、提高响应速度,并充分利用微控制器的全部性能潜力。

4573 浏览量

181 浏览量

904 浏览量

点击了解资源详情

523 浏览量

471 浏览量

137 浏览量

179 浏览量

lianshujian

- 粉丝: 0

- 资源: 2

最新资源

- ePass3000GM驱动安装程序

- 红色热气球风景主题单页网站模板

- generator-jas

- typescout:TypeScript类型搜索器

- 完美的音调

- Texture.zip

- SSA+CNN分类算法实现

- wikibase-docker::spouting_whale:Wikibase和周围服务的Docker映像和示例撰写文件

- 企业文化建设调查问卷

- 淘常州网分类导航

- PMA通信协议分析及仿真软件

- Gmail emotional labor-crx插件

- djecommerce:https://github.comjustdjango如何

- WALL-E:高效而简单的强化学习研究框架的代码库

- galImage2Ascii:将图像转换为ASCII格式

- OkSimple:OkSimple:强大而简单的网络库