Quartus II 设计指南:项目、编译与时序分析

需积分: 31 53 浏览量

更新于2024-08-02

收藏 6.67MB PPT 举报

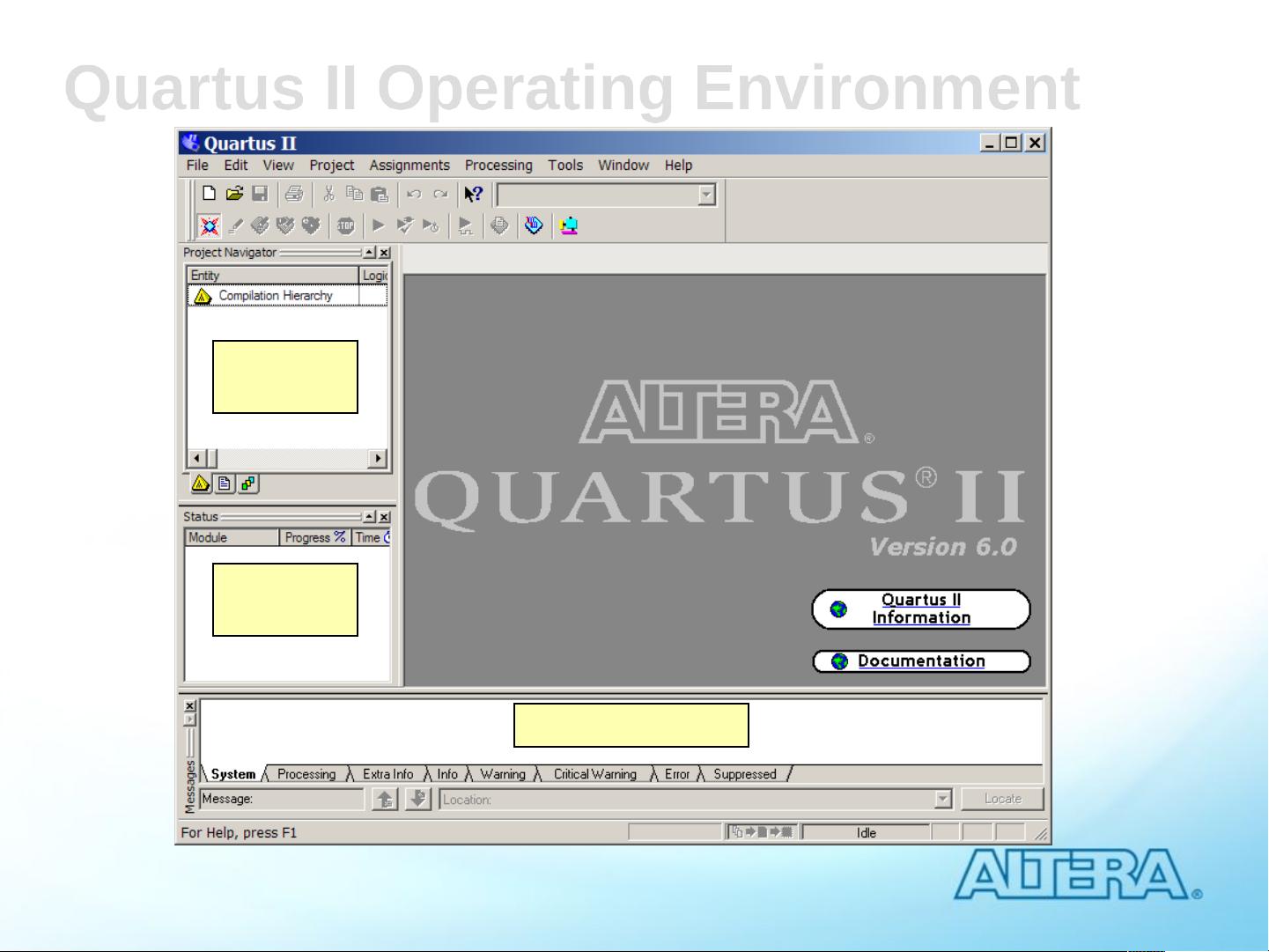

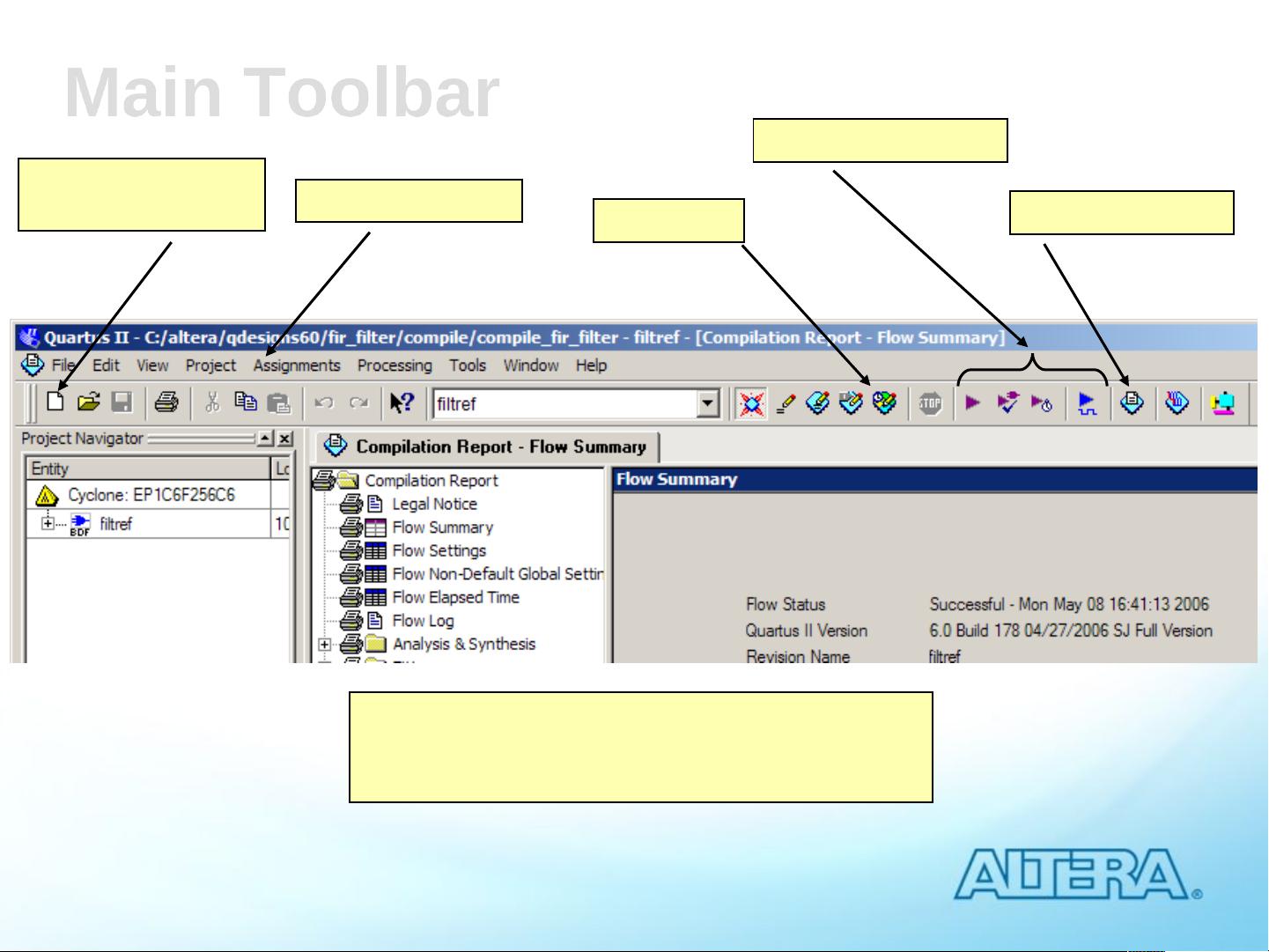

"Quartus II是Altera公司(现已被Intel收购)开发的一款强大的FPGA设计工具,它提供了一整套从设计、综合、布局布线到仿真、配置的解决方案。这款软件广泛应用于数字电路设计领域,尤其在 FPGA 开发中不可或缺。以下是Quartus II的主要功能和学习目标的详细说明。

一、创建Quartus II项目

在Quartus II中,首先需要创建一个新的项目。这包括选择目标FPGA器件、设定工作频率、添加源代码或IP核等。用户可以通过简洁的图形用户界面(GUI)完成这些操作,方便快捷地启动设计流程。

二、设计编译

设计编译是将HDL(硬件描述语言,如VHDL或Verilog)代码转化为逻辑门级网表的过程。Quartus II提供了全面的编译选项,包括预编译、全编译、快速编译等,以适应不同的设计需求和时间效率。

三、定位编译信息

在编译完成后,Quartus II会生成丰富的报告,包括综合报告、映射报告和时序分析报告等,帮助设计师了解设计的资源占用情况、性能指标和可能存在的问题。

四、设计约束

为了满足特定的性能要求,设计师需要对设计进行约束,如设置时钟路径、分配引脚等。这些约束可以确保设计在实际硬件中的正确运行,并对时序进行优化。

五、时序分析

时序分析是评估设计是否满足速度要求的关键步骤。Quartus II提供了两种时序分析工具:Classic Timing Analyzer 和 TimeQuest Timing Analyzer。经典时序分析器适用于基础的时序验证,而TimeQuest Timing Analyzer则具备更高级的功能,如静态时序分析、时序优化等,能提供更精确的时序结果。

六、仿真

在硬件实现之前,通过仿真可以验证设计的功能是否正确。Quartus II集成了ModelSim等仿真工具,可以生成波形并模拟设计的行为,帮助找出潜在的错误和问题。

七、配置FPGA

最后,一旦设计经过验证,就可以通过Quartus II将配置文件下载到FPGA中。Quartus II支持各种配置方式,包括JTAG、SPI和配置存储器等,以适应不同应用场景的需求。

课程通常会涵盖以上所有内容,并通过一系列练习来帮助学员熟练掌握Quartus II的各个功能,包括创建项目、设计编译、时序分析、仿真以及FPGA的配置。通过学习,设计师将能够有效地使用Quartus II进行高效的FPGA设计工作,同时理解和应用相关的知识产权(IP),如信号处理、通信和嵌入式处理器技术,以及各种FPGA系列(如Stratix和Cyclone)的特点和应用。"

2009-08-17 上传

2014-07-19 上传

2011-05-08 上传

2012-05-09 上传

2014-11-20 上传

2010-01-23 上传

2011-03-15 上传

2019-09-20 上传

fsgbeyond

- 粉丝: 1

- 资源: 1

最新资源

- QT-坐标系统和坐标变换-绘制曲线应用程序示例

- com.serenegiant.common.1.5.20

- QT-坐标系统和坐标变换-绘制三个五角星应用程序示例

- 无边框显示阴影控件Dwm-master

- GLD授权V2020.11.14(含全国写锁工具)

- qt-使用qt开发的五子棋小游戏-附项目源码.zip

- 简历-求职简历-word-文件-简历模版免费分享-应届生-高颜值简历模版-个人简历模版-简约大气-大学生在校生-求职-实习

- docker-compose 最新版本的当前时间离线安装包

- 开源书签管理程序Mtab网站源码,附带视频搭建教程

- 简历-求职简历-word-文件-简历模版免费分享-应届生-高颜值简历模版-个人简历模版-简约大气-大学生在校生-求职-实习

- 简历-求职简历-word-文件-简历模版免费分享-应届生-高颜值简历模版-个人简历模版-简约大气-大学生在校生-求职-实习

- 简历-求职简历-word-文件-简历模版免费分享-应届生-高颜值简历模版-个人简历模版-简约大气-大学生在校生-求职-实习

- 简历-求职简历-word-文件-简历模版免费分享-应届生-高颜值简历模版-个人简历模版-简约大气-大学生在校生-求职-实习

- 简历-求职简历-word-文件-简历模版免费分享-应届生-高颜值简历模版-个人简历模版-简约大气-大学生在校生-求职-实习

- 简历-求职简历-word-文件-简历模版免费分享-应届生-高颜值简历模版-个人简历模版-简约大气-大学生在校生-求职-实习

- 简历-求职简历-word-文件-简历模版免费分享-应届生-高颜值简历模版-个人简历模版-简约大气-大学生在校生-求职-实习