ARM9处理器的MMU和CACHE机制

需积分: 17 156 浏览量

更新于2024-07-21

1

收藏 726KB PPT 举报

ARM9 MMU与CACHE

ARM9处理器中,MMU(Memory Management Unit,内存管理单元)和CACHE(高速缓存)是两个关键组件,负责管理内存地址和提高处理器性能。本文将详细介绍ARM9 MMU与CACHE的工作原理、存储管理机制、CP15协处理器、MCR和MRC指令等相关知识点。

1. ARM9 MMU与CACHE概述

ARM9处理器提供线性地址管理机制,通过MMU和CACHE来缩小处理器和存储设备的速度差别,提高整体性能。MMU实现虚拟地址到物理地址的映射,提供存储保护机制,限制对局部存储的访问权限。CACHE则是高速缓存,负责存储常用的数据和指令,以提高处理器的执行速度。

2. 存储管理机制

ARM9处理器的存储管理机制主要包括虚拟地址(VA)、变换地址(MVA)和物理地址(PA)三个概念。虚拟地址是CPU执行程序的地址,由编译器编译后形成的;变换地址是经由CP15寄存器平移变换后的虚拟地址,在有CACHE的情况下,是CACHE的地址;物理地址是存储器实体的地址。MMU和CACHE的工作方式有三种:线性空间、MMU启用但不启用CACHE、启用MMU和CACHE。

3. CP15协处理器

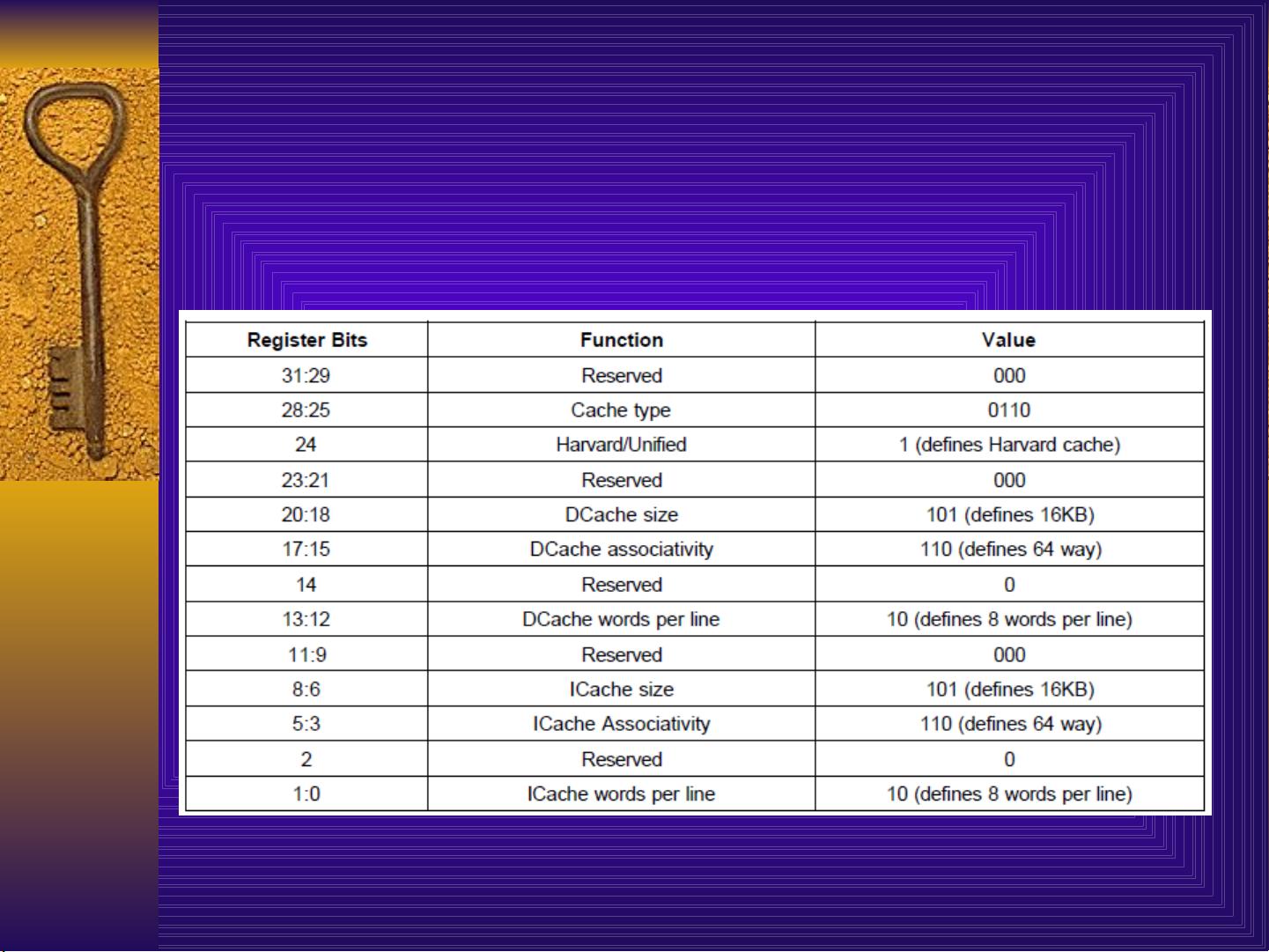

CP15协处理器是ARM920T处理器的核心组件,主要负责存储管理、控制MMU和CACHE。CP15协处理器采用V4版本,有16个32bit寄存器(C0~C15),并提供两条扩展的操作指令MCR和MRC。

4. MCR和MRC指令

MCR指令将ARM寄存器的值写入CP15寄存器中,格式为MCR{<cond>}p15,<opcode1=0>,<Rd>,<CRn>,<CRm>{,<opcode2>}。MRC指令将CP15寄存器的值写入ARM寄存器中,格式为MRC{<cond>}p15,<opcode1=0>,<Rd>,<CRm>,<CRm>{,<opcode2>}。这两个指令只能在系统模式下运行,在用户模式下运行将产生未定义指令异常。

5. MMU用途

MMU的用途包括ID编号、控制位、存储器保护和控制、内存保护和控制等。MMU的控制位包括MMU、Cache属性设置等。地址转换表基地址和域访问控制也是MMU的重要功能。

ARM9 MMU与CACHE是ARM9处理器的核心组件,负责管理内存地址和提高处理器性能。深入了解MMU和CACHE的工作原理和存储管理机制,对于嵌入式系统的开发和应用具有重要意义。

2021-12-18 上传

2014-08-24 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-11-30 上传

2021-10-06 上传

2021-10-06 上传

cjltch

- 粉丝: 0

最新资源

- Python脚本管理工具my-scripts使用指南

- VueSetter:实现Vue数据双向绑定的插件

- Java实现的员工数据库MySQL应用程序功能解析

- 在CentOS7上部署Docker与ELK集群实现项目发布和日志管理

- 深入理解SwiftUI的Navigation:基础指南

- R-Studio数据恢复工具:经典与便捷的结合

- 动态黑色箭头PPT模板艺术下载

- 简约黑白风景旅游PPT模板免费下载

- React购物车实现教程:第一步创建React应用

- 方舟助手v1.0.3.34:高效图片视频编辑与发布

- 【电脑主题】熊猫大侠系列:英武动漫风win7桌面主题

- OpenPCS 7 (V8.1 SP1) 过程控制系统使用手册

- SoonToBe即将推出的JoinPay支付技术

- Webpack加载器ihtml-loader深度解析

- 吉卜力电影前端展示与API数据检索学习项目

- PICT工具:生成有效软件测试用例的正交方法