FPGA设计基础与QUARTUS II教程详解

需积分: 10 97 浏览量

更新于2024-07-29

收藏 2.93MB PDF 举报

"FPGA设计及QUARTUS+II教程"

本教程主要涵盖了FPGA设计的基础知识和QUARTUS II软件的使用方法。FPGA(Field-Programmable Gate Array),即现场可编程门阵列,是一种高度灵活的集成电路,允许用户根据需求自定义其内部逻辑。这种可编程性使得FPGA在众多领域,如人工智能、机器人、通信、图像处理等,都有广泛的应用。

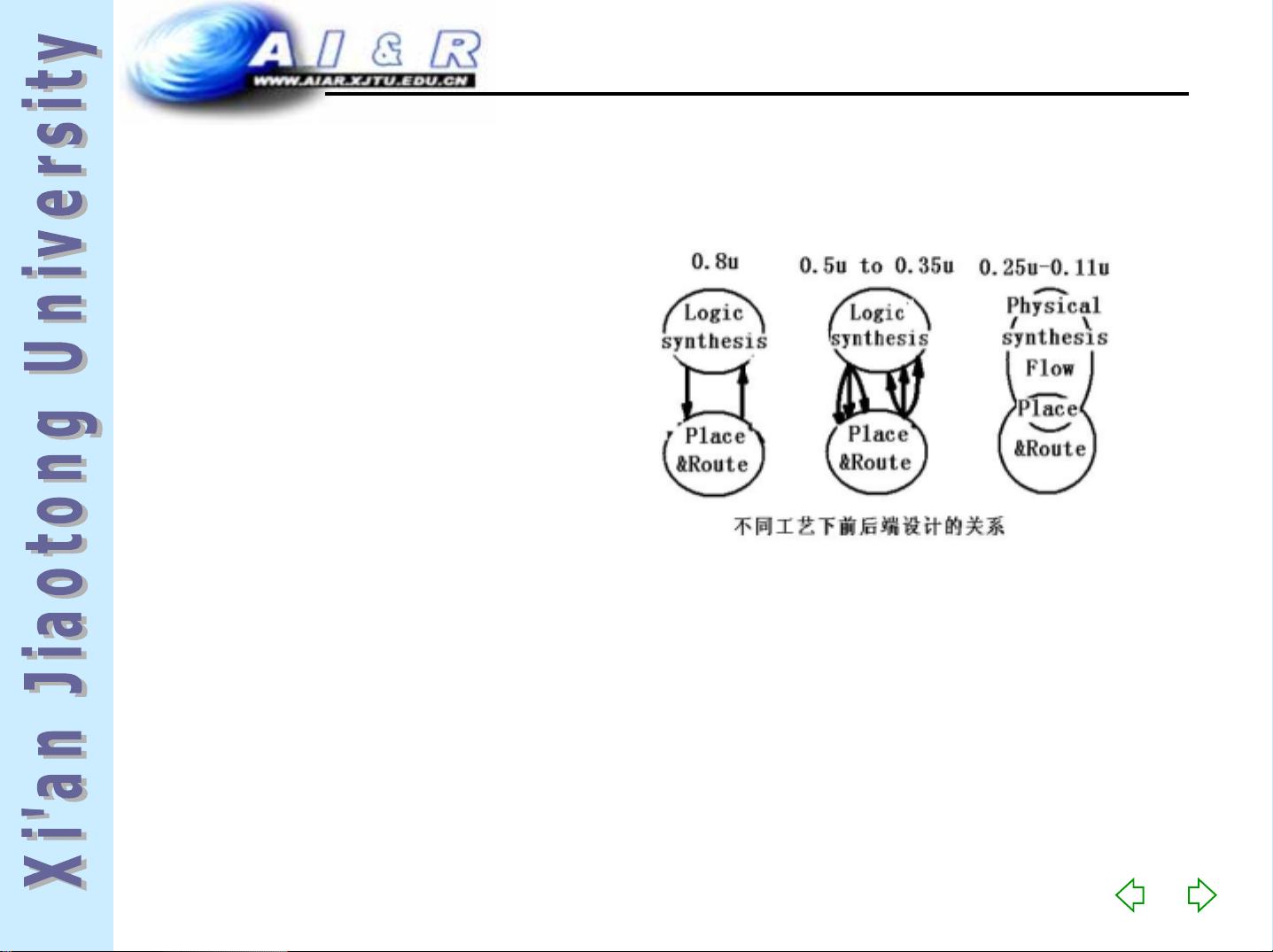

在IC设计概述中,我们了解到摩尔定律,即集成电路的集成度大约每18个月翻一番,这背后的技术进步包括晶圆尺寸增大、设计方法优化、设计工具的发展以及器件尺寸的持续缩小。IC设计有两个主要发展方向:一是追求超高速、超高集成度的电路,二是发展各种专用集成电路(ASIC),充分利用现有的工艺和技术。

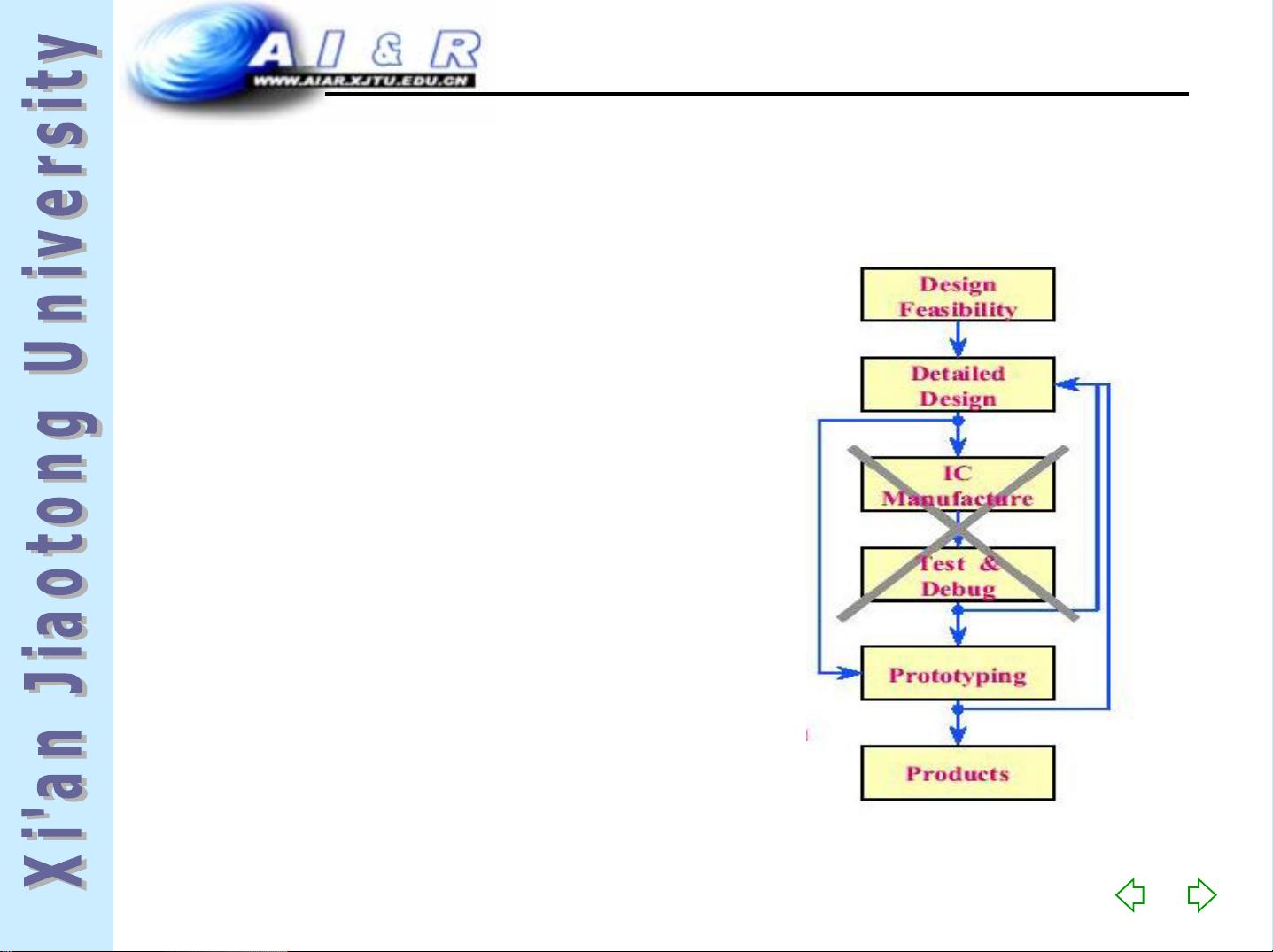

IC设计有着严格的要求,包括设计时间、设计正确性、设计成本、产品性能和可测性设计。设计时间直接影响费用和市场竞争力;正确性至关重要,因为IC一旦设计完成并制造出来,错误难以修正;设计成本涉及设计费用和生产费用,通过减小芯片面积来降低成本;产品性能依赖于器件结构和电路设计;而可测性设计则要求引入测试电路以确保质量和发现潜在问题,测试在整个设计流程中占据了很大比重。

进入FPGA设计流程,通常包括以下步骤:需求分析、逻辑设计、硬件描述语言(HDL)编程、逻辑综合、时序分析、布局布线、仿真验证和硬件调试。在这个过程中,QUARTUS II作为Altera公司(现Intel FPGA部门)的主力开发工具,提供了一整套的集成环境,支持VHDL和Verilog HDL,用于代码编写、编译、仿真、时序分析以及生成比特流文件,最后将该文件下载到FPGA实现硬件配置。

QUARTUS II使用简介部分,会详细讲解如何创建工程、编写HDL代码、进行功能仿真、时序分析、设置约束条件、进行物理综合和布局布线,以及最终生成配置文件和烧录到FPGA硬件的过程。此外,QUARTUS II还提供了丰富的IP核库,方便用户快速集成和实现复杂的功能模块。

这个教程对于想要学习FPGA设计和掌握QUARTUS II工具的人来说是一份宝贵的资源,它不仅教授了FPGA的基本概念,还深入到实际设计的各个环节,帮助初学者逐步掌握这一领域的核心技能。通过学习,你可以具备独立完成FPGA项目设计的能力,并能有效地利用QUARTUS II提高设计效率。

1378 浏览量

109 浏览量

119 浏览量

点击了解资源详情

点击了解资源详情

点击了解资源详情