"FPGA Vivado超详细教程:新建工程、添加源文件,适合初学者"

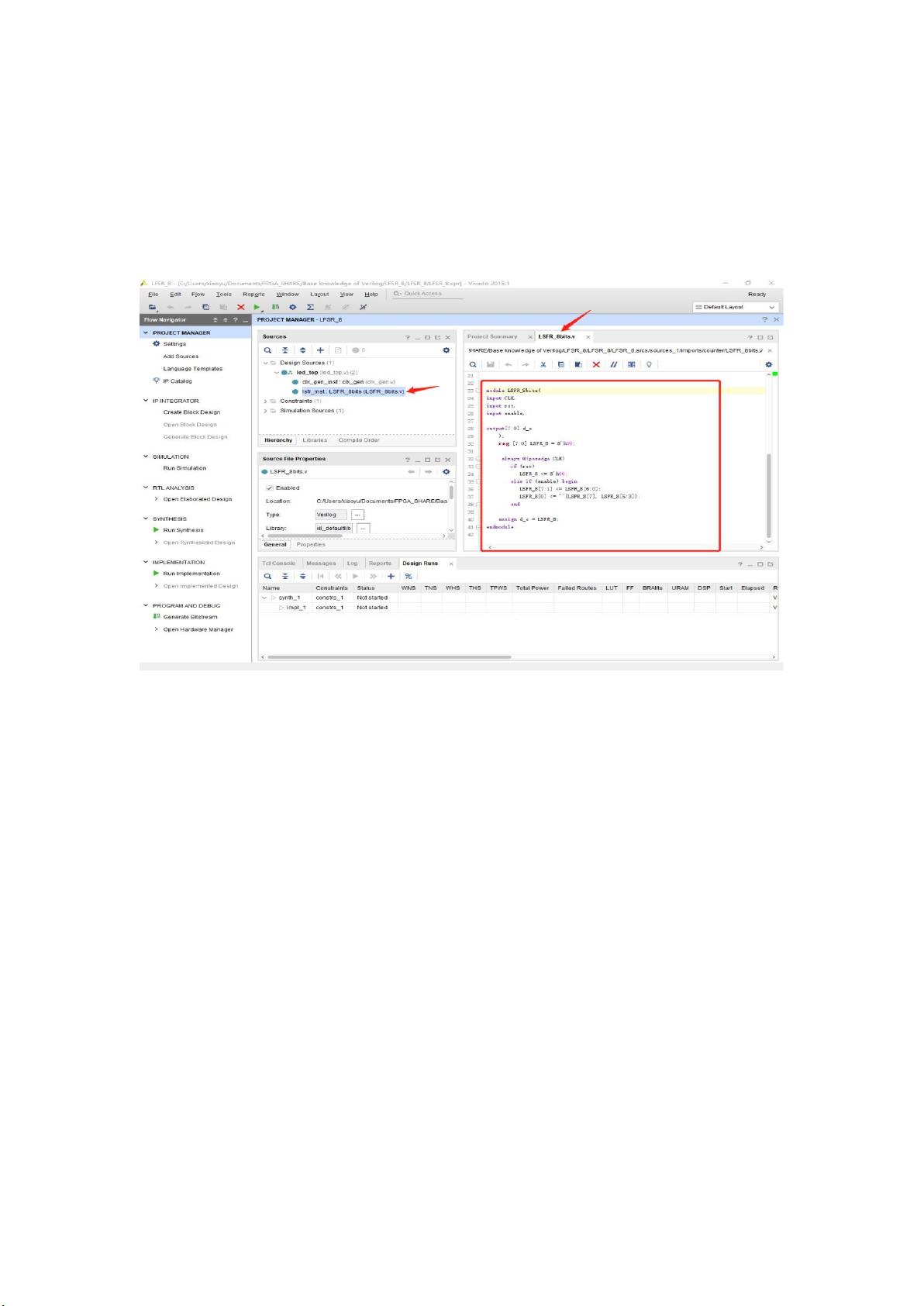

FPGA vivado超详细使用教程适合初学者。在使用FPGA vivado时,首先需要创建新工程。点击Create Project,在弹出的窗口中选择工程放置路径与工程名字,并选择RTL Project。勾选Do not specify at this time,表示在新建工程时不去指定源文件。接下来选择器件或者板卡,其中Parts表示器件,Boards表示板卡。可以根据系列去选器件,也可以直接在Search栏搜索器件型号。器件的选择根据你的FPGA芯片来定,一般在所用的开发板手册里可以找到。选择完毕后点击Next。确认整个工程信息后,点击Finish,完成工程创建。

接下来是添加源文件。在Flow Navigator界面下点击Add Sources。可以选择添加或者新建XDC约束文件、设计文件或者仿真文件。选择添加设计文件,再点击Next。在Add Files中可以添加已有的设计文件,新建file时指定文件名与路径。点击Finish完成添加源文件。

除了添加设计文件,还可以添加或者新建XDC约束文件。在Flow Navigator界面下点击Add Sources,选择添加或者新建XDC约束文件,再点击Next。在弹出的窗口中可以选择添加已有的XDC约束文件,也可以新建文件。点击Finish完成添加XDC约束文件。

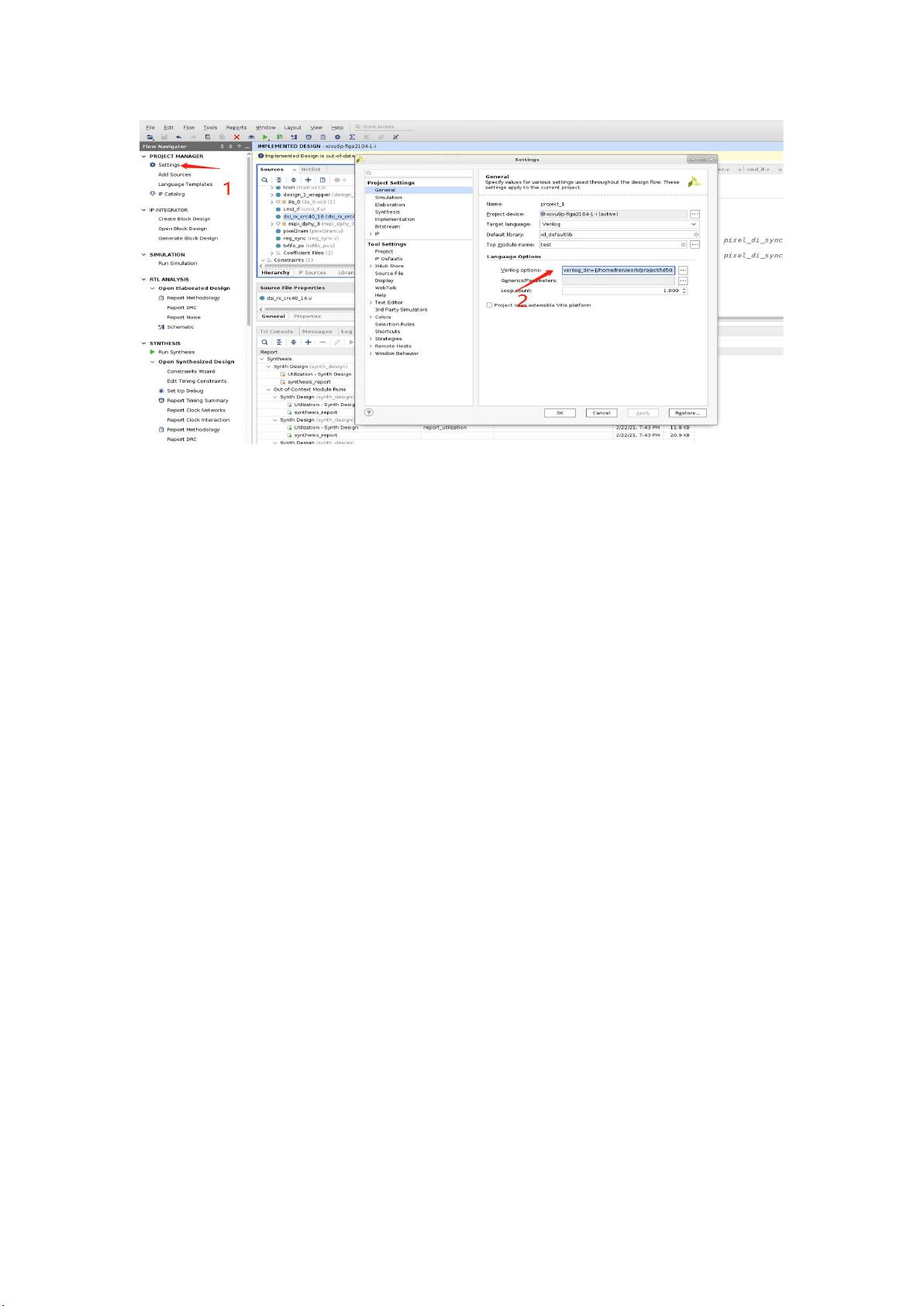

在Vivado中进行FPGA验证时,也需要进行一些操作。首先是进行设计规范检查。在Flow Navigator中点击Run Synthesis,等待综合完成后,可以在Reports中查看RTL Analysis结果进行设计规范检查。接着进行时序规划。在Flow Navigator中点击Open Elaborated Design,进入Design Runs界面,在工具栏中选择Open Synthesized Design。选择Tools下的最后一个Selection定位Window,找到Hierarchy中最上层的Design的名称,双击即可打开综合后的设计结构。在综合后的设计结构中进行时序规划。

进行FPGA验证的最后一步是生成bit文件。在Flow Navigator中点击Generate Bitstream,等待生成完毕。生成bit文件后可以下载到FPGA中进行验证。

以上就是FPGA vivado超详细使用教程的基本内容,对初学者来说可以作为一个简单的指南。希望能够帮助大家更好地了解FPGA vivado的使用方法。

2024-08-22 上传

2014-07-20 上传

2007-12-23 上传

2009-07-17 上传

2008-12-09 上传

141 浏览量

木目君

- 粉丝: 0

- 资源: 2

最新资源

- Addison Wesley Stephen C Dewhurst C++ Gotchas Avoiding Common Problems in.Coding and Design.pdf

- Prentice Hall Bruce Eckel Thinking In C++ Second Edition Volume 1.pdf

- verilog 练习

- Flex 3 实用教程

- C#命名规范 C#命名规范

- NiosII 嵌入式系统软件设计

- 毕业论文注意参考,答辩准备

- 华清软件,Symbian课件

- Hibernate开发指南.pdf

- iphone web开发与iphone SDK开发

- Windows Sockets 规范及应用.pdf

- 面向汽车防撞的混沌激光雷达

- word2003上机练习题

- 高质量C++/C编程指南.pdf

- Eclipse中文教程

- AIX命令参考大全1