基于Verilog的可控100进制可逆计数器设计

版权申诉

Verilog FPGA 程序课程设计

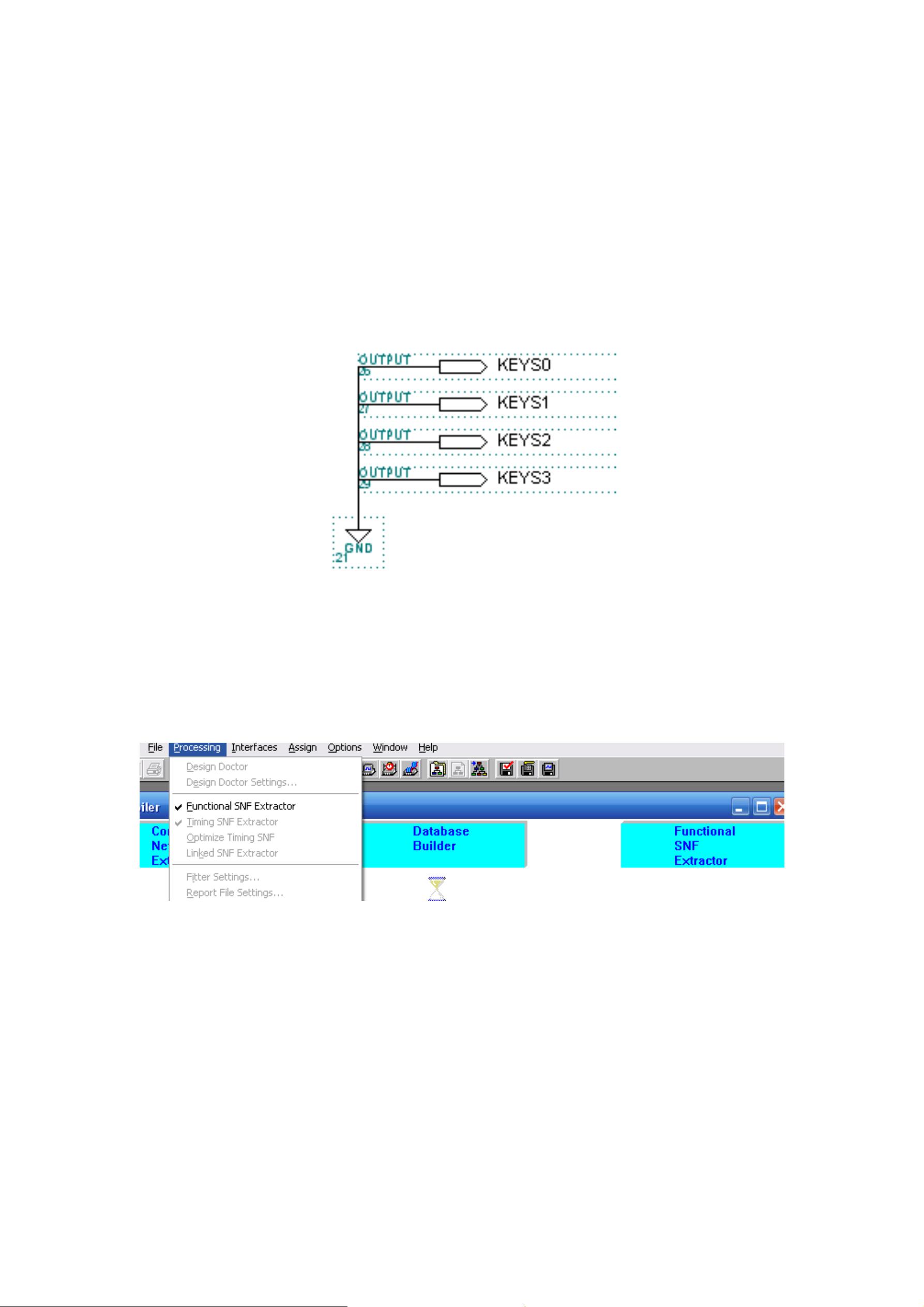

在这篇课程设计中,我们将学习如何使用 Verilog 语言设计一个可控的 100 进制可逆计数器。这个计数器具有复位、增或减计数、暂停功能,并且可以显示十进制形式的数值。

**计数器的设计**

在设计这个计数器时,我们需要考虑到它的四种工作模式:清零,加计数,减计数和暂停。为了实现这些功能,我们可以使用 case 语句来选择不同的工作模式。

**源代码解析**

在源代码中,我们首先定义了一个模块 `updown_count`,它有五个输入信号:`qout`、`reset`、`clk`、`plus` 和 `minus`。其中,`qout` 是一个 8 位的输出信号,表示计数器的当前值。`reset` 是一个输入信号,用于清零计数器。`clk` 是时钟输入信号,用于触发计数器的工作。`plus` 和 `minus` 是两个控制输入信号,用于控制计数器的增或减计数功能。

在模块内部,我们使用 `always` 语句来描述计数器的行为。当时钟信号上升沿到来时,计数器将执行一次操作。如果 `reset` 信号为低电平,则计数器将清零,否则将执行增或减计数操作。

**Case 语句的使用**

在源代码中,我们使用 case 语句来选择不同的工作模式。Case 语句的条件是 `{minus, plus}`,它可以取三种值:`2'b10`、`2'b01` 和 `2'b11`。根据不同的条件,我们可以选择不同的工作模式。

**减计数模块**

在减计数模块中,我们首先判断个位是否为零。如果个位为零,则执行后面的程序,个位直接赋值为 9,并且十位减一;否则个位减一。这是因为在减计数操作中,我们需要借用十位的值来减少个位的值。

**增计数模块**

在增计数模块中,我们首先判断个位是否为 9。如果个位为 9,则执行后面的程序,个位直接赋值为 0,并且十位加一;否则个位加一。

**结论**

通过这个课程设计,我们学习到了如何使用 Verilog 语言设计一个可控的 100 进制可逆计数器。我们了解了计数器的四种工作模式,并且学习到了如何使用 case 语句来选择不同的工作模式。同时,我们也学习到了如何设计减计数和增计数模块,以实现计数器的减计数和增计数功能。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2023-04-04 上传

2022-11-16 上传

2013-12-16 上传

2020-03-19 上传

2021-07-13 上传

2022-07-03 上传

G11176593

- 粉丝: 6916

- 资源: 3万+