Formality工具使用教程:从RTL到门级验证

"Formality使用指南提供了对Formality工具的操作步骤,主要涉及如何检查RTL源代码与门级网表的一致性。该指南包括对FIFO设计的实例,包括RTL源代码、技术库、综合的门级网表以及插入扫描链的门级网表。在检查过程中,用户需将RTL源代码设置为参考设计,而门级网表设置为实现设计,然后通过图形用户界面进行形式验证。"

Formality是一款强大的形式验证工具,用于确保硬件设计的RTL描述和门级表示在功能上是等价的。在这个使用指南中,重点讲解了如何利用Formality来检查RTL与GATE网表的一致性,这对于集成电路设计的验证过程至关重要。一致性检查可以发现设计中的潜在错误,避免在物理实现阶段出现代价高昂的修正。

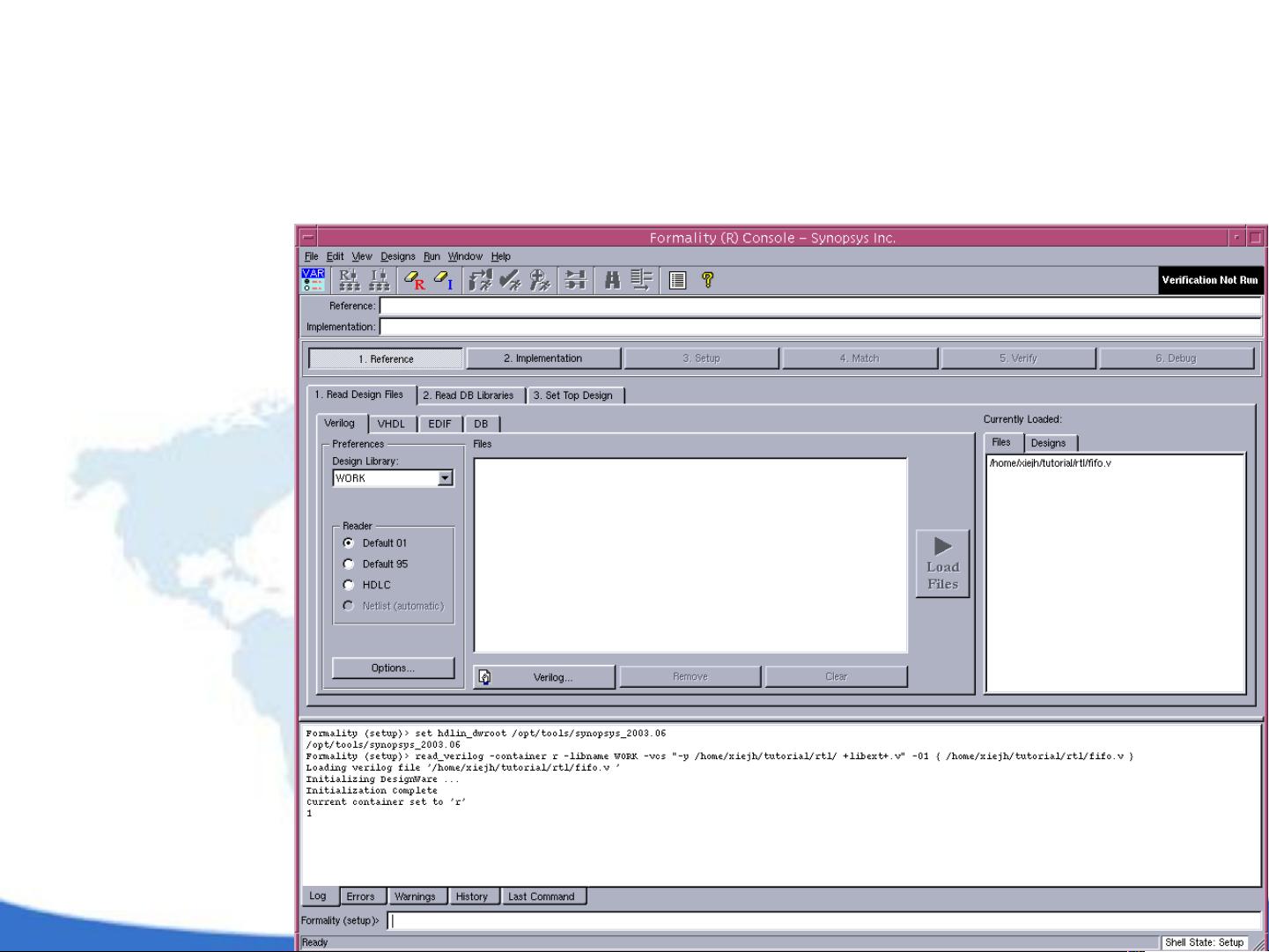

首先,指南中提到了FIFO(First In First Out,先进先出)的实例,这是一个常见的数据缓冲区设计,包含了多个子模块,如gray_counter.v、push_ctrl.v等。这些源代码位于Rtl目录下,是RTL描述的基础。同时,为了门级仿真和测试,还有对应的门级网表文件,如fifo.vg,它们位于Gate目录中。

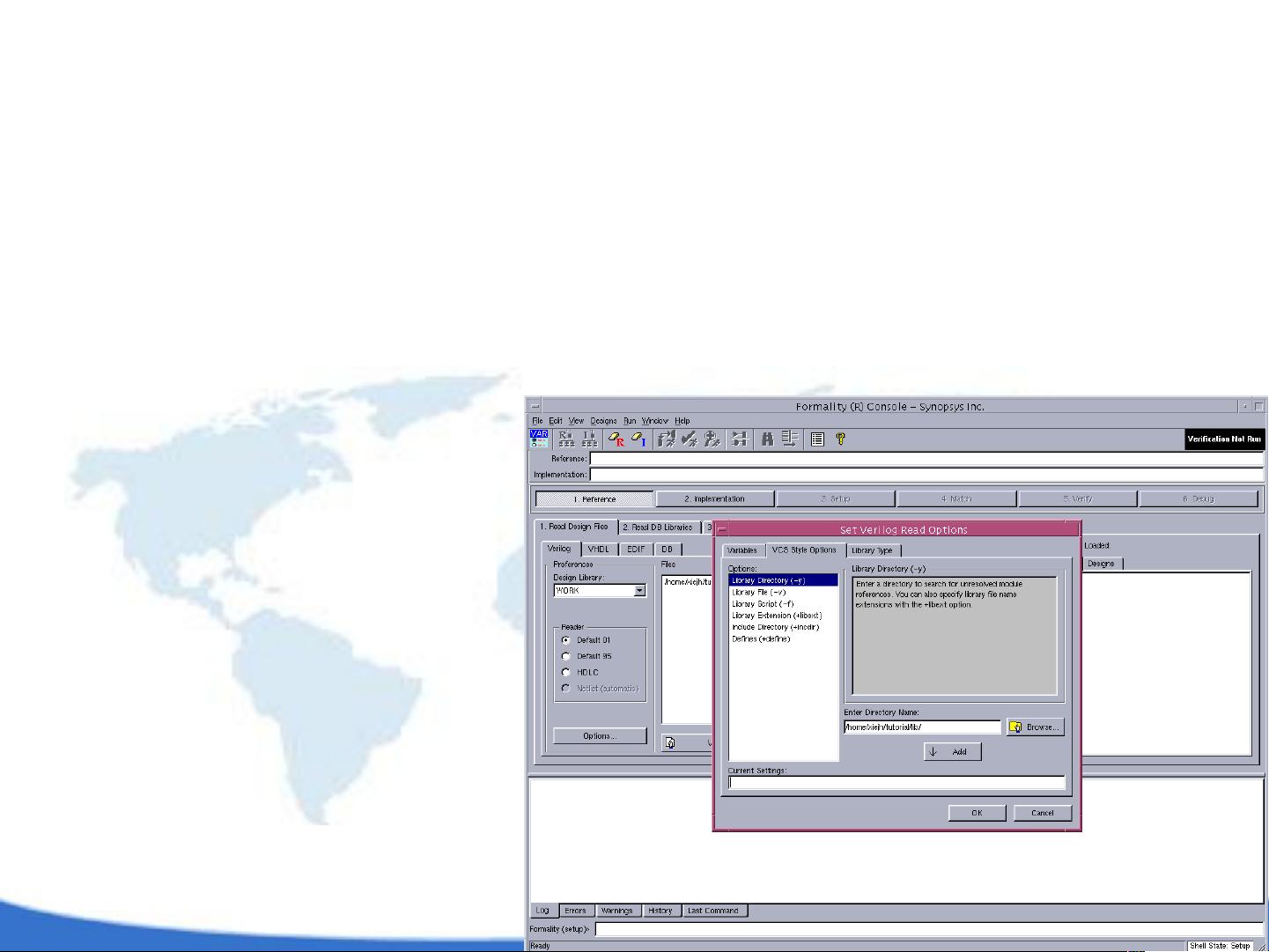

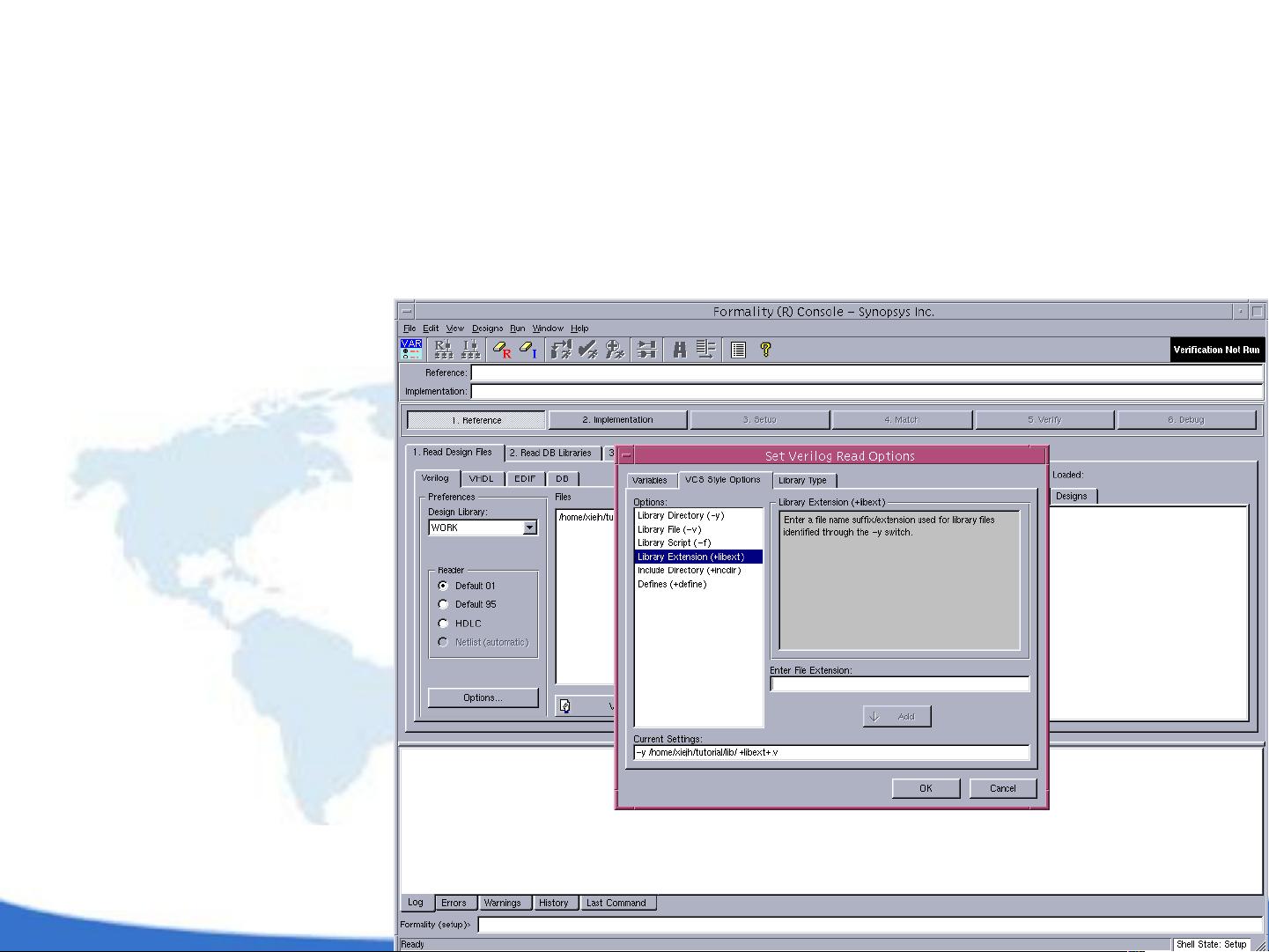

为了进行形式验证,首先要设置参考设计和实现设计。参考设计通常为未经综合的RTL源代码,如fifo.v,它描述了设计的逻辑行为。而实现设计则是经过综合后的门级网表,如fifo.vg,代表了实际的电路布局。在Formality的图形用户界面中,用户需要指定这两个设计文件的位置,并设置相应的搜索目录,以便工具能够找到相关的库文件。

设置搜索目录时,需要指定Synopsys工具的安装路径,这样Formality才能找到必要的库支持。这一步通常涉及到设置环境变量或者直接输入工具的安装路径,如/opt/tools/synopsys。设置完成后,Formality就可以读取并比较RTL源代码和门级网表,检查它们在功能上的匹配程度。

除了基本的检查,指南还提到了插入扫描链的门级网表(Gate_with_scan目录)和带有JTAG链的门级网表(Gate_with_scan_jtag目录)。这些网表用于在硬件测试中引入可测试性结构,方便进行边界扫描和故障诊断。在形式验证过程中,也需要对这些增强的网表进行相同的功能一致性检查。

Formality使用指南通过一个具体的FIFO设计案例,详细介绍了如何使用Formality工具进行形式验证,包括设置设计文件、指定搜索路径以及执行一致性检查,这对于理解和操作Formality进行设计验证是非常有价值的。通过这样的步骤,设计者可以确保他们的硬件设计在逻辑和物理层面都是准确无误的。

点击了解资源详情

点击了解资源详情

349 浏览量

881 浏览量

437 浏览量

209 浏览量

2024-06-15 上传

133 浏览量

wenskdy

- 粉丝: 0

- 资源: 6

最新资源

- Lotus关于获取URL字符串参数

- jsp数据库经典案例

- 基于LabVIEW步进电机PID控制系统的设计

- GNU映像原理-映像文件及执行机理

- 编程错误中英对照.txt

- 一个智能卡相关的类 PCSC.txt

- CDMA2000系统中的鉴权分析

- Oracle日期时间(Date/Time)操作

- PL/SQL 库程序设计语言介紹

- 什么是RUIM卡,可移动用户识别模块

- 转自名为“来自我心”的博客《中国移动面经、薪酬全攻略》

- 毕业论文—jsp技术实现的系统

- Matlab神经网络工具箱应用介绍

- Office SharePoint Server 2007 规划和基础架构 -2.pdf

- 开源技术选型手册精选版.pdf

- J2EE完全参考手册-J2EE概述-pdf.pdf