IDT72T系列高吞吐量TeraSync FIFO存储器规格详解

需积分: 1 136 浏览量

更新于2024-06-20

收藏 525KB PDF 举报

"C1547695_FIFO存储器规格书_RENESAS(瑞萨)_IDTFIFO存储器规格书.PDF"

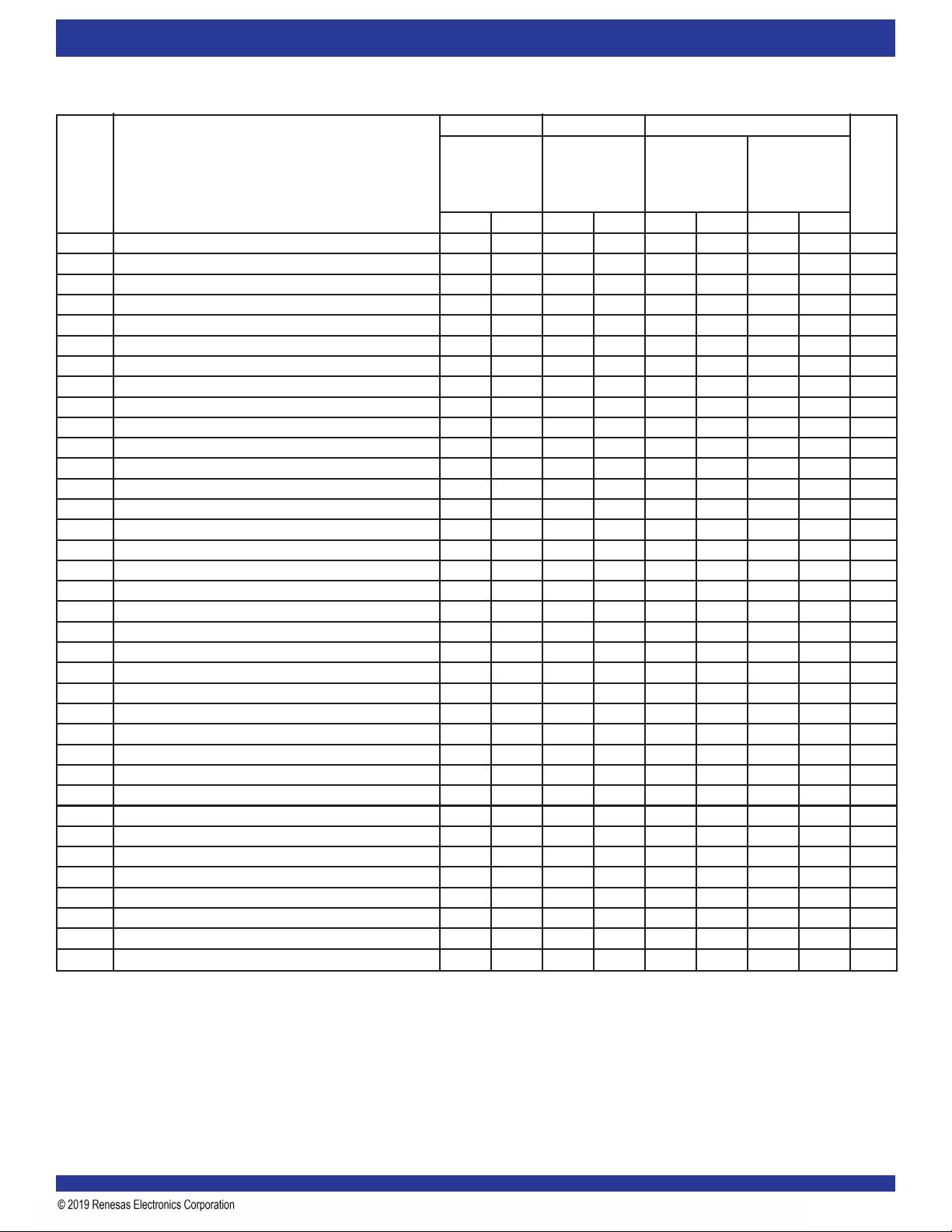

IDT72T72系列是瑞萨电子(RENESAS)推出的一种高性能TeraSync™ FIFO(First-In-First-Out,先进先出)存储器,主要用于商业和工业温度范围的应用。该系列提供了多种配置,包括16,384x72、32,768x72、65,536x72和131,072x72位的容量选项。这些FIFO器件旨在实现高速数据传输,并具备一系列先进的功能特性。

在功能结构上,IDT72T72系列FIFO包含输入寄存器、输出寄存器、RAM阵列、标志逻辑、读写指针控制逻辑、复位逻辑等关键组件。这些组件协同工作,确保数据的正确存储和检索。例如,输入寄存器接收并暂存外部数据,输出寄存器则在读取时提供数据。RAM阵列是存储数据的主要区域,根据配置的不同,其大小也会有所变化。

FIFO的工作原理是基于先进先出的原则,即最先写入的数据将最先被读出。读写控制逻辑管理数据的流入流出,而读写指针则跟踪存储器中的数据位置。复位逻辑用于初始化FIFO的状态,WEN(Write Enable)和RCLK/RD(Read Clock/Read Data)信号控制着数据的写入和读取。

此外,IDT72T72系列还提供了诸如OFFSET REGISTER、BUS CONFIGURATION BM CONTROL LOGIC、FSEL0/FSEL1等高级特性,用于配置和优化FIFO的操作。比如,OFFSET REGISTER允许设置数据读取的偏移,便于处理不同起始地址的数据流。BUS CONFIGURATION BM CONTROL LOGIC则支持自定义总线配置,适应不同的系统需求。

在接口方面,器件提供了如WCLK/WR(Write Clock/Write)、D0-Dn(数据输入)、REN(Read Enable)、RCLK/RD(Read Clock/Read Data)、OE(Output Enable)等信号,以及用于同步和调试的JTAG(Joint Test Action Group)控制端口,如TCK(Test Clock)、TMS(Test Mode Select)、TDO(Test Data Out)、TDI(Test Data In)和TRST(Test Reset)等。

该系列FIFO的特点包括:

1. 高速性能:适用于需要快速数据传输的系统。

2. 宽温操作:适用于商业和工业环境,具有良好的温度耐受性。

3. 多种容量选择:可以根据应用需求灵活选择存储容量。

4. 高度集成:集成了多种控制逻辑和功能,简化系统设计。

5. 可配置性:通过各种控制信号和寄存器,可以适应不同的系统需求和工作模式。

IDT72T72系列FIFO存储器是面向高速、高可靠性应用场景的理想选择,广泛应用于通信、数据处理、工业自动化等领域。其丰富的功能和可配置性使得它能够满足复杂系统对数据缓冲和同步的需求。

2023-09-20 上传

2024-09-08 上传

2023-07-14 上传

2023-07-14 上传

2023-07-14 上传

2023-06-01 上传

2023-05-30 上传

2023-09-01 上传

GoogleNetᅟᅠ

- 粉丝: 4221

- 资源: 2489

最新资源

- C语言快速排序算法的实现与应用

- KityFormula 编辑器压缩包功能解析

- 离线搭建Kubernetes 1.17.0集群教程与资源包分享

- Java毕业设计教学平台完整教程与源码

- 综合数据集汇总:浏览记录与市场研究分析

- STM32智能家居控制系统:创新设计与无线通讯

- 深入浅出C++20标准:四大新特性解析

- Real-ESRGAN: 开源项目提升图像超分辨率技术

- 植物大战僵尸杂交版v2.0.88:新元素新挑战

- 掌握数据分析核心模型,预测未来不是梦

- Android平台蓝牙HC-06/08模块数据交互技巧

- Python源码分享:计算100至200之间的所有素数

- 免费视频修复利器:Digital Video Repair

- Chrome浏览器新版本Adblock Plus插件发布

- GifSplitter:Linux下GIF转BMP的核心工具

- Vue.js开发教程:全面学习资源指南