时钟同步状态机设计:数字逻辑应用解析

版权申诉

127 浏览量

更新于2024-07-03

收藏 3.85MB PPT 举报

“数字逻辑设计及应用教学英文课件——Lec19-chap 7 seg=quential design-1.ppt”

这篇课件主要探讨的是数字逻辑设计中的时钟同步状态机设计,这是数字系统设计中的核心概念。时钟同步状态机在计算机、通信设备、嵌入式系统以及其他各种数字电路中广泛应用。

1. **时钟同步状态机分析步骤**

- **激励方程**(Excitation Equation):描述当前状态如何影响下一个状态,通常涉及到触发器的输入。

- **输出方程**(Output Equation):定义了当前状态下系统的输出。

- **转换方程**(Transition Equation):表示状态之间的转移关系,通常基于输入信号和当前状态。

- **Q*(状态的下一值)**:表示当前状态在时钟脉冲后的新值。

- **输出(Output)**:根据当前状态和输入计算得出的系统输出。

- **状态/输出表**(State/Output Table):列出所有可能的状态和对应的输出。

- **转换/输出表**(Transition/Output Table):详述状态之间的转换及其伴随的输出变化。

- **状态图**(State Diagram):图形化表示状态机的工作流程。

- **时序图**(Timing Diagram):展示信号随时间变化的图形。

2. **时钟同步状态机设计**

- **逻辑抽象**:对输入、输出和状态进行简化,以便于设计。

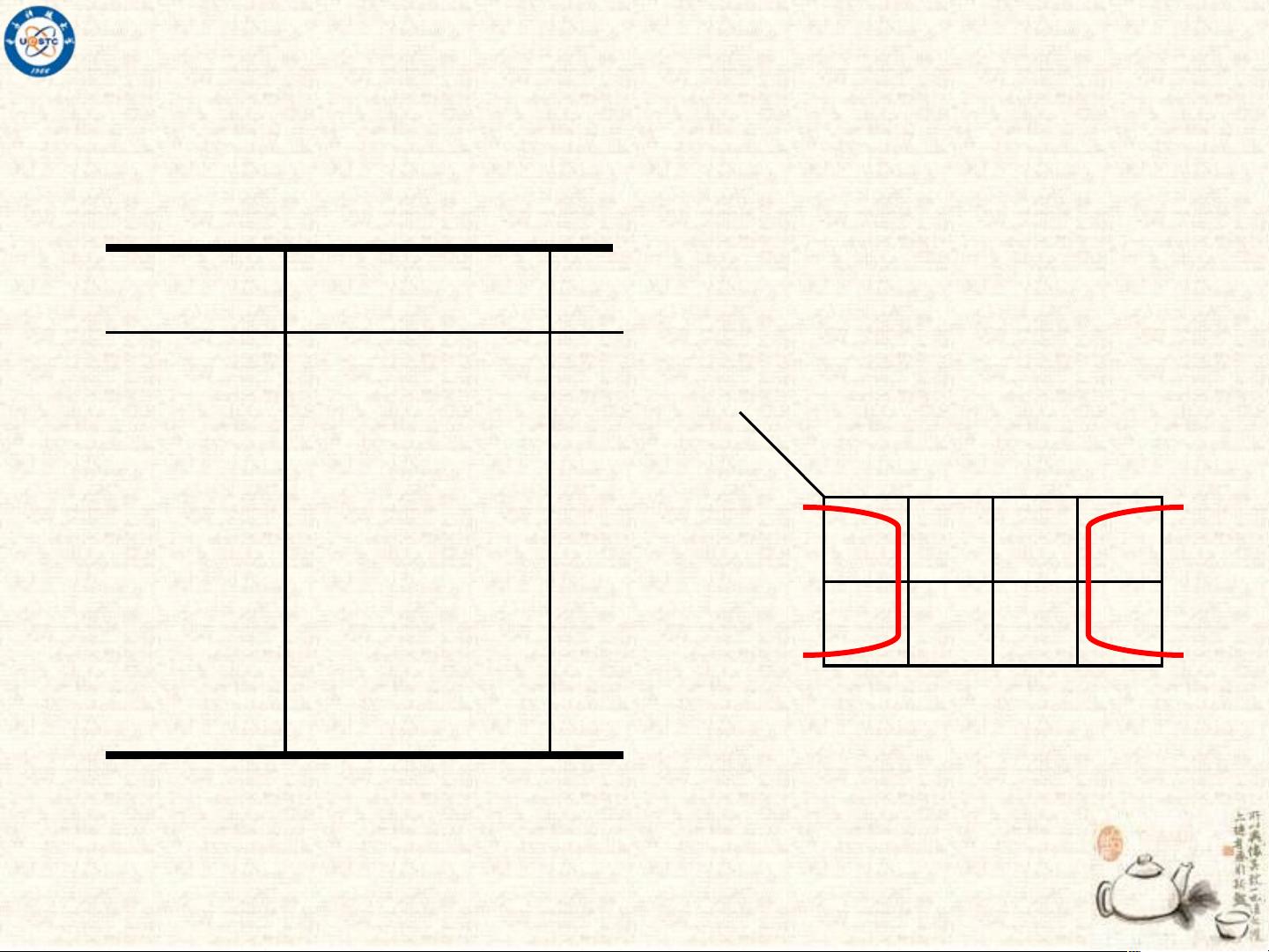

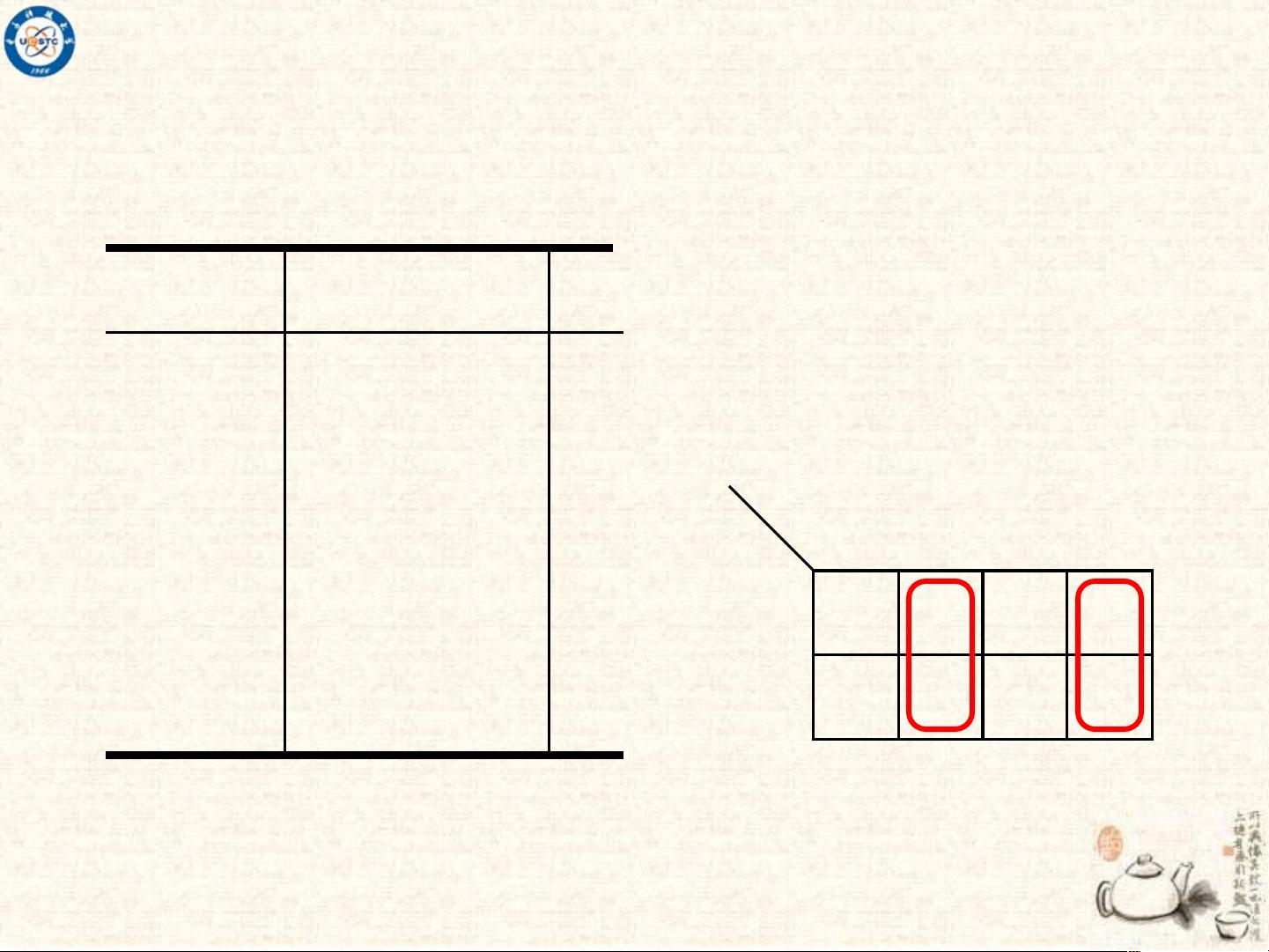

- **绘制状态图**(或构建状态/输出表):首先需要明确状态间的转换关系。

- **状态最小化**(Optional):通过状态合并减少状态机的复杂性。

- **状态分配**:将状态分配给触发器的特定组合,确保所有可能的状态都能被唯一表示。

- **创建转换/输出表**:记录所有可能的输入、状态转换及相应的输出。

- **导出转换方程和输出方程**:根据转换/输出表来确定系统的逻辑函数。

- **选择触发器**(FF Choose):根据设计需求选择适合的存储元件,如D型触发器、JK触发器等。

在数字逻辑设计中,理解并熟练掌握时钟同步状态机的设计和分析方法至关重要,因为它们是构建复杂数字系统的基础,例如控制器、计数器、数据路径等。通过对状态机的深入理解,可以更有效地实现逻辑功能,并优化系统性能。

2024-10-14 上传

2024-10-14 上传

智慧安全方案

- 粉丝: 3789

- 资源: 59万+

最新资源

- 前端面试必问:真实项目经验大揭秘

- 永磁同步电机二阶自抗扰神经网络控制技术与实践

- 基于HAL库的LoRa通讯与SHT30温湿度测量项目

- avaWeb-mast推荐系统开发实战指南

- 慧鱼SolidWorks零件模型库:设计与创新的强大工具

- MATLAB实现稀疏傅里叶变换(SFFT)代码及测试

- ChatGPT联网模式亮相,体验智能压缩技术.zip

- 掌握进程保护的HOOK API技术

- 基于.Net的日用品网站开发:设计、实现与分析

- MyBatis-Spring 1.3.2版本下载指南

- 开源全能媒体播放器:小戴媒体播放器2 5.1-3

- 华为eNSP参考文档:DHCP与VRP操作指南

- SpringMyBatis实现疫苗接种预约系统

- VHDL实现倒车雷达系统源码免费提供

- 掌握软件测评师考试要点:历年真题解析

- 轻松下载微信视频号内容的新工具介绍