USB3.0发送电路设计:多相位技术与Verilog HDL实现

137 浏览量

更新于2024-09-01

收藏 390KB PDF 举报

"基于多相位技术的USB3.0发送电路设计"

USB3.0是一种高速串行传输接口,自1995年的USB1.0版本以来,其传输速率经历了多次提升,到了USB3.0(SuperSpeed)阶段,速度达到了5Gb/s,远超USB2.0的480Mb/s。设计USB3.0发送电路面临的主要挑战是高I/O转换速率和低功耗。为了应对这些挑战,本文提出了一种基于多相位技术的USB3.0发送电路设计。

设计中,使用Verilog HDL(硬件描述语言)来描述电路,这是一种广泛用于数字系统设计的编程语言,能精确地表示数字逻辑和系统行为。在Xilinx的ISE(Integrated Synthesis Environment)平台上,对电路各模块进行了编译和仿真,以验证设计的正确性和性能。多相位技术在电路设计中的应用旨在平衡电路的复杂度、实用性和功耗。

发送电路的功耗分析是设计的关键部分。CMOS(互补金属氧化物半导体)工艺是数字集成电路的基础,其功耗与工作频率、电源电压和负载电容有关。降低功耗的策略包括降低电源电压、减小负载电容或降低工作频率。在USB3.0高速运行的场景下,由于供电电压和工艺固定,降低工作频率成为首选的节能手段。

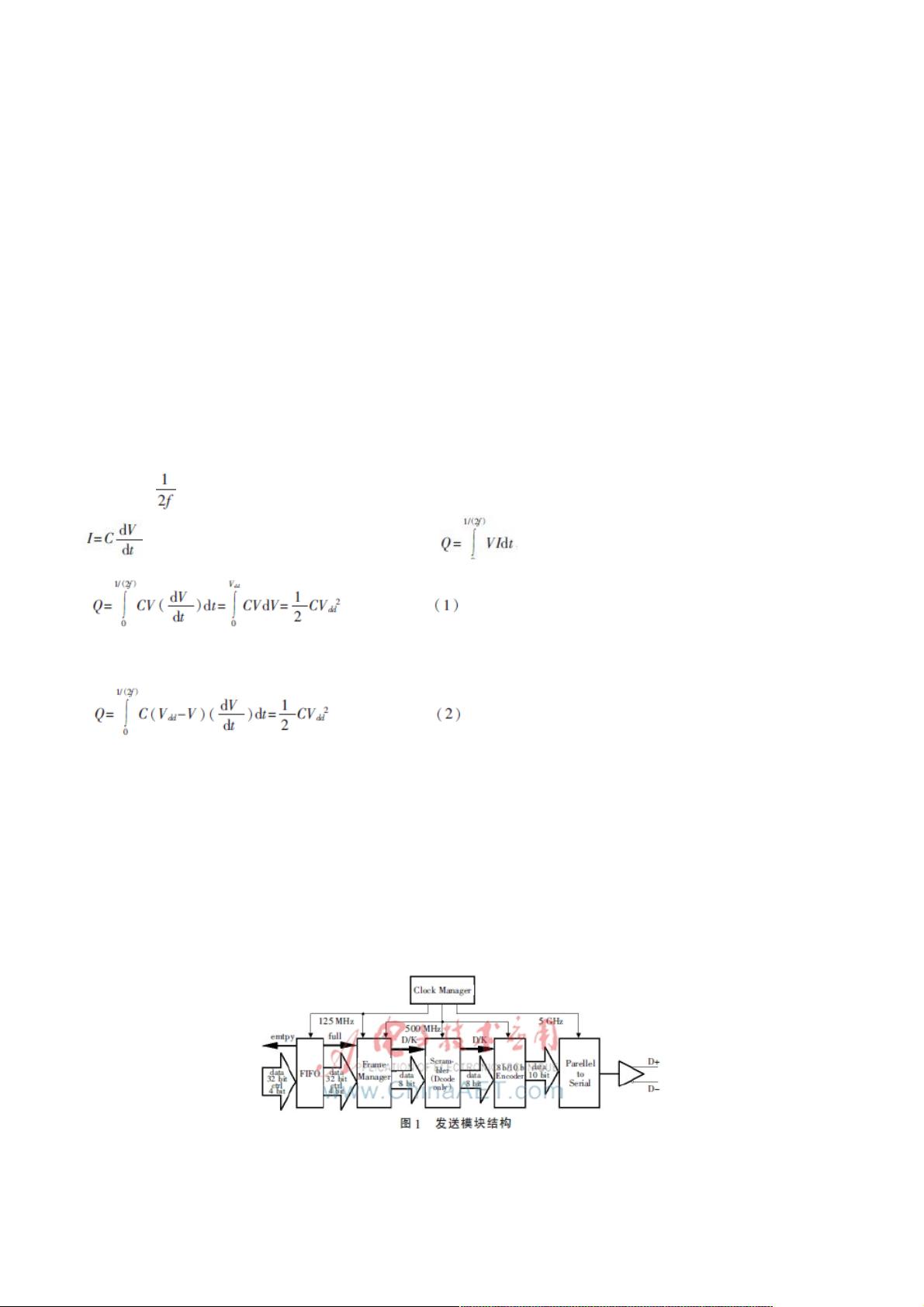

发送电路的结构如图1所示,它接收36位宽度的数据输入,包括32位有效数据和4位附加信息。电路通常包含预编码、时钟恢复、均衡、差分驱动等关键模块,这些模块共同协作确保数据的准确传输。多相位技术的应用可能体现在时钟恢复和预编码阶段,通过使用多个相位的时钟信号,可以有效地降低内部器件的工作频率,提高时钟利用率,从而达到降低功耗的目的。

预编码是为了纠正数据中的错误模式,提高信号质量。时钟恢复则是从接收到的信号中提取同步时钟,这是高速串行通信中必不可少的部分。均衡器则用于调整信号的幅度和相位,以适应信道的特性,确保数据在传输过程中的完整性。最后,差分驱动将数字信号转换成差分模拟信号,以减少干扰并提高信号的传输距离。

仿真结果表明,采用多相位技术设计的USB3.0发送电路能够满足数据发送的准确性和时序要求。通过对比验证,证明了这种方法的有效性。仿真波形图揭示了电路在不同阶段的信号行为,帮助工程师理解电路的工作原理和性能。

本文提出的方法成功地解决了USB3.0高速发送电路设计中的关键问题,实现了高效、低功耗的数据传输。多相位技术的应用为其他高速串行接口设计提供了参考和启示,对于推动高速通信技术的发展具有重要意义。

151 浏览量

146 浏览量

993 浏览量

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

weixin_38580959

- 粉丝: 3

最新资源

- 掌握PerfView:高效配置.NET程序性能数据

- SQL2000与Delphi结合的超市管理系统设计

- 冲压模具设计的高效拉伸计算器软件介绍

- jQuery文字图片滚动插件:单行多行及按钮控制

- 最新C++参考手册:包含C++11标准新增内容

- 实现Android嵌套倒计时及活动启动教程

- TMS320F2837xD DSP技术手册详解

- 嵌入式系统实验入门:掌握VxWorks及通信程序设计

- Magento支付宝接口使用教程

- GOIT MARKUP HW-06 项目文件综述

- 全面掌握JBossESB组件与配置教程

- 古风水墨风艾灸养生响应式网站模板

- 讯飞SDK中的音频增益调整方法与实践

- 银联加密解密工具集 - Des算法与Bitmap查看器

- 全面解读OA系统源码中的权限管理与人员管理技术

- PHP HTTP扩展1.7.0版本发布,支持PHP5.3环境