POWER DOWN

HIGH-IMPEDANCE MODE

FAILSAFE BIASING FOR THE SN65LV1224B

SN65LV1023A-EP

SN65LV1224B-EP

SGLS358 – SEPTEMBER 2006

FUNCTIONAL DESCRIPTION (continued)

Once the deserializer has synchronized to the serializer, the LOCK pin transitions low. The deserializer locks to

the embedded clock and uses it to recover the serialized data. ROUT data is valid when LOCK is low, otherwise

R

OUT0

–R

OUT9

is invalid. The R

OUT0

–R

OUT9

data is strobed out by RCLK. The specific RCLK edge polarity to be

used is selected by the RCLK_R/F input. The R

OUT0

–R

OUT9

, LOCK and RCLK outputs can drive a maximum of

three CMOS input gates (15-pF load total for all three) with a 66-MHz clock.

When no data transfer is required, the power-down mode can be used. The serializer and deserializer use the

power-down state, a low-power sleep mode, to reduce power consumption. The deserializer enters power down

when you drive PWRDN and REN low. The serializer enters power down when you drive PWRDN low. In power

down, the PLL stops and the outputs enter a high-impedance state, which disables load current and reduces

supply current to the milliampere range. To exit power down, you must drive the PWRDN pin high.

Before valid data exchanges between the serializer and deserializer can resume, you must reinitialize and

resynchronize the devices to each other. Initialization of the serializer takes 1026 TCLK cycles. The deserializer

initialize and drives LOCK high until lock to the LVDS clock occurs.

The serializer enters the high-impedance mode when the DEN pin is driven low. This puts both driver output

pins (DO+ and DO–) into a high-impedance state. When you drive DEN high, the serializer returns to the

previous state, as long as all other control pins remain static (SYNC1, SYNC2, PWRDN, TCLK_R/ F). When the

REN pin is driven low, the deserializer enters high-impedance mode. Consequently, the receiver output pins

R

OUT0

–R

OUT9

) and RCLK are placed into the high-impedance state. The LOCK output remains active, reflecting

the state of the PLL.

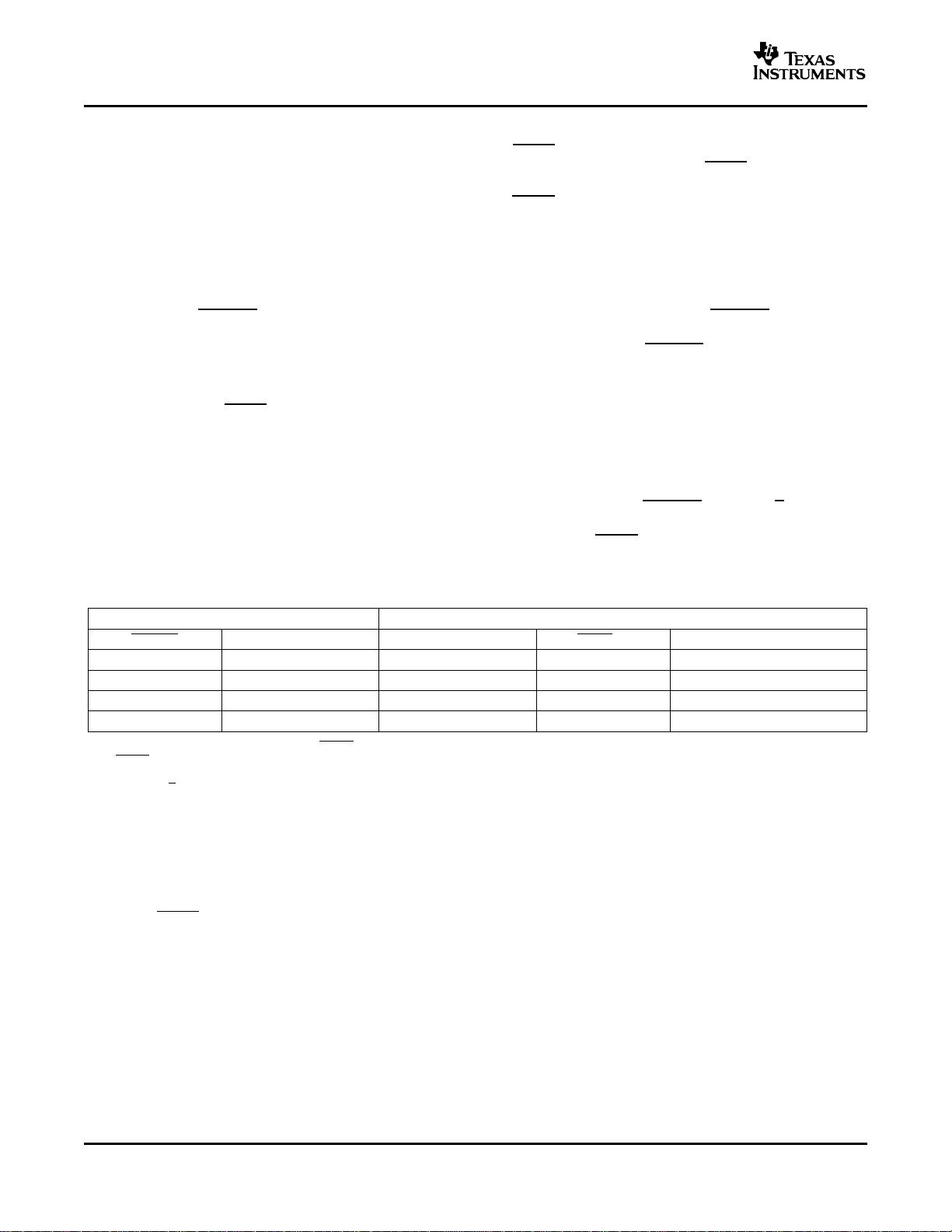

Deserializer Truth Table

INPUTS OUTPUTS

PWRDN REN ROUT(0:9)

(1)

LOCK

(2)

RCLK

(1) (3)

H H Z H Z

H H Active L Active

L X Z Z Z

H L Z Active Z

(1) ROUT and RCLK are 3-stated when LOCK is asserted high.

(2) LOCK output reflects the state of the deserializer with regard to the selected data stream.

(3) RCLK active indicates the RCLK is running if the deserializer is locked. The timing of RCLK with respect to ROUT is determined by

RCLK_R/ F.

The SN65LV1224B has an input threshold sensitivity of ± 50 mV. This allows for greater differential noise margin

in the SN65LV1224B. However, in cases where the receiver input is not being actively driven, the increased

sensitivity of the SN65LV1224B can pickup noise as a signal and cause unintentional locking. This may occur

when the input cable is disconnected. The SN65LV1224B has an on-chip fail-safe circuit that drives the serial

input and LOCK signal high. The response time of the fail-safe circuit depends on interconnect characteristics.

6

Submit Documentation Feedback