ispLEVER7.111使用入门指南

需积分: 44 166 浏览量

更新于2024-07-22

1

收藏 2.91MB PDF 举报

"ispLEVER7.111 使用指南主要针对初次或不常用 ispLEVER 软件的工程设计人员,旨在帮助他们理解和掌握软件的各项功能,包括设计流程、工具使用及报告解读。本指南通过一个简单的Verilog计数器设计示例,涵盖了从工程创建、PLL模块生成、信号锁定、时序分析到功耗评估和仿真的全过程。"

ispLEVER 是一款用于Lattice FPGA 设计的集成开发环境,版本7.111 提供了对Verilog HDL的支持和一系列设计工具。以下是关于ispLEVER 使用的关键知识点:

1. **工程创建与管理**:使用ispLEVER 创建一个新的Verilog 工程,选择目标Lattice FPGA 器件,并通过Project Navigator 添加Verilog源代码,组织工程目录。

2. **PLL模块生成**:利用IPexpress 和Text Editor,可以生成并集成sysCLOCK PLL模块,以实现时钟同步和频率转换。

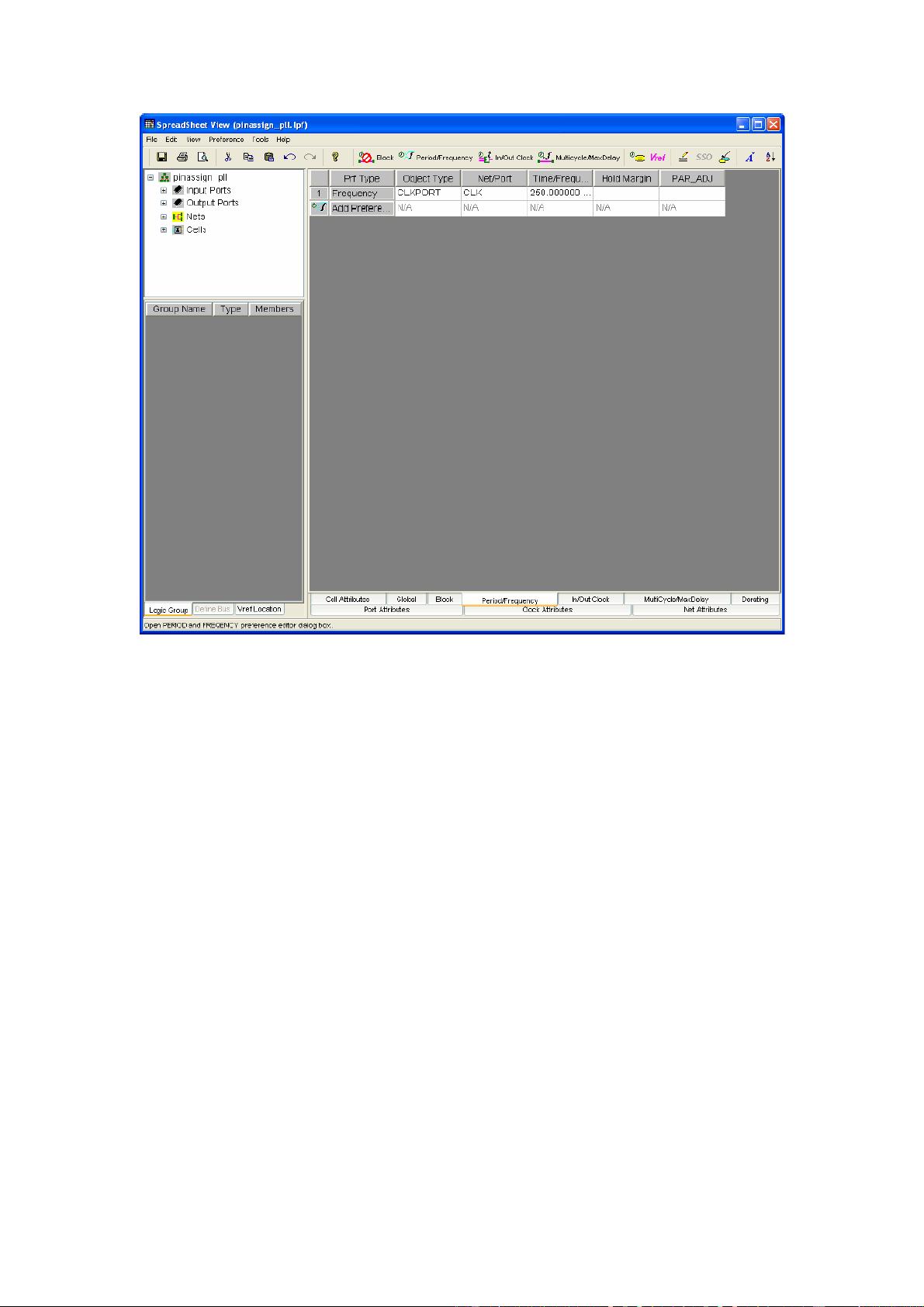

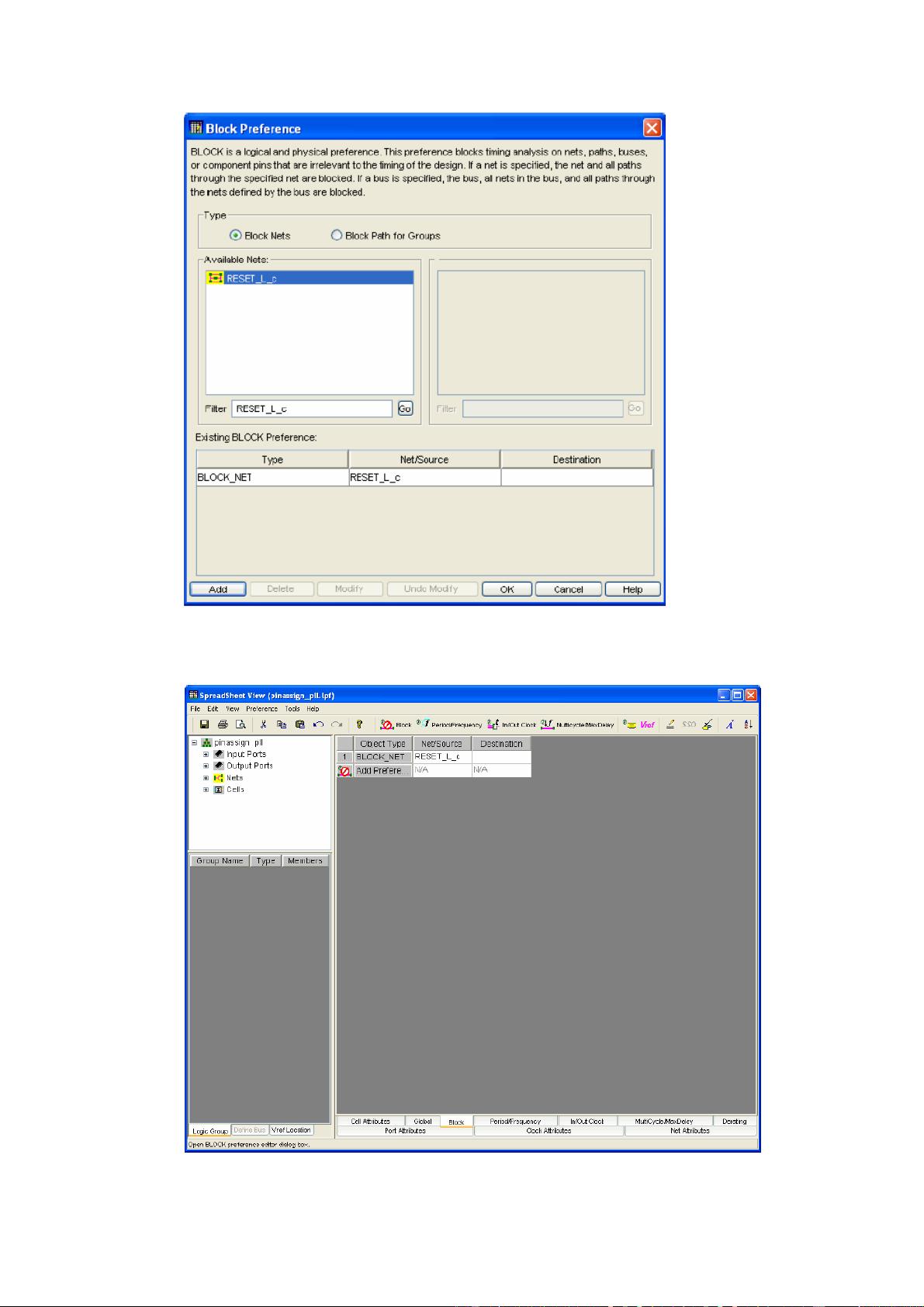

3. **设计约束与布局**:DesignPlanner 允许指定信号频率周期和时钟到输出的时间,同时锁定信号至器件管脚,确保满足系统需求。

4. **设计实现**:包括映射(Mapping)、布局(Placing)和布线(Routing)等步骤,Project Navigator 提供结果报告以检查设计质量。

5. **时序分析**:通过静态时序分析报告,理解设计的时序性能,根据需要调整设计以满足时序约束。

6. **约束条件优化**:根据设计性能要求,修改和重新设置约束条件,优化资源利用。

7. **设计检查**:DesignPlanner 可用于检查器件实现情况,分析布线阻塞和PFU(Programmable Function Unit)利用率。

8. **功耗评估**:使用PowerCalculator 工具评估设计的功耗,以便进行低功耗优化。

9. **仿真验证**:ispLEVER 提供了仿真工具,用于验证设计的功能正确性和性能特性。

通过学习和实践这个指南中的步骤,工程师能够掌握ispLEVER 的基本操作,进而在实际项目中更有效地利用Lattice FPGA 的资源,实现高性能和低功耗的设计。对于复杂的、时序要求严格的设计,需要进一步深入学习和掌握更高级的工具和技巧。

2015-11-19 上传

2017-12-27 上传

2023-05-14 上传

2023-08-01 上传

2023-05-13 上传

2020-12-04 上传

2022-07-14 上传

beijibing00002003

- 粉丝: 0

- 资源: 3

最新资源

- 磁性吸附笔筒设计创新,行业文档精选

- Java Swing实现的俄罗斯方块游戏代码分享

- 骨折生长的二维与三维模型比较分析

- 水彩花卉与羽毛无缝背景矢量素材

- 设计一种高效的袋料分离装置

- 探索4.20图包.zip的奥秘

- RabbitMQ 3.7.x延时消息交换插件安装与操作指南

- 解决NLTK下载停用词失败的问题

- 多系统平台的并行处理技术研究

- Jekyll项目实战:网页设计作业的入门练习

- discord.js v13按钮分页包实现教程与应用

- SpringBoot与Uniapp结合开发短视频APP实战教程

- Tensorflow学习笔记深度解析:人工智能实践指南

- 无服务器部署管理器:防止错误部署AWS帐户

- 医疗图标矢量素材合集:扁平风格16图标(PNG/EPS/PSD)

- 人工智能基础课程汇报PPT模板下载