FPGA设计关键问题探讨与解决方案

需积分: 9 104 浏览量

更新于2024-10-18

收藏 67KB DOC 举报

"FPGA设计关键问题研究"

在FPGA(Field Programmable Gate Array)设计中,面临的关键问题和挑战直接影响到数字系统的性能、可靠性和设计效率。本文将深入探讨这些问题,提供相应的解决策略。

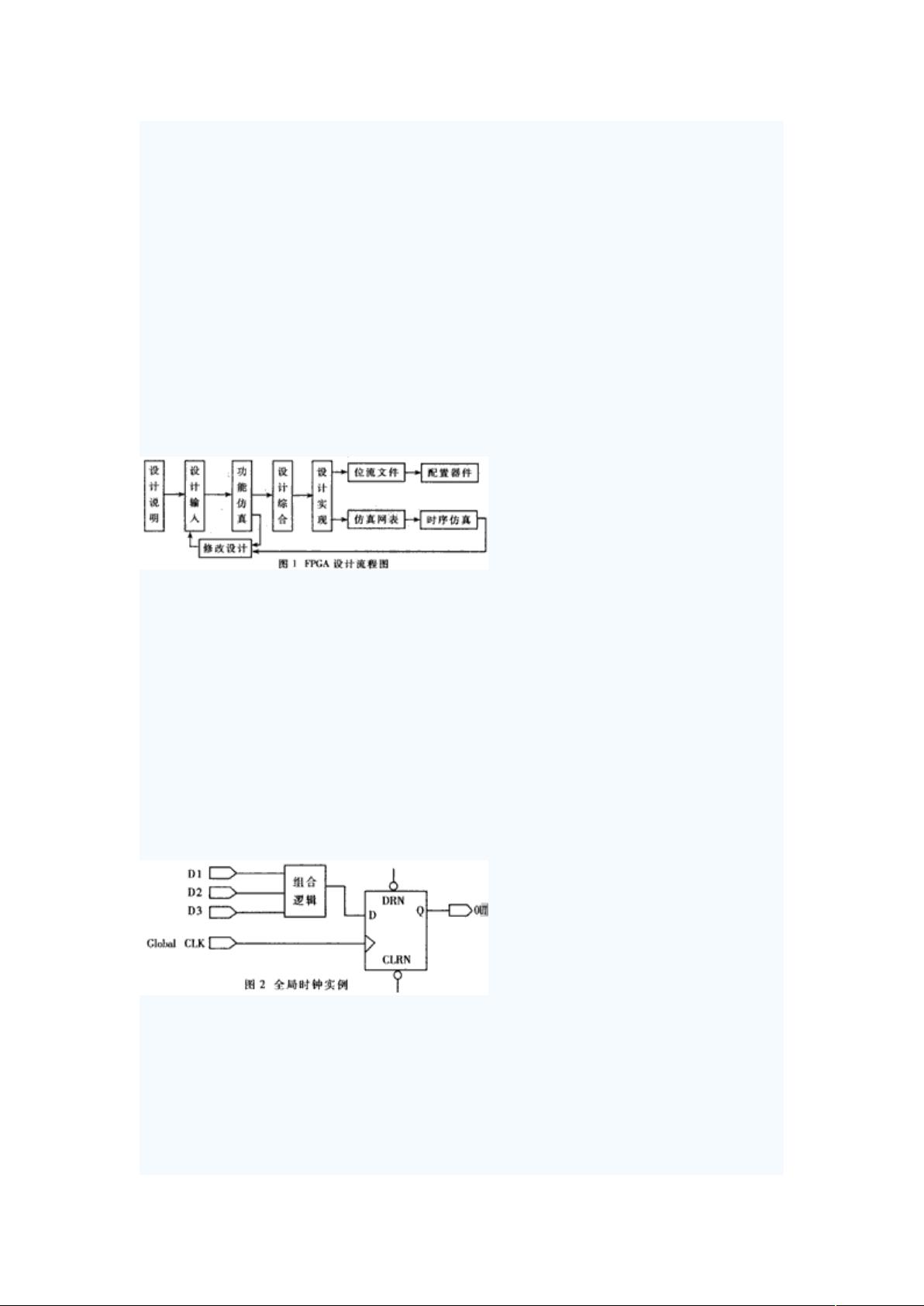

首先,FPGA设计流程是设计者必须遵循的步骤,通常采用自顶向下的方法。这一过程包括设计说明书的编写、设计输入、逻辑综合、功能仿真、逻辑实现、时序仿真和最终的配置下载。每个阶段都有其特定的目标和工具,确保设计的正确性和优化。

时钟设计是FPGA设计的核心问题之一,因为它直接影响电路的同步和性能。全局时钟是最简单且可靠的,由专用的全局时钟输入引脚驱动,确保所有时序器件在同一时刻翻转。然而,对于某些复杂设计,可能需要门控时钟,即通过组合逻辑控制时钟的开关。门控时钟的可靠性取决于驱动时钟的逻辑结构,通常限制为单一的“与”或“或”门,并确保满足建立和保持时间。在多时钟系统中,不同域之间的同步和接口设计变得尤为关键,需要精心的时钟域交叉(CDC)处理以避免数据错误。

其次是布线资源的优化。FPGA内部的连线资源有限,合理分配和使用这些资源对设计速度和面积有显著影响。设计者需要通过逻辑优化、时钟树综合(CTS)和路由预分配等手段来最大化性能。

再者,电源管理和功耗是另一个重要问题。FPGA的动态和静态功耗都需要考虑,尤其是在便携式设备中。设计者可以通过低功耗设计技术,如动态电压频率调整(DVFS)、时钟门控和部分重配置来降低功耗。

另外,错误检测和纠正也是必不可少的。FPGA设计中的错误可能来源于硬件故障、设计缺陷或制造过程中的变异。采用内置自我测试(BIST)和冗余逻辑可以增强系统的鲁棒性。

仿真和验证是确保设计正确性的关键环节。功能仿真用于检查逻辑功能,而时序仿真则评估设计在实际时钟速度下的行为。仿真需要覆盖所有可能的输入状态和边界条件,以确保设计的健壮性。

最后,知识产权(IP)的复用和集成也是FPGA设计中的重要方面。利用现成的IP核可以节省设计时间和成本,但需要考虑兼容性、互操作性和知识产权保护。

FPGA设计涉及多个相互关联的问题,包括时钟设计、资源管理、功耗控制、错误检测、仿真验证和IP复用。理解和解决这些问题对于成功实现高性能、低功耗且可靠的FPGA系统至关重要。通过不断学习和实践,设计者可以掌握这些关键技术,提升FPGA设计的效率和质量。

2013-06-02 上传

2020-12-09 上传

2023-02-27 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

2009-08-25 上传

2020-10-21 上传

luckmdw

- 粉丝: 0

- 资源: 8

最新资源

- SSM动力电池数据管理系统源码及数据库详解

- R语言桑基图绘制与SCI图输入文件代码分析

- Linux下Sakagari Hurricane翻译工作:cpktools的使用教程

- prettybench: 让 Go 基准测试结果更易读

- Python官方文档查询库,提升开发效率与时间节约

- 基于Django的Python就业系统毕设源码

- 高并发下的SpringBoot与Nginx+Redis会话共享解决方案

- 构建问答游戏:Node.js与Express.js实战教程

- MATLAB在旅行商问题中的应用与优化方法研究

- OMAPL138 DSP平台UPP接口编程实践

- 杰克逊维尔非营利地基工程的VMS项目介绍

- 宠物猫企业网站模板PHP源码下载

- 52简易计算器源码解析与下载指南

- 探索Node.js v6.2.1 - 事件驱动的高性能Web服务器环境

- 找回WinSCP密码的神器:winscppasswd工具介绍

- xctools:解析Xcode命令行工具输出的Ruby库