JESD204B接口标准与高速ADC应用解析

需积分: 5 24 浏览量

更新于2024-07-09

1

收藏 2.61MB PDF 举报

"这份文档是普渡大学关于JESD204B接口标准的介绍,主要用于高速ADC(模拟到数字转换器)接口的应用和挑战。文档由Matthew Jones在2016年的8th INFIERI Workshop – Fermilab活动中发表,详细探讨了JESD204B标准在不同领域的应用,如医疗成像、数字示波器、软件定义无线电和合成孔径雷达等。JESD204B标准旨在解决超过200 MSPS(每秒百万样本)高速ADC应用中的问题,提供多个供应商遵循的明确标准,促进应用开发。"

正文:

JESD204B是一个高速模拟到数字转换器(ADC)接口标准,由JEDEC固态技术协会制定,主要针对高速数据转换系统的需求。该标准在2016年的普渡大学研讨会上被详细讨论,强调了其在多个领域的广泛应用,包括但不限于医学成像中的超声波设备、数字示波器中用于光电倍增管波形数字化、软件定义无线电以及合成孔径雷达系统。

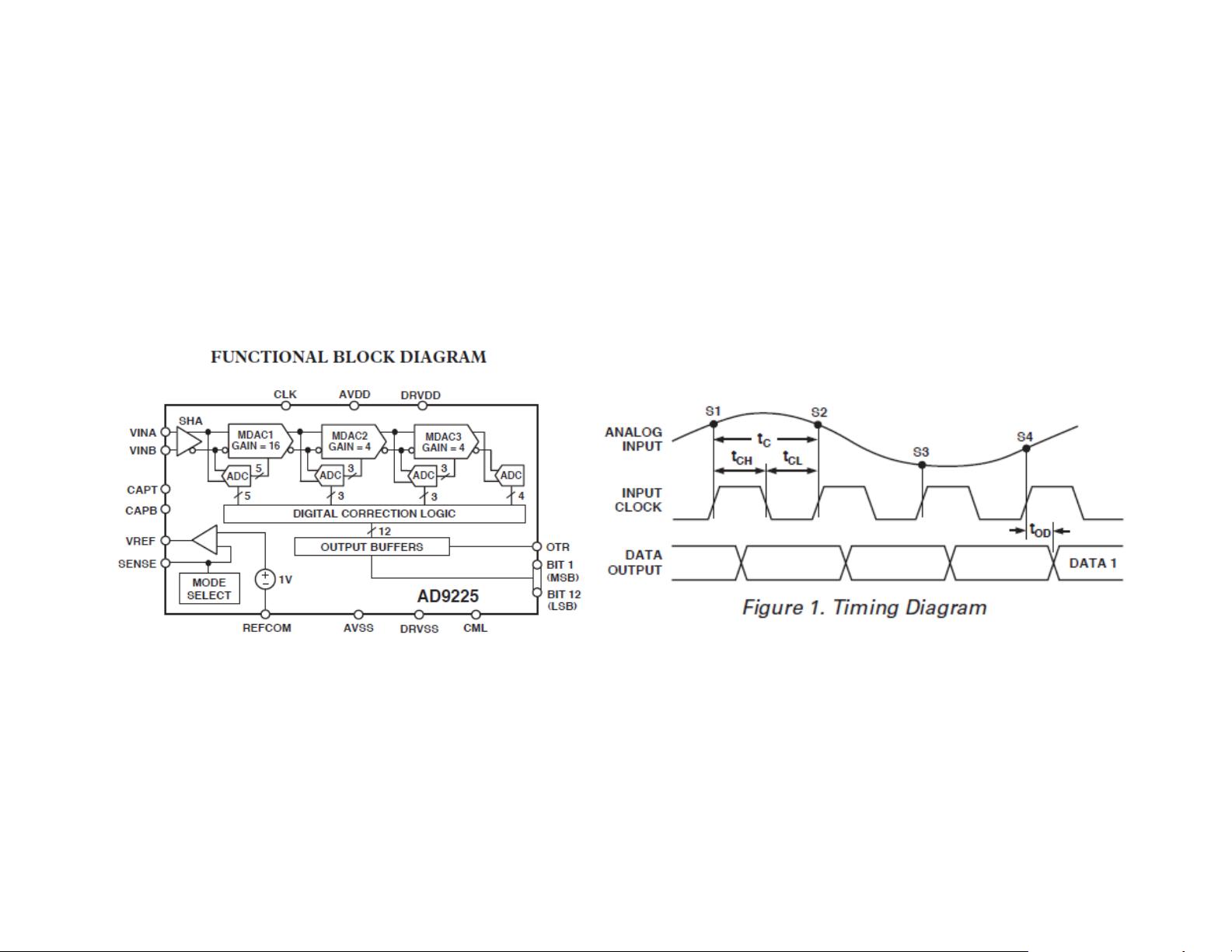

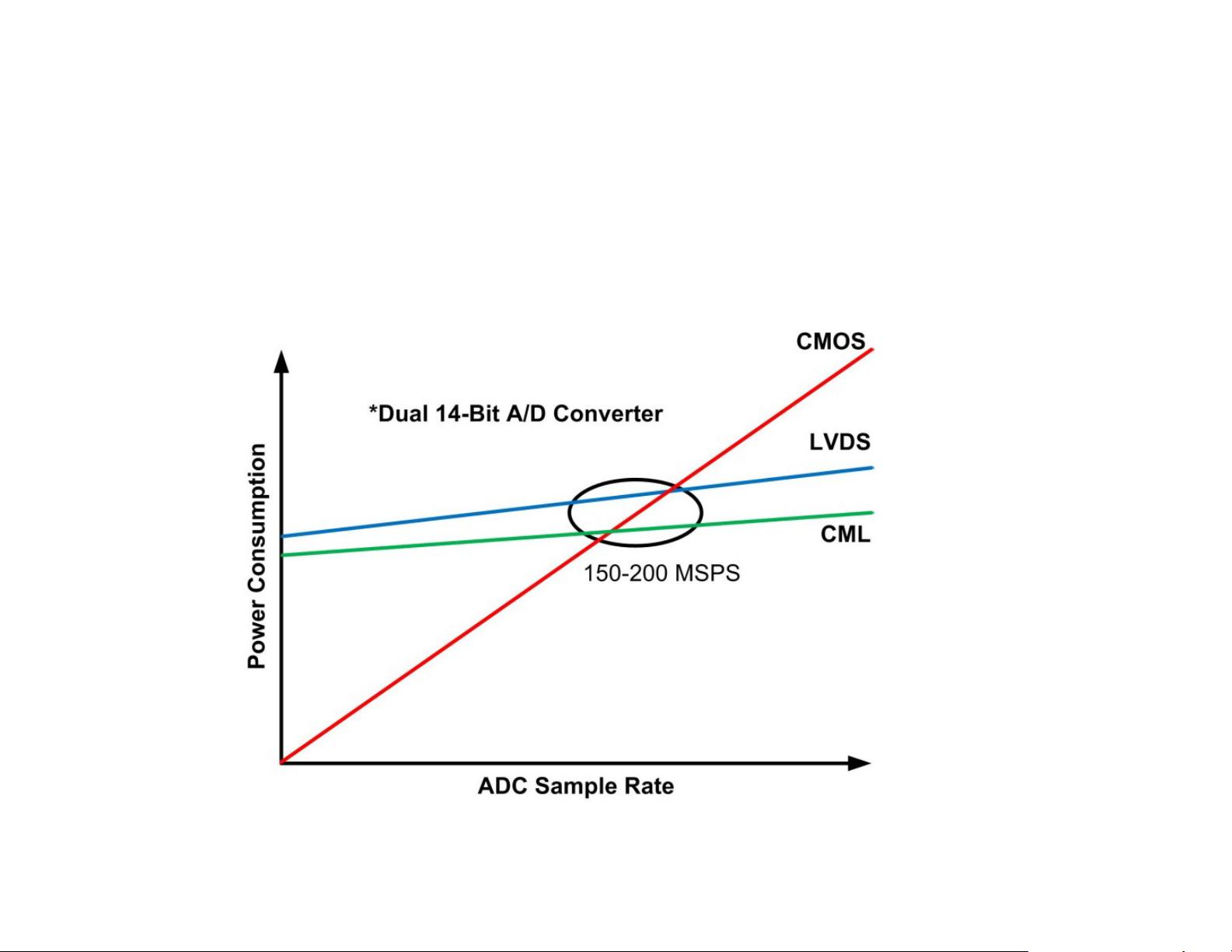

在高采样速率(大于200 MSPS)的场景下,传统的并行接口开始面临挑战。例如,AD9225(约1998年)是一个单通道、12位、25 MSPS的5V CMOS ADC,当采样速率超过100 MSPS时,由于噪声和信号偏斜问题,平行接口的设计变得复杂。此外,随着速度的提升,功耗也是一个不容忽视的因素。

为了解决这些问题,JESD204B引入了低电压差分信号(LVDS)和转发时钟输出,如AD9634(约2011年)所示,这是一个单通道、12位、250 MSPS的1.8V CMOS ADC。尽管这些改进减少了电压和降低了功耗,但信号偏斜仍然是一个潜在问题。JESD204B标准通过提供一种串行化的方法,解决了高速ADC接口中的信号完整性、时钟同步和功耗问题,使得多供应商间的互操作性成为可能。

JESD204B标准的关键特性包括:

1. **串行化数据传输**:通过将并行数据转换为串行流,减少信号偏斜和噪声的影响。

2. **时钟管理**:采用同步时钟和时钟恢复机制,确保数据在接收端的精确对齐。

3. **低电压差分信号**:使用LVDS降低功耗和提高信号质量。

4. **错误检测与纠正**:包含内置的校验码和错误检测机制,以增强系统的可靠性。

5. **多设备同步**:支持多个ADC或数字信号处理器(DSP)之间的同步,对于需要多通道同步的应用至关重要。

JESD204B接口标准为高速ADC应用提供了一种高效、可靠和标准化的解决方案,推动了高速数据转换系统的进步,尤其是在需要高速采样和高精度测量的领域。通过遵循这一标准,开发者可以简化设计过程,减少开发时间,并确保不同供应商组件之间的兼容性。

2022-07-14 上传

2022-07-15 上传

2021-10-10 上传

2021-09-30 上传

2021-09-30 上传

2022-07-14 上传

2019-12-10 上传

2019-07-17 上传

2021-10-10 上传

mplargeangel

- 粉丝: 0

- 资源: 1

最新资源

- JavaScript实现的高效pomodoro时钟教程

- CMake 3.25.3版本发布:程序员必备构建工具

- 直流无刷电机控制技术项目源码集合

- Ak Kamal电子安全客户端加载器-CRX插件介绍

- 揭露流氓软件:月息背后的秘密

- 京东自动抢购茅台脚本指南:如何设置eid与fp参数

- 动态格式化Matlab轴刻度标签 - ticklabelformat实用教程

- DSTUHack2021后端接口与Go语言实现解析

- CMake 3.25.2版本Linux软件包发布

- Node.js网络数据抓取技术深入解析

- QRSorteios-crx扩展:优化税务文件扫描流程

- 掌握JavaScript中的算法技巧

- Rails+React打造MF员工租房解决方案

- Utsanjan:自学成才的UI/UX设计师与技术博客作者

- CMake 3.25.2版本发布,支持Windows x86_64架构

- AR_RENTAL平台:HTML技术在增强现实领域的应用