5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

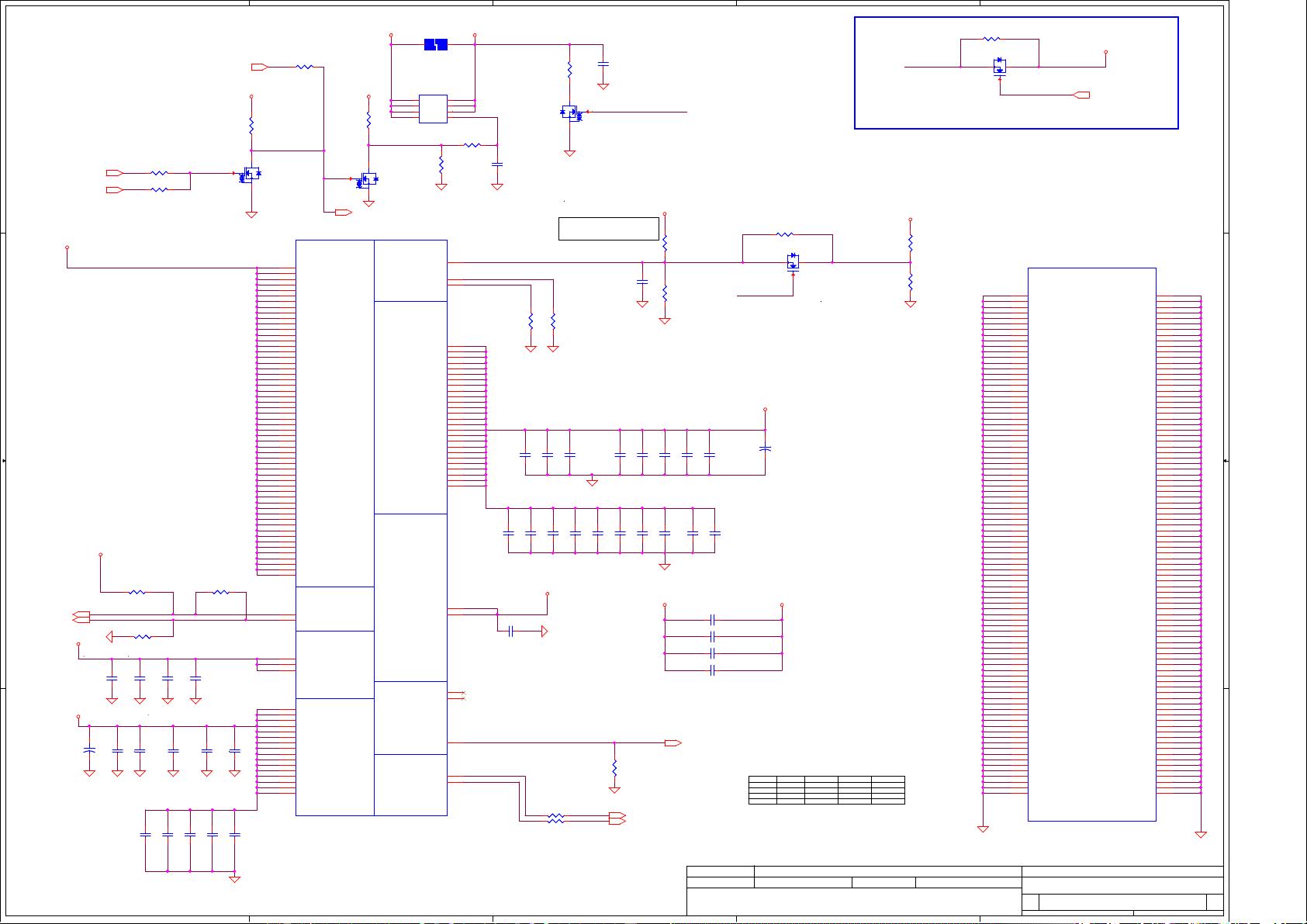

SGA00004L00

SA00001LV10

M_OD T0

DDR _A _D QS4

DDR _A _D QS# 4

DDR _A _D QS# 2

DDR _A _DQS# 7

DDR _A _DQS7

DDR 3_ DR AMRS T#

DDR _A _D QS# 0

DDR _A _BS0

DDR _A _BS1

DDR _A _BS2

M_OD T0

M_CL K_ DDR0

DDR _C KE0_D IMMA

M_CL K_ DDR#0

DDR _C S0 _DI MMA#

DDR _A _D QS# 5

DDR _A _D QS5

DDR _A _BS2

DDR _A _BS0

M_CL K_ DDR0

DDR _C KE0_D IMMA

M_CL K_ DDR#0

M_OD T0

DDR _A _BS1

DDR _A _MA3

DDR _A _MA1

DDR _A _W E#

DDR _A _CAS#

DDR _A _RAS#

DDR _C S0_DI MMA#

DDR _A _MA12

DDR _A _MA10

DDR _A _MA9

DDR _A _MA8

DDR _A _MA5

DDR _A _MA6

DDR _A _MA4

DDR _A _MA0

DDR _A _MA2

DDR _A _MA13

DDR _A _MA11

DDR _A _MA7

DDR _A _BS1

DDR _A _R AS#

DDR _A _D QS# 3

DDR _A _W E#

DDR _A _D QS# [0..7 ]

DDR _A _D QS[0 ..7]

DDR _A _MA[0..15 ]

DDR _A _D [0..63 ]

DDR _A _MA8

DDR _A _MA5

DDR _A _MA3

DDR _A _MA1

DDR _A _MA2

DDR _A _MA13

DDR _A _MA12

DDR _A _MA10

DDR _A _MA9

DDR _A _MA11

DDR _A _MA7

DDR _A _MA6

DDR _A _MA4

DDR _A _MA0

DDR _A _D QS2

DDR _A _C AS#

DDR 3_ DR AMRS T#

DDR _C KE0_D IMMA

M_CL K_ DDR#0

M_OD T0

DDR _A _W E#

DDR _A _CAS#

DDR _A _RAS#

DDR _C S0_DI MMA#

M_CL K_ DDR0

DDR _A _BS1

DDR _A _BS2

DDR _A _BS0

DDR _A _BS2

DDR 3_ DR AMRS T#

+VR EF1+VR EF0

DDR _A _MA5

DDR _A _MA3

DDR _A _MA1

DDR _A _MA13

DDR _A _MA12

DDR _A _MA10

DDR _A _MA9

DDR _A _MA8

DDR _A _MA7

DDR _A _MA6

DDR _A _MA4

DDR _A _MA0

DDR _A _MA2

DDR _A _MA11

DDR _A _MA8

DDR _A _MA5

DDR _A _MA3

DDR _A _MA1

DDR _A _MA2

DDR _A _MA13

DDR _A _MA12

DDR _A _MA10

DDR _A _MA9

DDR _A _MA11

DDR _A _MA7

DDR _A _MA6

DDR _A _MA4

DDR _A _MA0

DDR _A _MA14

DDR _A _BS0

DDR _A _D QS0

DDR _A _C AS#

DDR _A _R AS#

DDR _C S0 _DI MMA#

DDR 3_ DR AMRS T#

DDR _A _W E#

M_CL K_ DDR#0

M_CL K_ DDR0

DDR _C KE0_D IMMA

DDR _A _D QS1

DDR _A _DQS# 6

DDR _A _DQS6DDR _A _D QS3

DDR _A _D QS# 1

DDR _A _MA14DDR _A _MA14

DDR _A _MA14

M_CL K_ DDR0

M_CL K_ DDR#0

SMB_ CL K_S3

SMB_ DA TA_S3

DDR _A _MA15

DDR _A _MA15

DDR _A _MA15 DDR _A _MA15

M_CL K_ DDR1

M_CL K_ DDR#1

DDR _A _D11

DDR _A _D9

DDR _A _D13

DDR _A _D14

DDR _A _D8

DDR _A _D12

DDR _A _D10

DDR _A _D15

DDR _A _D 24

DDR _A _D 25

DDR _A _D 26

DDR _A _D 27

DDR _A _D 28

DDR _A _D 29

DDR _A _D 30

DDR _A _D 31

DDR _A _D40

DDR _A _D42

DDR _A _D43

DDR _A _D44

DDR _A _D47

DDR _A _D46

DDR _A _D41

DDR _A _D45

DDR _A _D57

DDR _A _D59

DDR _A _D60

DDR _A _D63

DDR _A _D62

DDR _A _D61

DDR _A _D56

DDR _A _D58

DDR _A _D0

DDR _A _D1

DDR _A _D7

DDR _A _D6

DDR _A _D5

DDR _A _D4

DDR _A _D3

DDR _A _D2

DDR _A _D 16

DDR _A _D 19

DDR _A _D 20

DDR _A _D 21

DDR _A _D 23

DDR _A _D 17

DDR _A _D 18

DDR _A _D 22

DDR _A _D32

DDR _A _D33

DDR _A _D34

DDR _A _D35

DDR _A _D36

DDR _A _D38

DDR _A _D39

DDR _A _D37

DDR _A _D48

DDR _A _D50

DDR _A _D52

DDR _A _D53

DDR _A _D54

DDR _A _D55

DDR _A _D51

DDR _A _D49

DDR _A _MA2

DDR _A _MA5

M_OD T1

DDR _A _MA0

DDR _A _W E#

DDR _A _MA11

DDR _A _MA14

DDR _C S0 _DI MMA#

DDR _A _MA4

DDR _A _C AS#

DDR _A _MA12

DDR _A _MA6

DDR _A _MA7

DDR _A _MA9

DDR _A _MA10

DDR _A _MA8

DDR _A _MA13

DDR _C KE0_D IMMA

M_OD T0

DDR _A _R AS#

DDR _C S1 _DI MMA#

DDR _A _BS0

DDR _A _BS1

DDR _C KE1_D IMMA

DDR _A _BS2

DDR _A _MA1

DDR _A _MA15

DDR _A _MA3

M_OD T0[6]

DDR _C S0 _DI MMA#[6 ]

DDR _A _BS1[11,6 ]

DDR _A _R AS#[11 ,6]

DDR _A _W E#[1 1,6]

DDR _A _C AS#[11 ,6]

DDR 3_ DR AMRS T#[11,6 ]

DDR _A _BS2[11,6 ]

DDR _A _BS0[11,6 ]

DDR _A _D QS# [0..7 ][11 ,6]

DDR _A _D[0..63 ][11,6]

DDR _A _MA[0..15 ][11,6 ]

DDR _A _DQS[0 ..7][11,6 ]

DDR _C KE0_D IMMA[6]

M_CL K_ DDR0[6]

M_CL K_ DDR#0[6]

SMB_ CL K_S3 [13,2 1,3 2,35]

SMB_ DA TA_S3 [13,2 1,3 2,35 ]

M_CL K_ DDR1[11,6 ]

M_CL K_ DDR#1[11,6 ]

M_OD T1[11,6 ]

DDR _C S1 _DI MMA#[11,6 ]

DDR _C KE1_D IMMA[11,6 ]

+1.5 V +1.5 V+1.5 V

+VR EF0 +V REF 1

+1.5 V

+VR EF0 +VREF1

+1.5 V +1.5 V

+VR EF0 +VR EF1

+VR EF0

+0.7 5VS

+VR EF1 +VR EF0 +VREF1

+1.5 V

+3V S

Title

Size Doc ument Num be r Rev

Date: Shee t of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

LA-8671P_SDV

1.0

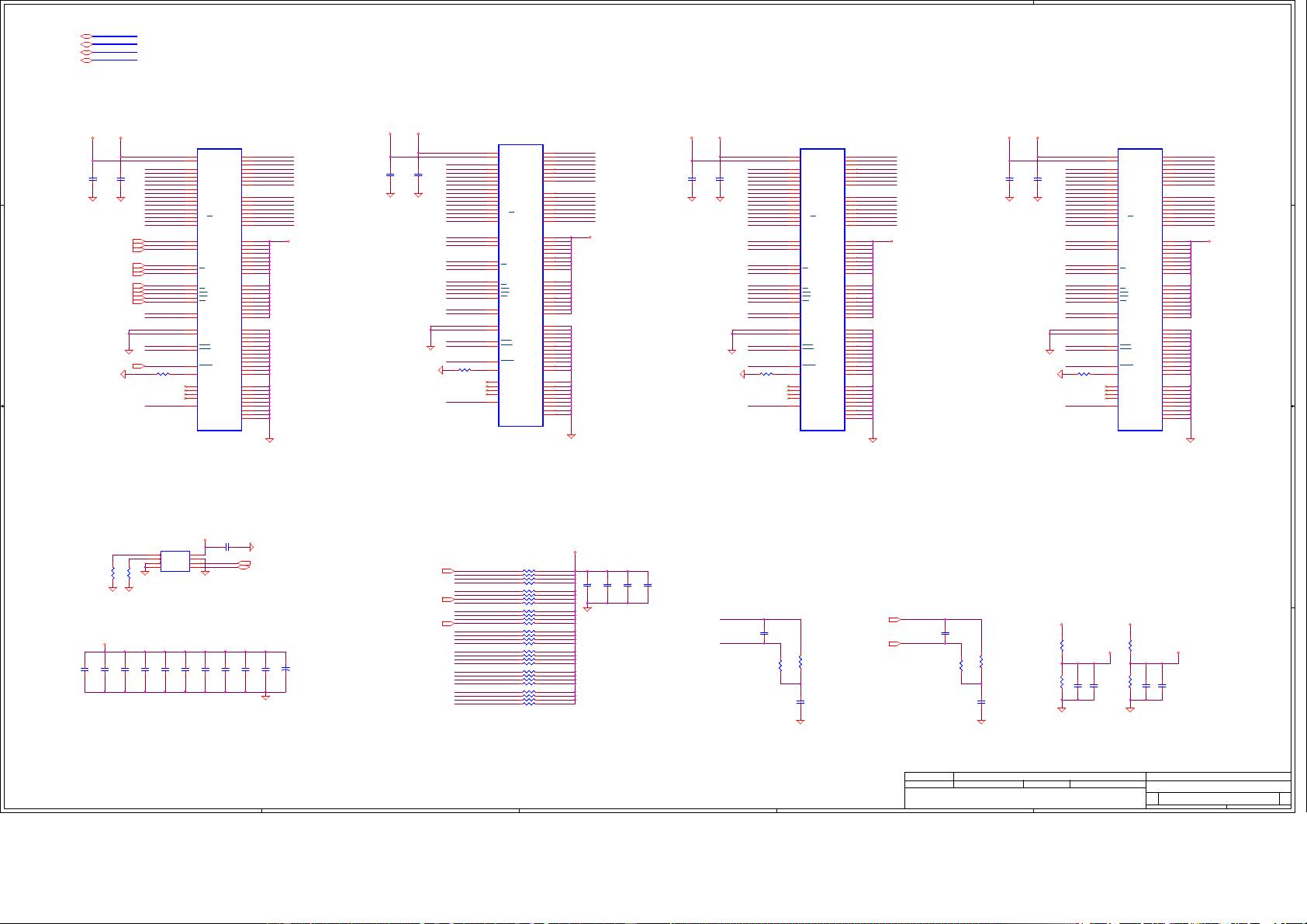

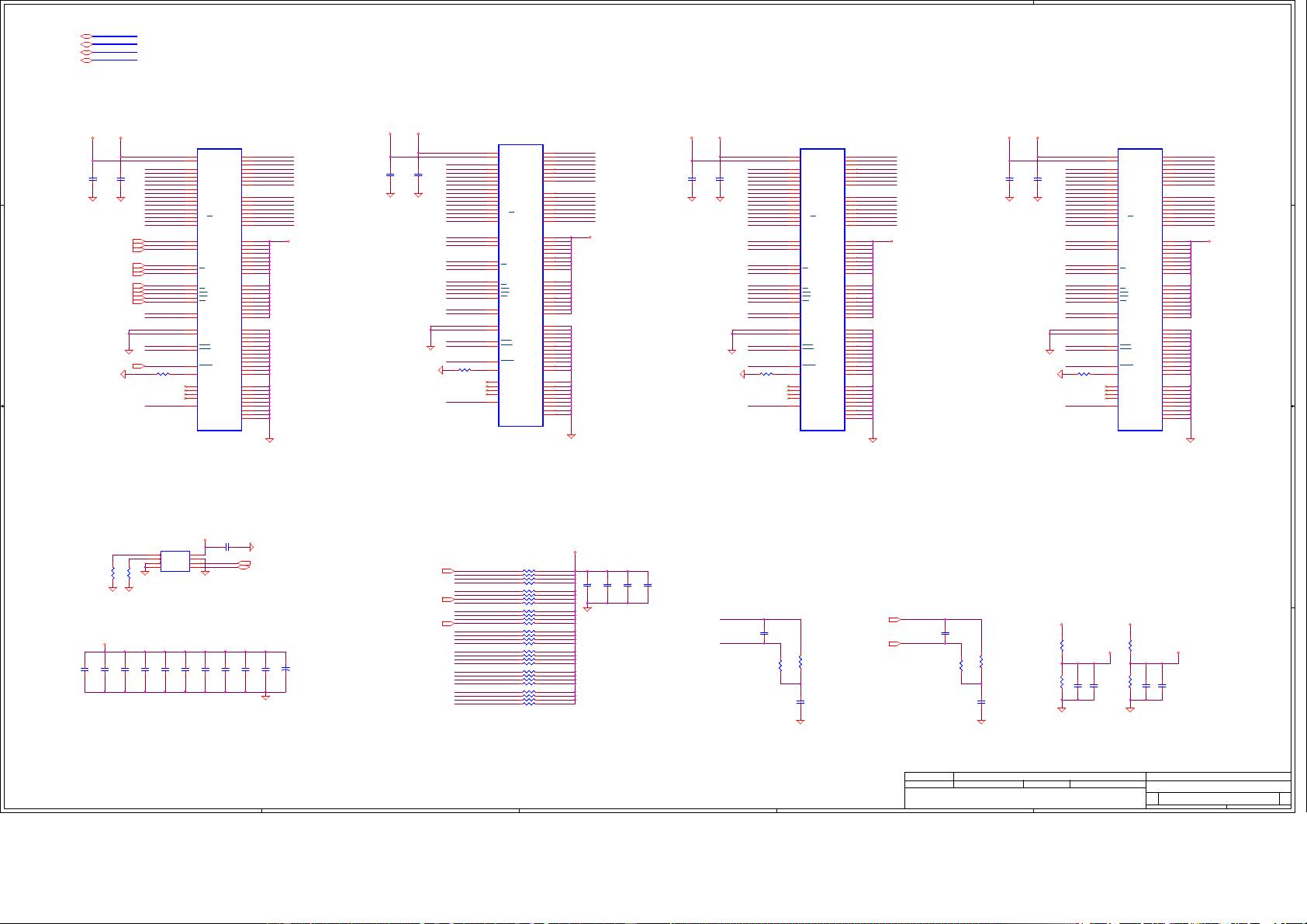

DDRIII A Chip 2Gbit X16-I

D

10 50Thursd ay, Octobe r 04 , 2012

2011/05/16 2013/05/16

Compal Electronics, Inc.

Title

Size Doc ument Num be r Rev

Date: Shee t of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

LA-8671P_SDV

1.0

DDRIII A Chip 2Gbit X16-I

D

10 50Thursd ay, Octobe r 04 , 2012

2011/05/16 2013/05/16

Compal Electronics, Inc.

Title

Size Doc ument Num be r Rev

Date: Shee t of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

LA-8671P_SDV

1.0

DDRIII A Chip 2Gbit X16-I

D

10 50Thursd ay, Octobe r 04 , 2012

2011/05/16 2013/05/16

Compal Electronics, Inc.

C52 88

2P_ 04 02 _50 V8 C

C52 88

2P_ 04 02 _50 V8 C

1

2

96-B AL L

SDR AM D DR3L

U500 7

H5TC 4G 63MFR-P BA _FBGA 96

DDR 1@

96-B AL L

SDR AM D DR3L

U500 7

H5TC 4G 63MFR-P BA _FBGA 96

DDR 1@

WE

L4

RAS

J4

CAS

K4

CS

L3

CKE

K10

CK

J8

CK

K8

DQSU

B8

BA0

M3

BA1

N9

A2

P4

A3

N3

A4

P9

A5

P3

A6

R9

A7

R3

A8

T9

A9

R4

A10/AP

L8

A11

R8

DQL0

E4

DQL1

F8

DQL2

F3

DQL3

F9

DQL4

H4

DQL5

H9

DQL6

G3

DQL7

H8

VSSQ

D2

VSS

A10

VSS

E2

VSS

B4

NC

J2

VDD

B3

VDD

D10

VDDQ

A2

VDDQ

A9

VDDQ

C2

VDDQ

C10

NC

L2

NC

J10

VDDQ

E10

ZQ

L9

RESET

T3

DQSL

F4

DMU

D4

DML

E8

VSSQ

B2

VSSQ

B10

VSSQ

D9

VSSQ

E3

DQSU

C8

VSSQ

E9

DQSL

G4

VDDQ

F2

VSSQ

F10

VSSQ

G2

VDDQ

H3

VDDQ

H10

VSSQ

G10

VREFCA

M9

VSS

G9

VDD

G8

ODT

K2

A0

N4

A1

P8

VDD

K3

A12/BC

N8

VSS

J3

VDD

K9

DQU1

C4

DQU2

C9

DQU3

C3

DQU4

A8

DQU5

A3

DQU6

B9

DQU7

A4

DQU0

D8

A13

T4

A14

T8

NC

M8

BA2

M4

VREFDQ

H2

NC

L10

VDD

N2

VDD

N10

VDD

R2

VDD

R10

VSS

J9

VSS

M2

VSS

M10

VSS

P2

VSS

P10

VSS

T2

VSS

T10

VDDQ

D3

R52 48 36_ 04 02 _5%R52 48 36_ 04 02 _5%

1 2

C5259

10U_0603_6.3V6M

C5259

10U_0603_6.3V6M

1

2

R52 42 36_ 04 02 _5%R52 42 36_ 04 02 _5%

1 2

R52 38 36_ 04 02 _5%R52 38 36_ 04 02 _5%

1 2

+

C52 57

220 U_D 2_2VY_ R1 5M

@

+

C52 57

220 U_D 2_2VY_ R1 5M

@

1

2

R52 35 36_ 04 02 _5%R52 35 36_ 04 02 _5%

1 2

C52 46

0.1U_0402_16V4Z

C52 46

0.1U_0402_16V4Z

1

2

C5256

10U_0603_6.3V6M

C5256

10U_0603_6.3V6M

1

2

R52 31 36_ 04 02 _5%R52 31 36_ 04 02 _5%

1 2

R52 19 36_ 04 02 _5%R52 19 36_ 04 02 _5%

1 2

C52 75

0.1U_ 04 02_16 V4 Z

C52 75

0.1U_ 04 02_16 V4 Z

1

2

R52 15 36_ 04 02 _5%R52 15 36_ 04 02 _5%

1 2

R51 97240_ 04 02_1% R5 197240_04 02 _1%

1 2

R51 96

240 _0 40 2_1 %

R51 96

240 _0 40 2_1 %

1 2

C5263

0.1U_0402_16V7K

C5263

0.1U_0402_16V7K

1

2

96-B AL L

SDR AM D DR3L

U500 9

H5TC 4G 63MFR-P BA _FBGA 96

DDR 1@

96-B AL L

SDR AM D DR3L

U500 9

H5TC 4G 63MFR-P BA _FBGA 96

DDR 1@

WE

L4

RAS

J4

CAS

K4

CS

L3

CKE

K10

CK

J8

CK

K8

DQSU

B8

BA0

M3

BA1

N9

A2

P4

A3

N3

A4

P9

A5

P3

A6

R9

A7

R3

A8

T9

A9

R4

A10/AP

L8

A11

R8

DQL0

E4

DQL1

F8

DQL2

F3

DQL3

F9

DQL4

H4

DQL5

H9

DQL6

G3

DQL7

H8

VSSQ

D2

VSS

A10

VSS

E2

VSS

B4

NC

J2

VDD

B3

VDD

D10

VDDQ

A2

VDDQ

A9

VDDQ

C2

VDDQ

C10

NC

L2

NC

J10

VDDQ

E10

ZQ

L9

RESET

T3

DQSL

F4

DMU

D4

DML

E8

VSSQ

B2

VSSQ

B10

VSSQ

D9

VSSQ

E3

DQSU

C8

VSSQ

E9

DQSL

G4

VDDQ

F2

VSSQ

F10

VSSQ

G2

VDDQ

H3

VDDQ

H10

VSSQ

G10

VREFCA

M9

VSS

G9

VDD

G8

ODT

K2

A0

N4

A1

P8

VDD

K3

A12/BC

N8

VSS

J3

VDD

K9

DQU1

C4

DQU2

C9

DQU3

C3

DQU4

A8

DQU5

A3

DQU6

B9

DQU7

A4

DQU0

D8

A13

T4

A14

T8

NC

M8

BA2

M4

VREFDQ

H2

NC

L10

VDD

N2

VDD

N10

VDD

R2

VDD

R10

VSS

J9

VSS

M2

VSS

M10

VSS

P2

VSS

P10

VSS

T2

VSS

T10

VDDQ

D3

R52 08

1K_ 04 02 _1%

R52 08

1K_ 04 02 _1%

12

R52 09

30.1 _0 40 2_1 %

R52 09

30.1 _0 40 2_1 %

12

R52 40 36_ 04 02 _5%R52 40 36_ 04 02 _5%

1 2

C5254

10U_0603_6.3V6M

C5254

10U_0603_6.3V6M

1

2

C5271

0.1U_0402_16V4Z

C5271

0.1U_0402_16V4Z

1

2

C5253

10U_0603_6.3V6M

C5253

10U_0603_6.3V6M

1

2

C5255

10U_0603_6.3V6M

C5255

10U_0603_6.3V6M

1

2

C52 40

0.1U_0402_16V4Z

C52 40

0.1U_0402_16V4Z

1

2

R52 18 36_ 04 02 _5%R52 18 36_ 04 02 _5%

1 2

C52 45

0.1U_0402_16V4Z

C52 45

0.1U_0402_16V4Z

1

2

R52 46 36_ 04 02 _5%R52 46 36_ 04 02 _5%

1 2

R52 43 36_ 04 02 _5%R52 43 36_ 04 02 _5%

1 2

R52 39 36_ 04 02 _5%R52 39 36_ 04 02 _5%

1 2

C52 42

0.1U_0402_16V4Z

C52 42

0.1U_0402_16V4Z

1

2

R52 33 36_ 04 02 _5%R52 33 36_ 04 02 _5%

1 2

C5258

10U_0603_6.3V6M

C5258

10U_0603_6.3V6M

1

2

R52 27 36_ 04 02 _5%R52 27 36_ 04 02 _5%

1 2

R52 20 36_ 04 02 _5%R52 20 36_ 04 02 _5%

1 2

C5251

1U_0402_6.3V6K

C5251

1U_0402_6.3V6K

1

2

R52 16 36_ 04 02 _5%R52 16 36_ 04 02 _5%

1 2

R51 98

240 _0 40 2_1 %

R51 98

240 _0 40 2_1 %

1 2

C52 43

0.1U_0402_16V4Z

C52 43

0.1U_0402_16V4Z

1

2

U501 0

CAT 24 C0 2W I-G T3 A_SO8

@

U501 0

CAT 24 C0 2W I-G T3 A_SO8

@

A0

1

A1

2

A2

3

VSS

4

VCC

8

WP

7

SCL

6

SDA

5

R52 29

30.1 _0 40 2_1 %

R52 29

30.1 _0 40 2_1 %

12

C5260

0.1U_0402_16V7K

C5260

0.1U_0402_16V7K

1

2

R52 45 36_ 04 02 _5%R52 45 36_ 04 02 _5%

1 2

R52 14 36_ 04 02 _5%R52 14 36_ 04 02 _5%

1 2

C52 39

0.1U_0402_16V4Z

C52 39

0.1U_0402_16V4Z

1

2

C5272

2.2U_0603_6.3V6K

C5272

2.2U_0603_6.3V6K

1

2

R52 32 36_ 04 02 _5%R52 32 36_ 04 02 _5%

1 2

C5250

1U_0402_6.3V6K

C5250

1U_0402_6.3V6K

1

2

R52 22 36_ 04 02 _5%R52 22 36_ 04 02 _5%

1 2

C5248

1U_0402_6.3V6K

C5248

1U_0402_6.3V6K

1

2

R52 47 36_ 04 02 _5%R52 47 36_ 04 02 _5%

1 2

C5273

0.1U_0402_16V4Z

C5273

0.1U_0402_16V4Z

1

2

R52 44 36_ 04 02 _5%R52 44 36_ 04 02 _5%

1 2

C52 47

0.1U_ 04 02_16 V4 Z~D

@

C52 47

0.1U_ 04 02_16 V4 Z~D

@

1 2

R52 37 36_ 04 02 _5%R52 37 36_ 04 02 _5%

1 2

R52 34 36_ 04 02 _5%R52 34 36_ 04 02 _5%

1 2

C52 52

2P_ 04 02 _50 V8 C

C52 52

2P_ 04 02 _50 V8 C

1

2

R52 28 36_ 04 02 _5%R52 28 36_ 04 02 _5%

1 2

C5262

0.1U_0402_16V7K

C5262

0.1U_0402_16V7K

1

2

R52 21 36_ 04 02 _5%R52 21 36_ 04 02 _5%

1 2

R51 99

240 _0 40 2_1 %

R51 99

240 _0 40 2_1 %

1 2

C52 44

0.1U_0402_16V4Z

C52 44

0.1U_0402_16V4Z

1

2

R5200

1K_0402_5%~D

@

R5200

1K_0402_5%~D

@

12

C53 11

0.1U_ 04 02_16 V4 Z

C53 11

0.1U_ 04 02_16 V4 Z

1

2

R52 17 36_ 04 02 _5%R52 17 36_ 04 02 _5%

1 2

R52 07

1K_ 04 02 _1%

R52 07

1K_ 04 02 _1%

12

C5249

1U_0402_6.3V6K

C5249

1U_0402_6.3V6K

1

2

C5274

2.2U_0603_6.3V6K

C5274

2.2U_0603_6.3V6K

1

2

R52 10

30.1 _0 40 2_1 %

R52 10

30.1 _0 40 2_1 %

12

C5261

0.1U_0402_16V7K

C5261

0.1U_0402_16V7K

1

2

R52 30

30.1 _0 40 2_1 %

R52 30

30.1 _0 40 2_1 %

12

R5201

1K_0402_5%~D

@

R5201

1K_0402_5%~D

@

12

R52 13

1K_ 04 02 _1%

R52 13

1K_ 04 02 _1%

12

R52 12

1K_ 04 02 _1%

R52 12

1K_ 04 02 _1%

12

R52 36 36_ 04 02 _5%R52 36 36_ 04 02 _5%

1 2

96-B AL L

SDR AM D DR3L

U500 8

H5TC 4G 63MFR-P BA _FBGA 96

DDR 1@

96-B AL L

SDR AM D DR3L

U500 8

H5TC 4G 63MFR-P BA _FBGA 96

DDR 1@

WE

L4

RAS

J4

CAS

K4

CS

L3

CKE

K10

CK

J8

CK

K8

DQSU

B8

BA0

M3

BA1

N9

A2

P4

A3

N3

A4

P9

A5

P3

A6

R9

A7

R3

A8

T9

A9

R4

A10/AP

L8

A11

R8

DQL0

E4

DQL1

F8

DQL2

F3

DQL3

F9

DQL4

H4

DQL5

H9

DQL6

G3

DQL7

H8

VSSQ

D2

VSS

A10

VSS

E2

VSS

B4

NC

J2

VDD

B3

VDD

D10

VDDQ

A2

VDDQ

A9

VDDQ

C2

VDDQ

C10

NC

L2

NC

J10

VDDQ

E10

ZQ

L9

RESET

T3

DQSL

F4

DMU

D4

DML

E8

VSSQ

B2

VSSQ

B10

VSSQ

D9

VSSQ

E3

DQSU

C8

VSSQ

E9

DQSL

G4

VDDQ

F2

VSSQ

F10

VSSQ

G2

VDDQ

H3

VDDQ

H10

VSSQ

G10

VREFCA

M9

VSS

G9

VDD

G8

ODT

K2

A0

N4

A1

P8

VDD

K3

A12/BC

N8

VSS

J3

VDD

K9

DQU1

C4

DQU2

C9

DQU3

C3

DQU4

A8

DQU5

A3

DQU6

B9

DQU7

A4

DQU0

D8

A13

T4

A14

T8

NC

M8

BA2

M4

VREFDQ

H2

NC

L10

VDD

N2

VDD

N10

VDD

R2

VDD

R10

VSS

J9

VSS

M2

VSS

M10

VSS

P2

VSS

P10

VSS

T2

VSS

T10

VDDQ

D3

C52 41

0.1U_0402_16V4Z

C52 41

0.1U_0402_16V4Z

1

2

96-B AL L

SDR AM D DR3L

U500 6

H5TC 4G 63MFR-P BA _FBGA 96

DDR 1@

96-B AL L

SDR AM D DR3L

U500 6

H5TC 4G 63MFR-P BA _FBGA 96

DDR 1@

WE

L4

RAS

J4

CAS

K4

CS

L3

CKE

K10

CK

J8

CK

K8

DQSU

B8

BA0

M3

BA1

N9

A2

P4

A3

N3

A4

P9

A5

P3

A6

R9

A7

R3

A8

T9

A9

R4

A10/AP

L8

A11

R8

DQL0

E4

DQL1

F8

DQL2

F3

DQL3

F9

DQL4

H4

DQL5

H9

DQL6

G3

DQL7

H8

VSSQ

D2

VSS

A10

VSS

E2

VSS

B4

NC

J2

VDD

B3

VDD

D10

VDDQ

A2

VDDQ

A9

VDDQ

C2

VDDQ

C10

NC

L2

NC

J10

VDDQ

E10

ZQ

L9

RESET

T3

DQSL

F4

DMU

D4

DML

E8

VSSQ

B2

VSSQ

B10

VSSQ

D9

VSSQ

E3

DQSU

C8

VSSQ

E9

DQSL

G4

VDDQ

F2

VSSQ

F10

VSSQ

G2

VDDQ

H3

VDDQ

H10

VSSQ

G10

VREFCA

M9

VSS

G9

VDD

G8

ODT

K2

A0

N4

A1

P8

VDD

K3

A12/BC

N8

VSS

J3

VDD

K9

DQU1

C4

DQU2

C9

DQU3

C3

DQU4

A8

DQU5

A3

DQU6

B9

DQU7

A4

DQU0

D8

A13

T4

A14

T8

NC

M8

BA2

M4

VREFDQ

H2

NC

L10

VDD

N2

VDD

N10

VDD

R2

VDD

R10

VSS

J9

VSS

M2

VSS

M10

VSS

P2

VSS

P10

VSS

T2

VSS

T10

VDDQ

D3

AMY WEN