内存屏障:硬件视角下的软件优化解析

"内存屏障是计算机硬件和软件交互的关键机制,用于确保在多处理器系统(SMP)中的同步原语正确执行。它们的存在是由于CPU为了优化性能而进行的内存引用重排序,但这种重排序可能导致内存访问顺序的不确定性,从而影响同步操作的正确性。本文将深入探讨内存屏障的原理,以及它们与CPU缓存、一致性协议的关系。

1. CPU缓存结构:

CPU缓存是位于CPU与主内存之间的小型高速存储器,旨在减少CPU访问主内存的延迟。缓存通常分为多个层次(如L1、L2、L3),每个层次具有不同的大小和速度。缓存的工作基于局部性原理,即程序倾向于在短时间内访问同一块内存区域。缓存通过缓存行(Cache Line)来存储和管理数据,当CPU需要读取或写入数据时,会首先查找缓存,如果数据在缓存中,称为缓存命中;否则,称为缓存未命中,需要从主内存中加载。

2. 缓存一致性协议:

在多处理器系统中,每个CPU都有自己的缓存,当多个CPU同时修改共享内存时,必须保证所有CPU对内存状态有一致的视图。为此,引入了缓存一致性协议,如MESI(Modified, Exclusive, Shared, Invalidated)或MOESI(Modified, Owned, Exclusive, Shared, Invalidated)。这些协议规定了如何处理缓存行的状态变化和在CPU间传播这些变化,以保持数据的一致性。

3. 存储缓冲区与无效队列:

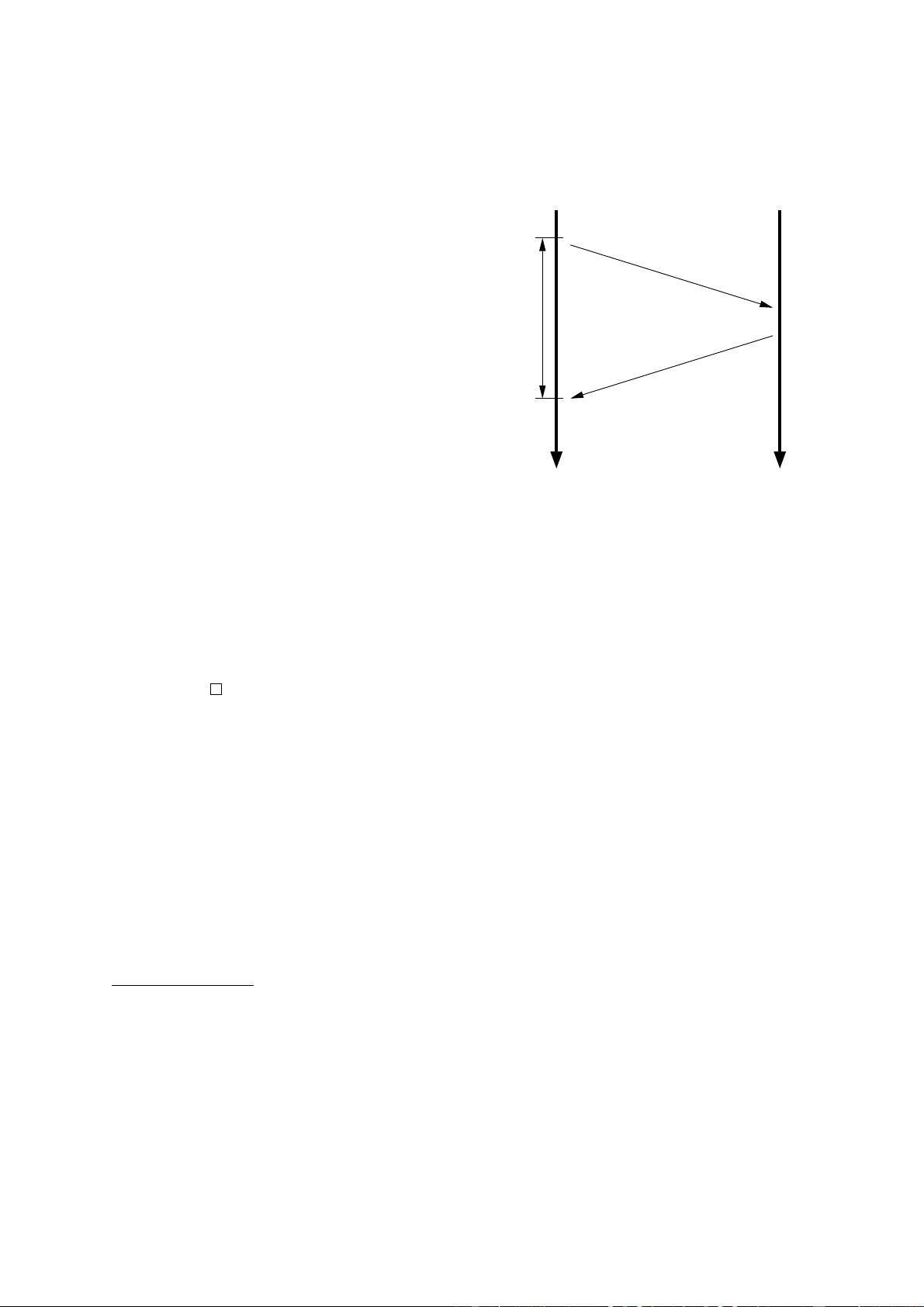

现代CPU在写操作时可能不会立即更新主内存,而是将数据暂存到存储缓冲区中,等到合适时机再批量写入。同时,当一个CPU修改了缓存中的数据,需要通知其他CPU其缓存中对应数据已失效,这涉及到无效队列的管理。这些机制虽然提高了性能,但也可能导致数据的可见性问题。

4. 内存屏障的作用:

内存屏障是一种指令,用于阻止特定内存操作的重排序。它确保在屏障前的操作完成并使其他处理器看到这些操作后,才执行屏障后的操作。对于Java程序员来说,内存屏障体现在 volatile 关键字的使用上,它可以强制内存操作的顺序,保证多线程环境中的可见性和有序性。

总结来说,内存屏障是应对CPU缓存优化和数据一致性挑战的必要工具。它们虽然带来了复杂性,但确保了在高性能和可扩展性的系统中,软件能够正确地执行同步操作,维持数据的一致性和正确性。"

点击了解资源详情

118 浏览量

158 浏览量

1683 浏览量

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

Jake27U1

- 粉丝: 1

- 资源: 11

最新资源

- 顶部导航菜单下拉,左侧分类切换

- XX公司企业文化职能战略规划PPT

- torch_cluster-1.5.6-cp37-cp37m-win_amd64whl.zip

- 使用WPF表单的AC#系统托盘应用程序

- Color-Transfer-between-Images:这是开源工具Erik Reinhard,Michael Ashikhmin,Bruce Gooch和Peter Shirley撰写的论文“图像之间的颜色转移”

- log4net工具包与配置文件.rar

- 企业文化案例(8个文件)

- PokemonGo-CalcyIV-Renamer:使用adb将假冒的点击事件发送到您的手机,以及Calcy IV一起自动重命名所有宠物小精灵

- torch_sparse-0.6.5-cp36-cp36m-win_amd64whl.zip

- cd2021

- Angel网络工作室报名网站管理系统v1.0

- CssWebResposive:罪过的评论

- 导航条宽度随二级菜单宽度变化的

- 系统温湿度检测与控制 1-源程序注释.rar

- iicTets.zip

- QAServer:基于质量检查服务器的中文CQA网站