12

AWR2243

ZHCSKT7 –FEBRUARY 2020

www.ti.com.cn

Submit Documentation Feedback

Product Folder Links: AWR2243

Terminal Configuration and Functions Copyright © 2020, Texas Instruments Incorporated

(1) Status of PULL structures associated with the IO after device POWER UP.

(2) Cascading feature is available only in the AWR2243 device.

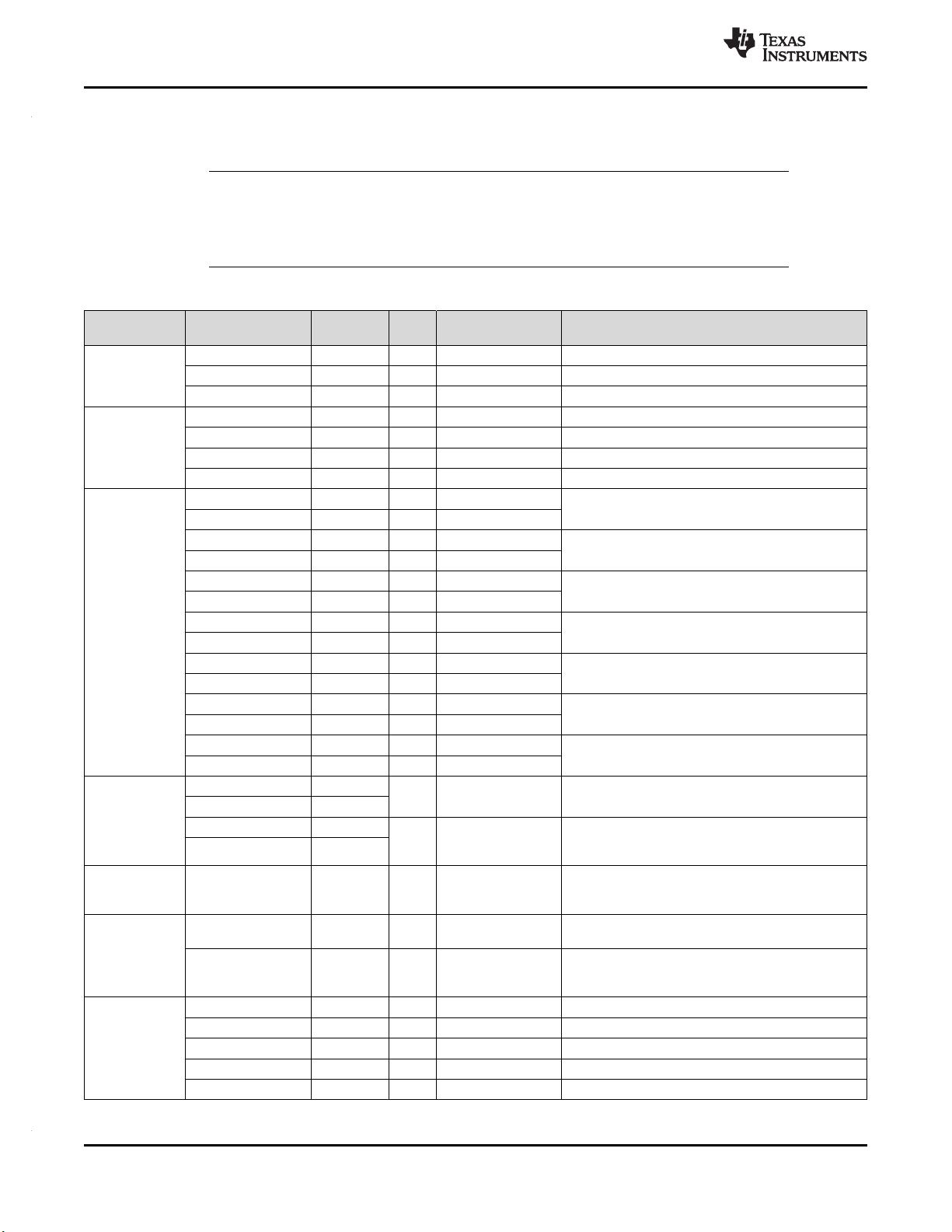

4.2 Signal Descriptions

Table 4-1 lists the pins by function and describes that function.

NOTE

All IO pins of the device (except NERROR IN, NERROR_OUT, and WARM_RESET) are

non-failsafe; hence, care needs to be taken that they are not driven externally without the

VIO supply being present to the device.

Table 4-1. Signal Descriptions

FUNCTION SIGNAL NAME

PIN

NUMBER

PIN

TYPE

DEFAULT PULL

STATUS

(1)

DESCRIPTION

Transmitters

TX1 B4 O — Single-ended transmitter1 o/p

TX2 B6 O — Single-ended transmitter2 o/p

TX3 B8 O — Single-ended transmitter3 o/p

Receivers

RX1 M2 I — Single-ended receiver1 i/p

RX2 K2 I — Single-ended receiver2 i/p

RX3 H2 I — Single-ended receiver3 i/p

RX4 F2 I — Single-ended receiver4 i/p

CSI2 TX

CSI2_TXP[0] G15 O —

Differential data Out – Lane 0 (for CSI and LVDS

debug interface)

CSI2_TXM[0] G14 O —

CSI2_CLKP J15 O —

Differential clock Out (for CSI and LVDS debug

interface)

CSI2_CLKM J14 O —

CSI2_TXP[1] H15 O —

Differential data Out – Lane 1 (for CSI and LVDS

debug interface)

CSI2_TXM[1] H14 O —

CSI2_TXP[2] K15 O —

Differential data Out – Lane 2 (for CSI and LVDS

debug interface)

CSI2_TXM[2] K14 O —

CSI2_TXP[3] L15 O —

Differential data Out – Lane 3 (for CSI and LVDS

debug interface)

CSI2_TXM[3] L14 O —

HS_DEBUG1_P M15 O —

Differential debug port 1 (for LVDS debug interface)

HS_DEBUG1_M M14 O —

HS_DEBUG2_P N15 O —

Differential debug port 2 (for LVDS debug interface)

HS_DEBUG2_M N14 O —

Chip-to-chip

cascading

synchronization

signals

(2)

FM_CW_CLKOUT B15

O — 20-GHz single-ended output. Modulated waveform

FM_CW_SYNCOUT D1

FM_CW_SYNCIN1 B1

I —

20-GHz single-ended input. Only one of these pins

should be used. Multiple instances for layout

flexibility.

FM_CW_SYNCIN2 D15

Reference clock OSC_CLKOUT A14 O —

Reference clock output from clocking subsystem

after cleanup PLL. Can be used by slave chip in

multichip cascading

System

synchronization

SYNC_OUT P11 O Pull Down

Low-frequency frame synchronization signal output.

Can be used by slave chip in multichip cascading

SYNC_IN N10 I Pull Down

Low-frequency frame synchronization signal input.

This signal could also be used as a hardware trigger

for frame start

SPI control

interface from

external MCU

(default slave

mode)

SPI_CS_1 R7 I Pull Up SPI chip select

SPI_CLK_1 R9 I Pull Down SPI clock

MOSI_1 R8 I Pull Up SPI data input

MISO_1 P5 O Pull Up SPI data output

SPI_HOST_INTR_1 P6 O Pull Down SPI interrupt to host