数字PID控制器设计与调速实验分析 - MATLAB仿真分析及性能影响评估

版权申诉

198 浏览量

更新于2024-02-28

1

收藏 281KB DOC 举报

一、实验目的与内容

本实验旨在分析晶闸管直流单闭环调速系统中PID控制器的设计及参数对系统性能的影响。具体实验目的包括:理解直流单闭环调速系统的数学模型和工作原理、掌握PID控制器参数对系统性能的影响、熟练运用MATLAB/Simulink软件对系统建模及参数设置、掌握计算机控制仿真结果的分析方法。实验工具为MATLAB软件。

二、实验步骤

1. 模拟PID控制作用分析

- 比例控制作用分析:

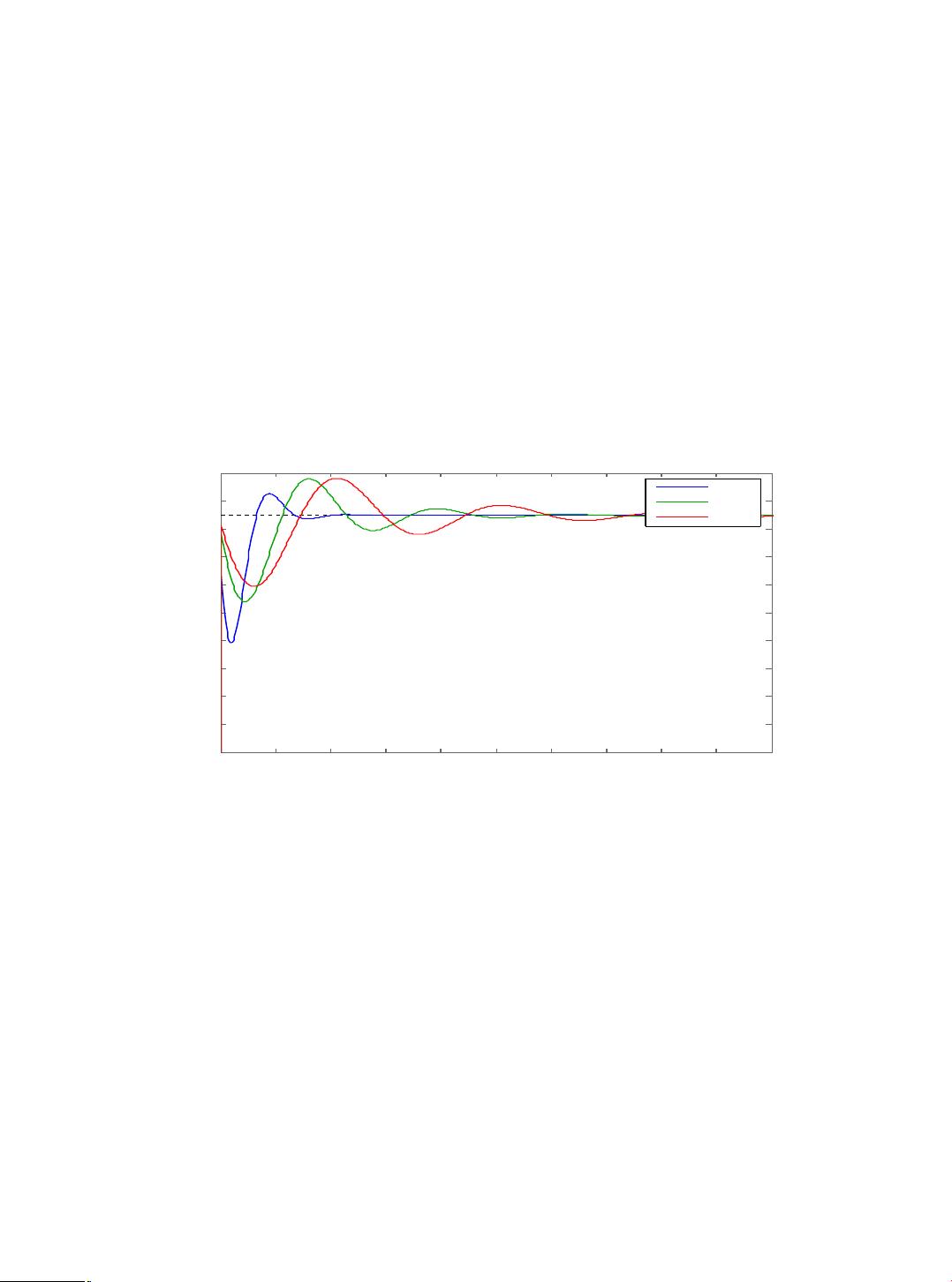

采用MATLAB软件对系统的比例控制作用进行分析,通过设置参数Td = 0, Ti = 0,以及不同的Kp值(1~5),观察系统的阶跃响应曲线。根据实验结果显示,比例系数越大,系统的响应速度越快,稳态误差越小,但会增加超调量。

- 积分控制作用分析:

保持Kp = 1不变,通过调整Ti的数值(0.03~0.07),观察系统的阶跃响应。实验结果显示,积分系数对系统的响应速度和稳定性有显著影响,适当调整积分时间常数可减小系统超调量和稳态误差。

- 微分控制作用分析:

保持Kp = 1和Ti = 0不变,通过设置不同的Td值观察系统的阶跃响应曲线。微分控制作用对系统的稳定性和抑制振荡有一定作用,适当的微分时间常数能够减小系统的超调量和振荡现象。

3. 最佳PID参数设计

根据比例、积分和微分控制作用的分析结果,可以通过试验和调整得到最佳的PID控制器参数组合,以提高系统的响应速度、稳定性和准确性。

4. 性能评价与分析

通过对最佳PID参数组合下系统的阶跃响应曲线进行分析,评价系统的性能表现,如超调量、稳态误差、响应速度等。根据分析结果,结合实际应用需求,进一步优化PID控制器参数,以达到最佳的控制效果和性能表现。

总体而言,本实验通过对晶闸管直流单闭环调速系统的PID控制器设计与分析,深入探讨了参数调整对系统性能的影响,为掌握控制系统的调节与优化提供了实践基础和指导原则。

184 浏览量

201 浏览量

2009-06-24 上传

2021-12-24 上传

133 浏览量

2022-10-19 上传

是空空呀

- 粉丝: 199

- 资源: 3万+

最新资源

- skinrestorerfilegen

- katacoda方案:Katacoda方案

- 多功能便签效果

- JSPGenCMS 4.0 20160520

- SZFMBeadando

- XX种畜牧草良种繁殖场反季节蔬菜(萝卜)加工项目商业计划书.zip

- 开店损益评估表excel模板下载

- 电子邮件地址:Spring Cloud的餐厅服务,餐厅和餐厅

- capecodseedcoop

- html5lib-0.999999999.tar.gz

- Cloth-simulation:使用质量弹簧模型模拟布料

- vicky:Vicky 是使用 ffmpeg 将视频文件转换为声音文件的 GUI 程序

- perl-orm-easy:PostgreSQL数据库内ORM

- onlineSystem:基于SSH + BootStrap的在线考试系统

- 商场设计CAD图纸

- Dizi Haberleri-crx插件