基于FPGA的高速HDLC通信控制器设计与实现

156 浏览量

更新于2024-08-29

收藏 1.23MB PDF 举报

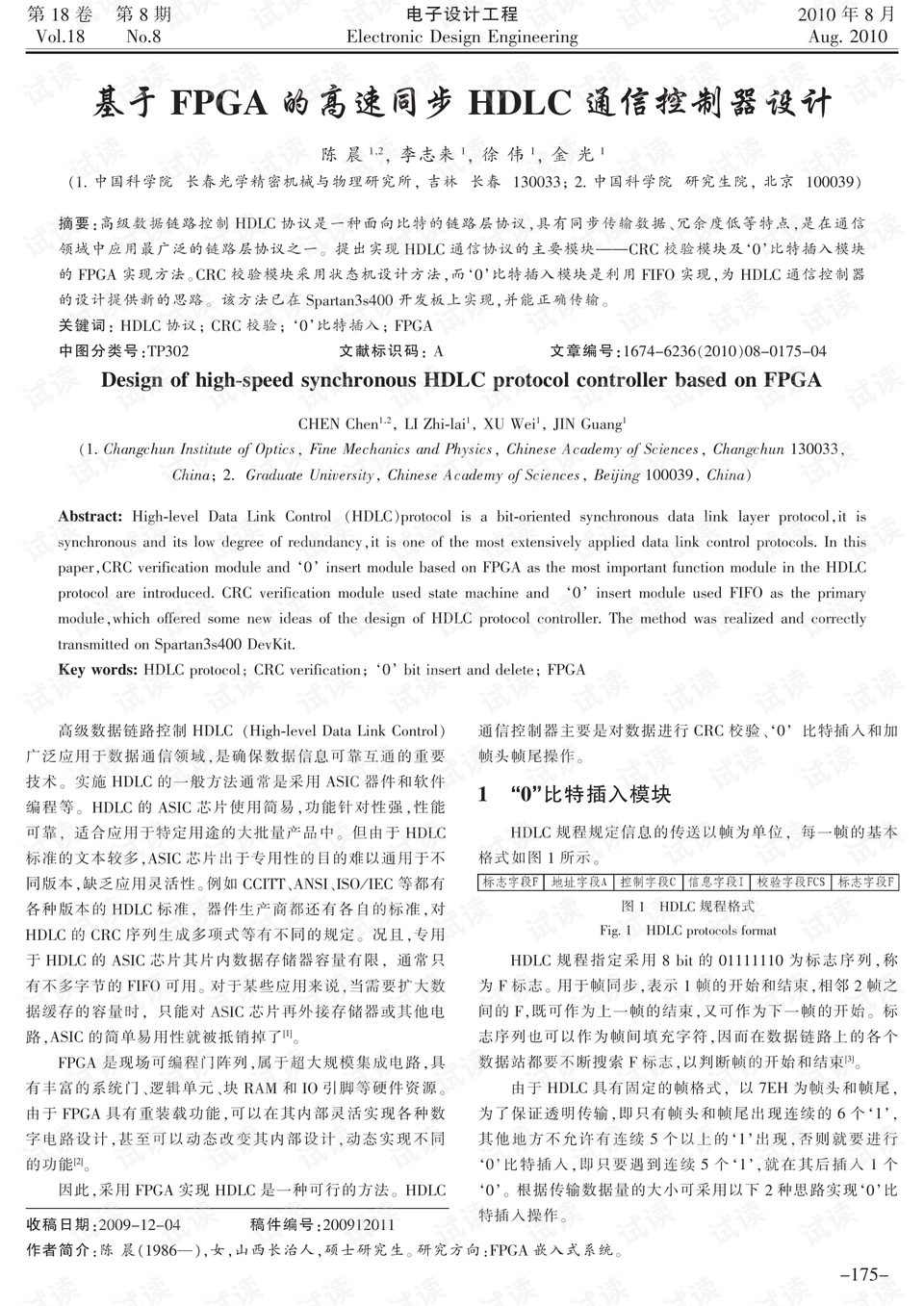

本文主要探讨了基于FPGA的高速同步高级数据链路控制(HDLC)通信控制器的设计。HDLC是一种经典的面向比特的链路层协议,它支持同步数据传输,具有较高的传输效率和较低的冗余度,被广泛应用于通信系统中。文章的重点在于实现两个关键模块:CRC校验模块和‘0’比特插入模块。

CRC校验模块是通信控制器中的一个重要组成部分,它用于检测数据传输过程中的错误。设计者采用了状态机的方法来实现这个模块,确保数据的准确性和完整性。状态机通过一系列的状态转移规则,根据接收到的比特流计算循环冗余校验码(CRC),如果接收的数据与预期的CRC码不符,就可能发生错误,从而触发相应的错误处理机制。

‘0’比特插入模块的作用是在数据包中插入特定的‘0’比特,以保持数据帧的同步。设计者通过使用FIFO(First-In-First-Out)数据结构来实现这个功能,FIFO能够按照数据到达的顺序存储并取出,确保在发送时始终按照规定的帧格式进行操作,防止数据失序或丢失。

作者在Spartan3s400开发板上成功实现了这一设计,验证了这种方法的有效性和可靠性。整个通信控制器设计充分考虑了性能和效率,使得HDLC协议能够在FPGA平台上高效运行,适用于各种实时通信应用场景,如工业控制、网络设备等。

总结来说,这篇论文提供了将HDLC协议的核心功能,如CRC校验和‘0’比特插入,集成到FPGA中的具体实现策略,对于理解FPGA在通信系统中的应用以及设计高速、可靠的数据链路控制具有重要的参考价值。同时,通过实验验证,证明了这种设计方法在实际硬件平台上的可行性,为工程师们在类似项目中提供了实践经验和技术指导。

2021-07-13 上传

287 浏览量

135 浏览量

222 浏览量

204 浏览量

114 浏览量

2021-09-21 上传

2021-05-20 上传

130 浏览量

weixin_38748580

- 粉丝: 6

最新资源

- C#高效多线程下载器组件源码V1.12发布

- 32位Windows汇编语言程序设计大全

- Sketch插件库替换器:简化库更换流程

- 首版投资组合网站的开发与部署指南

- C语言实现农历与阳历转换的新库发布

- 探索Linux下的Vim优雅配色方案:Colibri.vim

- STM32 TFT显示技术与刷屏方法解析

- STM32单片机控制交通灯毕设资料整合

- Vitamio实现后台Service播放m3u8音频流

- 使用Docker封装的Alpine版Vim体验

- 步步高高级版WarNards开源项目发布

- 使用JNI实现Java调用VC6 DLL与Linux SO的DEMO教程

- STM32与OLED显示技术的实践应用

- 全面技术覆盖的小区物业管理系统设计与源码

- 清华版编译原理专业课答案解析

- Linux系统下nginx添加SSL配置的详细步骤