ZYNQ-7000 FPGA开发深度解析:ARM与FPGA协同工作与AXI总线详解

需积分: 9 85 浏览量

更新于2024-09-08

1

收藏 402KB DOCX 举报

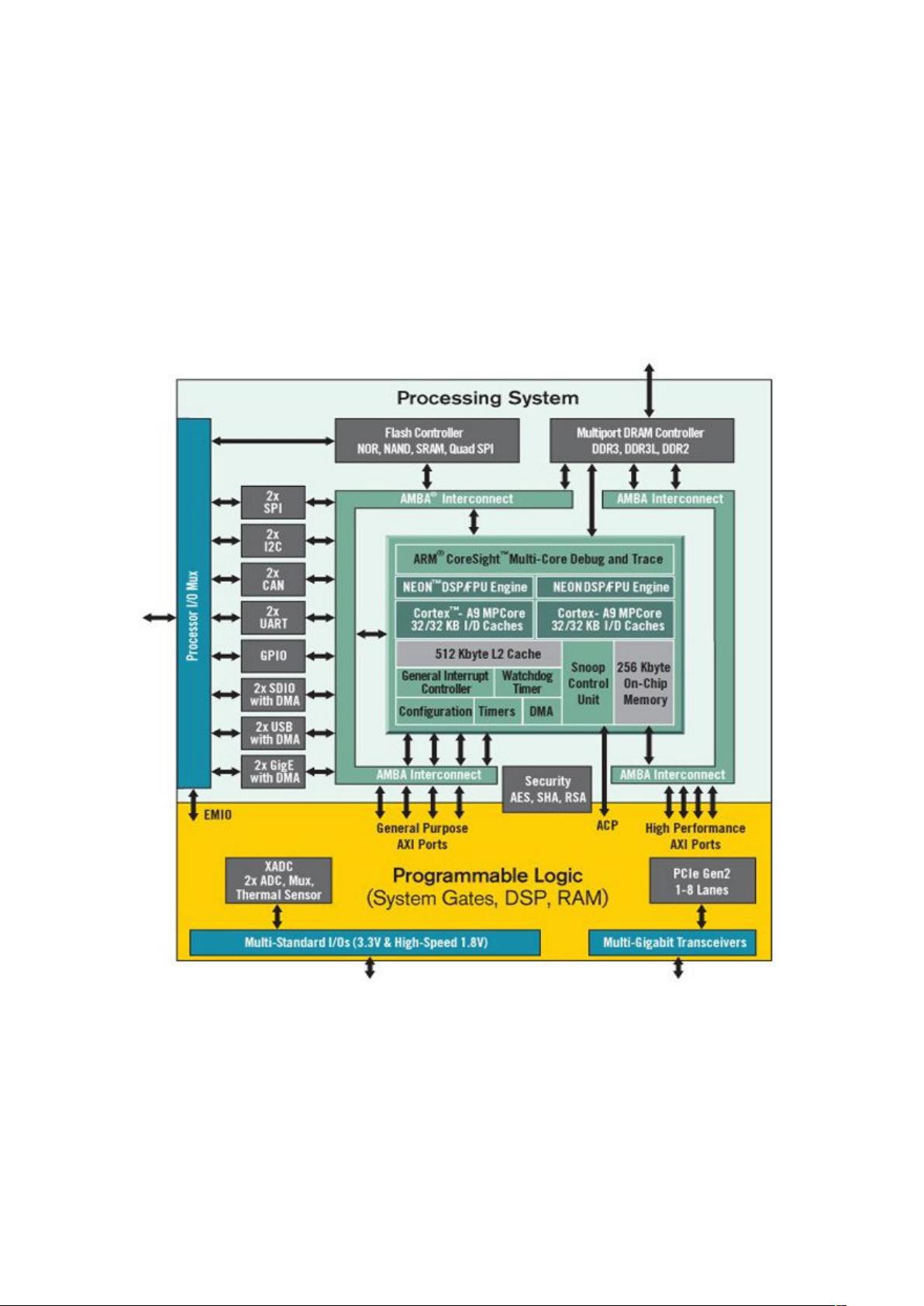

FPGA开发指南深入探讨了Xilinx ZYNQ-7000系列全可编程片上系统(All-Programmable System on Chip, SoC)的特点和工作原理。ZYNQ-7000集成了ARMCortex-A9双核处理器(PS部分)和FPGA逻辑单元(PL部分),形成一个高度灵活的平台。PS部分提供了丰富的外围设备接口,如USB、以太网、SD/SDIO等,支持独立运行,同时也与PL部分通过AXI(Advanced eXtensible Interface)总线进行高效通信。

AXI总线是关键的技术组件,它在ZYNQ-7000中的应用包括AXI_HP(High Performance)、AXI_GP(General Purpose)和AXI_ACP(Advanced Control Plane)接口。AXI_HP用于高性能通信,带宽高达千兆比特,确保了PS和PL之间几乎无限的数据交换能力。AXI_GP则适用于一般目的通信,而AXI_ACP则针对ARM多核架构中的无缓存外设管理,其64位的高性能接口带宽达到1200MB/s,主要用于DMA等操作。

PL部分作为FPGA核心,既可以在ARM的控制下作为从设备,也可以独立工作,甚至控制ARM处理单元。它提供了丰富的功能,如数据交互、存储管理和控制,但配置通常需要JTAG接口。ZYNQ-7000的设计使得PL与PS之间的协同工作非常高效,能够支持高性能且复杂的嵌入式系统设计。

在进行FPGA开发时,开发者需掌握如何利用这些特性,包括配置PS和PL之间的连接,编写ARM和FPGA之间的交互代码,以及优化使用AXI总线以实现高效的系统性能。此外,理解和熟练运用Vivado工具(如FPGA开发环境中的Vivado IDE),对于设计和实现ZYNQ-7000项目至关重要。Vivado提供了图形化界面和脚本编辑器,用于创建硬件描述语言(HDL)模型,进行逻辑综合、布线、仿真和下载到目标硬件。开发者应熟悉FPGA开发流程,包括逻辑设计、验证、编程和调试,确保最终产品的质量和效率。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2023-06-26 上传

2019-01-03 上传

2021-09-29 上传

zbb595291850

- 粉丝: 2

- 资源: 5