Spartan-6 FPGA PCIe Endpoint Block 用户指南

198 浏览量

更新于2024-06-19

收藏 7.67MB PDF 举报

"Spartan-6 FPGA Integrated Endpoint Block是Xilinx公司为PCI Express设计的一款集成终端块,适用于Spartan-6系列FPGA。该用户指南(UG654 v3.0)发布于2010年4月19日,提供了关于如何在Spartan-6 FPGA中实现PCI Express端点功能的详细指导。文档旨在帮助开发者理解和应用Xilinx提供的这一技术,但不包含任何明示或暗示的保修,同时强调了用户需对基于该信息的任何实现可能引发的侵权责任自负。所有规格都可能在没有预先通知的情况下进行更改。"

正文:

Spartan-6 FPGA Integrated Endpoint Block for PCI Express是Xilinx公司为满足高性能嵌入式系统需求而设计的一种核心模块,它允许Spartan-6 FPGA器件作为PCI Express (PCIe)总线架构中的设备端点。PCIe是一种高速接口标准,广泛应用于计算机系统、服务器和嵌入式系统中,提供比传统PCI更高的数据传输速率和更低的延迟。

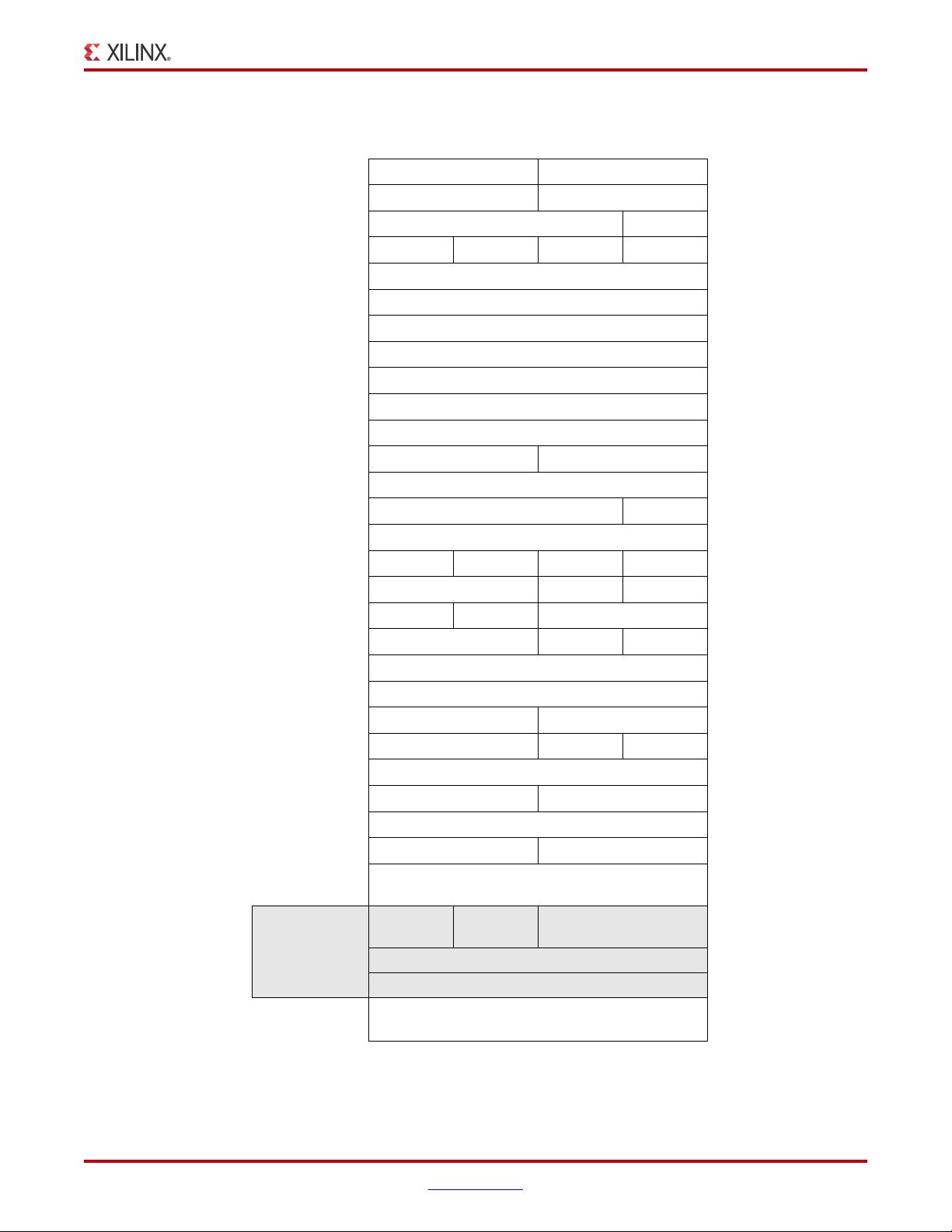

该集成终端块实现了PCI Express协议的物理层(PHY)、数据链路层(DLL)和部分网络层(NL),使得Spartan-6 FPGA能够无缝地与支持PCI Express的主板或其他设备通信。用户指南详细介绍了如何配置和使用这些功能,包括初始化、配置、错误处理和中断管理等方面。

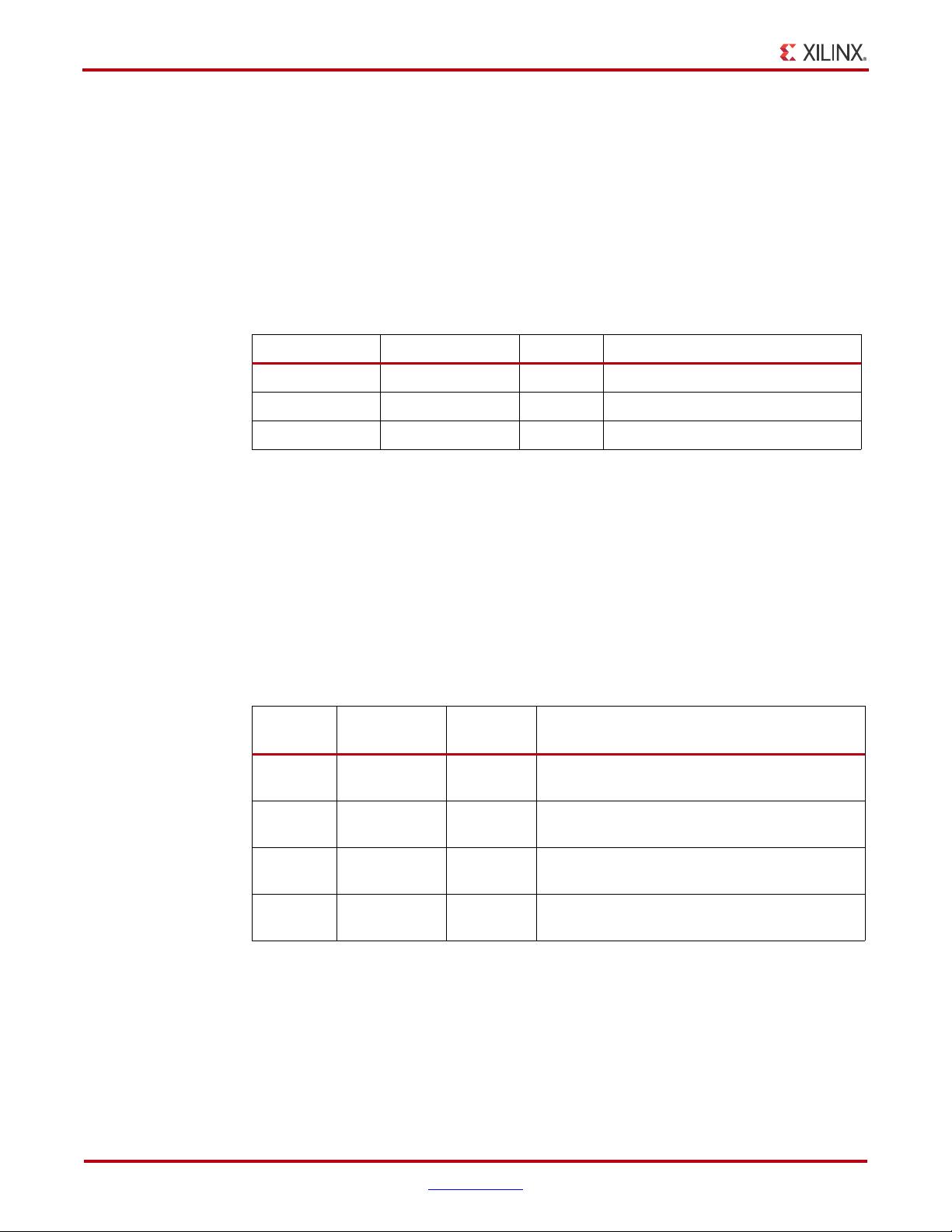

1. 物理层(PHY): PHY层负责管理串行化和去串行化的数据传输,以及信号完整性。Spartan-6 FPGA的PCIe集成终端块支持Gen1速度(2.5 Gbps),提供与PCIe连接所需的物理接口。

2. 数据链路层(DLL): DLL层处理数据包的编码、解码和错误检测,确保数据在传输过程中的正确性。它还管理链接状态,包括连接、训练和维护。

3. 网络层(NL): NL层处理PCI Express的事务层协议,包括请求、响应和流控制。这部分允许端点与上游设备(如根复杂体)交互,处理事务级的数据交换。

在使用Spartan-6 FPGA的PCIe集成终端块时,开发者需要关注以下关键概念:

- 配置空间: 这是每个PCI设备的一部分,用于存储设备的配置信息,如设备ID、厂商ID、中断设置等。

- 帧结构: PCIe协议定义了多种帧类型,包括事务层包(TLPs)、数据包(DPs)和填充包(FLITS),它们共同构成了PCIe总线上的数据传输单元。

- 流ID(Flow ID, FLIT): 用于区分不同的数据流,支持服务质量(QoS)和多队列管理。

- 错误处理: 包括接收错误、CRC错误、解码错误等,需要在设计中进行适当的错误处理机制。

用户指南UG654(v3.0)提供了详细的硬件描述语言(HDL)示例、约束文件模板和设计流程,帮助开发者快速上手并优化他们的PCIe设计。然而,值得注意的是,由于Xilinx不提供任何侵权相关的保证,开发者在使用这些信息进行产品开发时,必须自行评估可能的知识产权风险。

Spartan-6 FPGA Integrated Endpoint Block是实现高效、可靠的PCI Express端点解决方案的关键组件,它简化了PCIe接口的设计,同时也要求开发者具备深厚的PCIe协议理解和技术实施能力。通过遵循Xilinx提供的用户指南,开发者可以有效地利用Spartan-6 FPGA的潜力,构建高性能的PCI Express系统。

195 浏览量

171 浏览量

点击了解资源详情

2023-11-24 上传

237 浏览量

2024-10-28 上传

332 浏览量

2021-07-13 上传

2021-07-13 上传

探索者我有我路向

- 粉丝: 336

最新资源

- C语言文件读取:高效统计字符数方法

- ReactJS和React Native库复制Airbnb应用的研究项目分析

- Ruby应用Bookers3部署与运行自述指南

- YAVI:利用Lambda表达式的Java类型安全验证工具

- 市场专员工作日报表Excel模板免费下载

- 开发图书搜索推荐系统的实践项目

- 利用Spark高效实现Apriori算法

- 欧美风FLASH网页模板设计展示

- PHPmagicSQL:简化MySQL操作的PHP开源抽象层

- Dockerfile实践:构建并运行MYSQL容器映像

- 深入探究Spring Boot 2核心要点

- 新春祝福短信范例集锦

- XSpotLight源码实现iOS新手引导效果

- ngCordova结合离子运动检测技术演示

- Python代码测试实战指南与实践案例

- 商务风格电脑主机HTML模板下载