没有合适的资源?快使用搜索试试~ 我知道了~

首页苹果2017款A1708无Touch Bar MacBook Pro电路原理图解析

苹果2017款A1708无Touch Bar MacBook Pro电路原理图解析

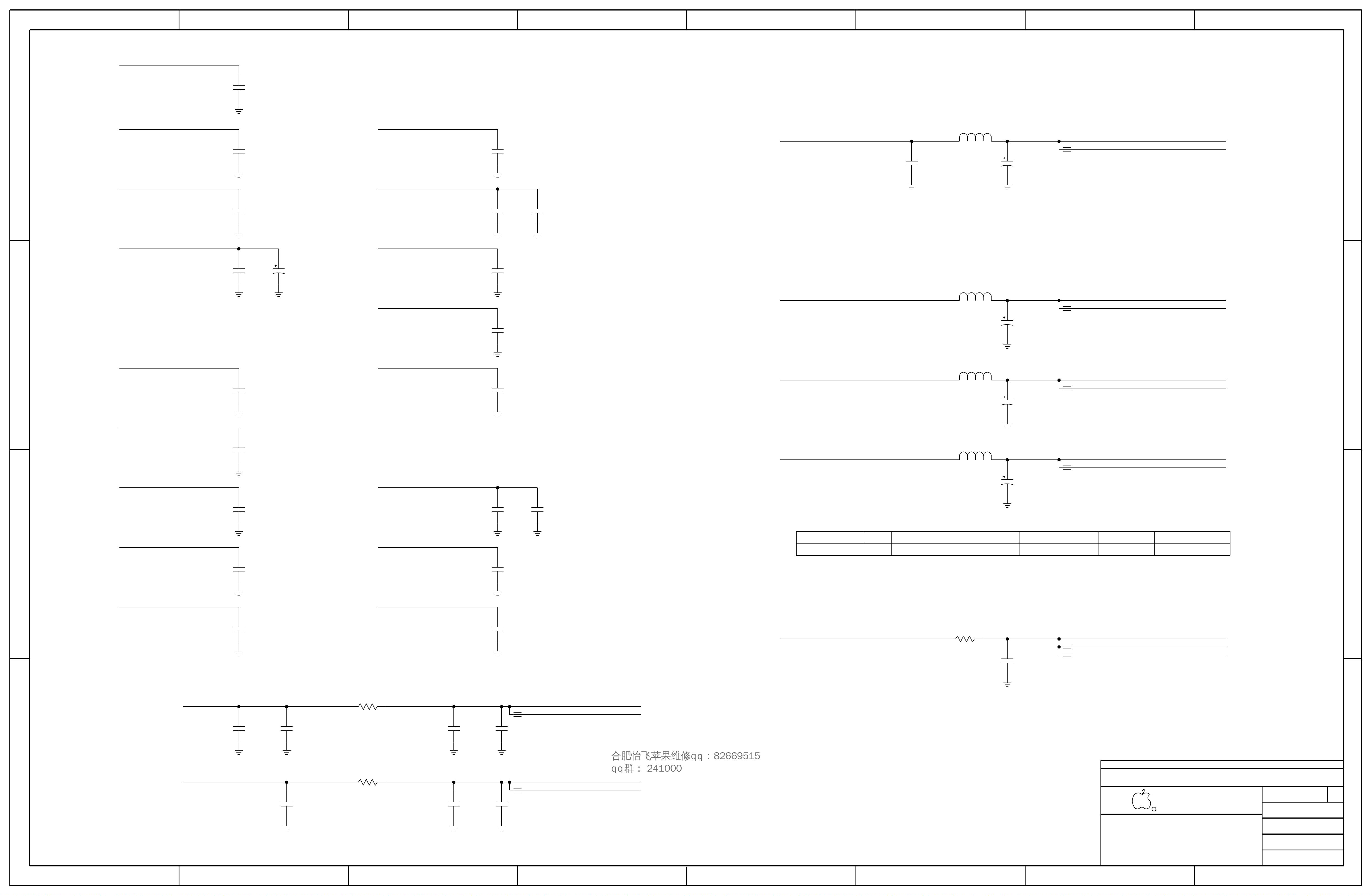

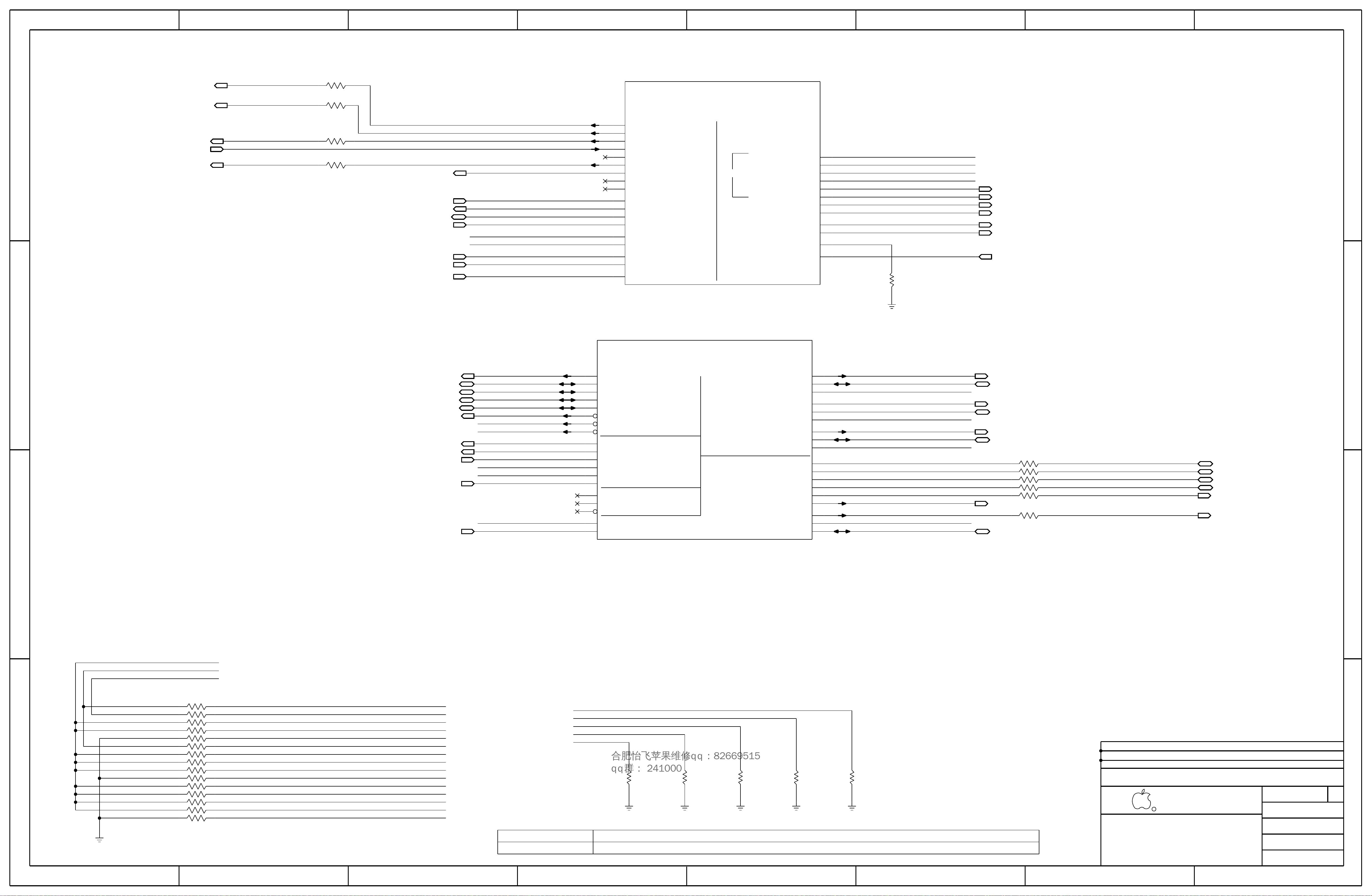

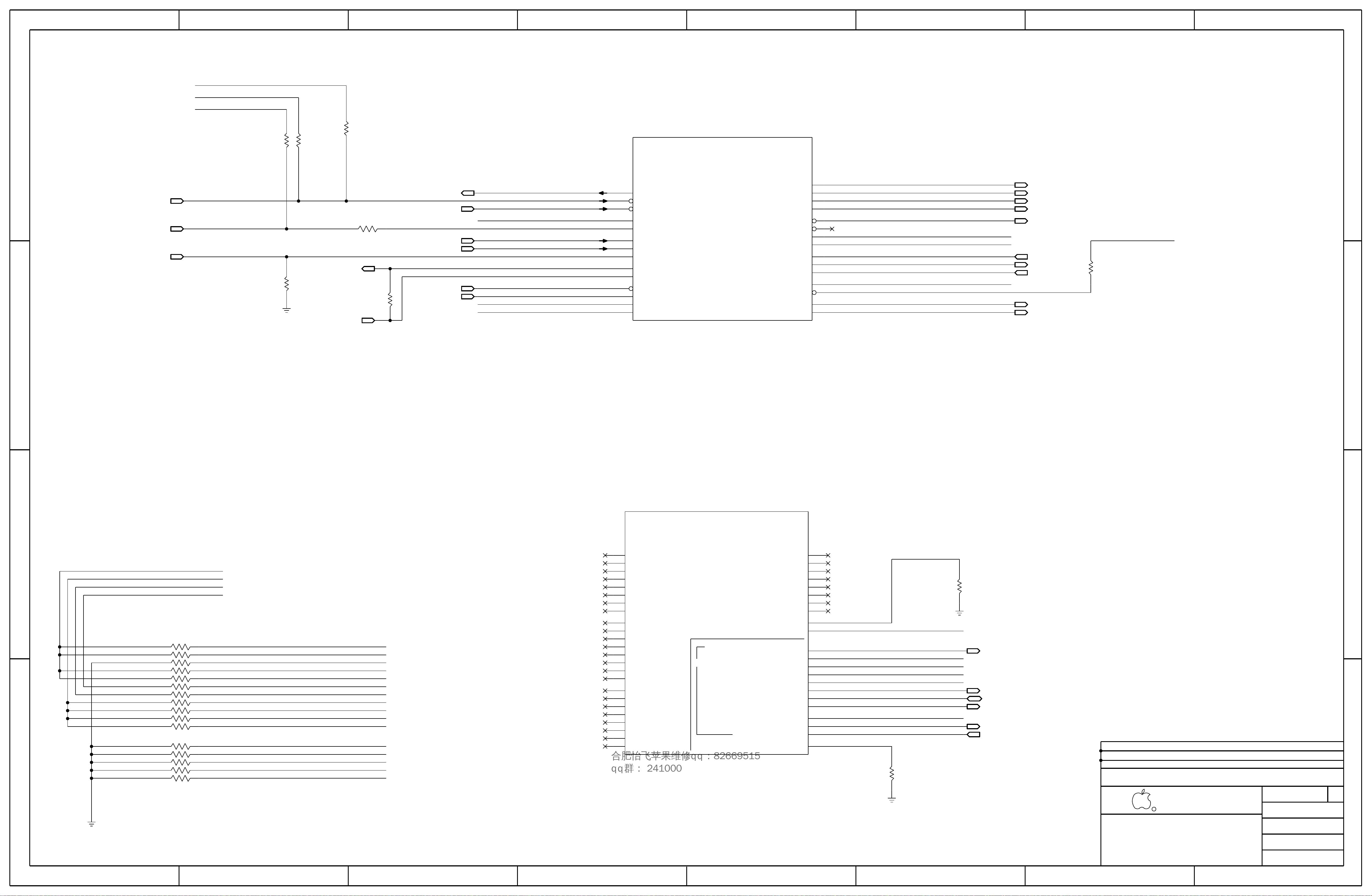

该资源是一份苹果2017款A1708型号无Touch Bar的MacBook Pro笔记本电脑的电路图、原理图和点位图,具体文档名为APPLE 820-00840-A.pdf,主要用于维修用途。其中包含了关于电源传感器、SMBus连接、SMC项目支持、电源管理集成电路(PMIC)等多个关键组件的详细信息。

这份资料详细列出了电脑主板上的各个组件和连接,包括但不限于电源传感器的分布(如PowerSensorsExtended、PowerSensorsHighSide、PowerSensorsLoadSide),CPU和PCH(平台控制器 hub)的电源管理(如CPUIMVPVCC&VCCSA、PBUSSupply&BatteryCharger),电压调节模块(VReg)以及电池充电器,还有DC-IN和电池连接器的布局。

此外,资料还提到了JACKTRANSLATORS,这可能是指音频接口的转换电路,以及LCD背光驱动、电源栅极(PowerFETs)、电源去耦电容(RAILDESENSECAPS)、PMIC的多种电压输出(如1.2V、1.0V、0.6V、VCCPCH、VCCIO1.8V)。同时,它涵盖了芯片组支持的相关部分,如LPDDR3内存参考电压校准、CPU/PCH合并的eDP接口、PCH的SPI、UART、GPIO接口,以及CPU核心去耦合和电源设计。

文档还详细描述了CPU的LPDDR3接口、杂项电路(CPUMISC)、JTAG配置、SPI ROM及SWD调试接口,HDMI桥接器、音频编解码器、扬声器放大器等关键硬件组件的位置和连接关系。

这些信息对于专业维修人员来说至关重要,他们可以凭借这些图纸定位和识别故障部件,进行有效的诊断和维修。同时,这些数据也可以帮助理解电脑内部的工作原理,对硬件升级或定制也有一定的指导价值。合肥怡飞苹果维修提供相关的技术支持,可以通过提供的QQ联系方式寻求帮助。

合肥怡飞苹果维修qq:82669515

qq群: 241000

FILTER PLACEHOLDERS ONLY

PCH SIDERAIL SIDE

FOR FUTURE PRODUCT PER PDG

CPU CIRCUITS GENERATE NOISE AT WIFI BAND FREQUENCIES.

USE SPECIFIC 3PF CAPS FOR BEST FILTERING OF THOSE FREQUNCIES.

12 OF 73

12 OF 500

1.0.0

051-02265

=PP1V_SUS_PCH_VCCCLK5_SRC

=PP1V_SUSSW_PCH_VCCAPLLEBB

=PP3V3_SUS_PCH_VCCPRIM

MAKE_BASE=TRUE

PP1V_SUS_PCH_VCCCLK5_F=PP3V3_SUS_PCH_VCCPGPPC

=PP1V_SUS_PCH_VCCCLK4_SRC

MAKE_BASE=TRUE

PP1V8_SUS_PCH_VCC1P8

=PP1V8_SUS_PCH_VCC1P8_SRC

=PP3V3_SUS_PCH_VCCRTCPRIM

=PP1V_SUS_PCH_VCCCLK2=PP1V_SUS_PCH_VCCCLK2_SRC

=PP1V8_SUS_PCH_VCCATS

MAKE_BASE=TRUE

PP1V8_S0_PCH_VCCHDA_F

MAKE_BASE=TRUE

PP1V_SUS_PCH_VCCAPLL_F

MAKE_BASE=TRUE

PP1V_SUS_PCH_VCCCLK4_F

=PP1V_SUS_PCH_VCCCLK4

=PP3V3_SUS_PCH_VCCPGPPE

=PP1V8_SUS_PCH_VCC1P8_U12

=PP1V_SUSSW_PCH_VCCAMPHYPLL_SRC

MAKE_BASE=TRUE

PP1V_SUS_PCH_VCCCLK2_F

=PP1V_SUS_PCH_VCCCLK5

=PP1V_SUS_PCH_VCCCLK6

=PP1V_SUSSW_PCH_VCCSRAM

=PP3V3_SUS_PCH_VCCPGPPB

MAKE_BASE=TRUE

PP1V_SUSSW_PCH_VCCAMPHYPLL_F

=PP1V_SUSSW_PCH_VCCAMPHYPLL

=PP1V8_SUS_PCH_VCC1P8_U11

=PP1V8_S0_PCH_VCCHDA_F

PP1V_S5_PCH_DCPDSW

=PP1V8_S0_PCH_VCCHDA

=PPVCCPRIMECORE_SUS_PCH

=PP1V_SUS_PCH_VCCAPLL

=PP1V_SUS_PCH_VCCMPHYAON

=PP3V_G3H_PCH_VCCRTC

=PP1V_SUS_PCH_VCCAPLL_F

PPDCPRTC_PCH

=PP1V_SUS_PCH_VCCPRIM

=PP1V_SUS_PCH_FUSE

=PP1V_SUSSW_PCH_VCCMPHYGT

L1250,L1252,L1253,L1254RES,MF,1A MAX,0OHM,5%,06034113S0022

SYNC_DATE=06/15/2015SYNC_MASTER=PAULM

PCH Decoupling

BOM_COST_GROUP=CPU & CHIPSET

0201

X7R

25V

10%

BYPASS=U0500.AK20::10MM

1000PF

2

1

C1208

0201

C0G-CERM

25V

+/-0.05PF

2.9PF

CRITICAL

2

1

C1267

0201

CERM

25V

5%

12PF

2

1

C1264

0201

C0G-CERM

25V

+/-0.05PF

2.9PF

CRITICAL

2

1

C1265

0201

MF

1/20W

5%

0

21

R1261

0201

X7R

25V

10%

BYPASS=U0500.V15::10MM

1000PF

2

1

C1261

0201

C0G-CERM

25V

+/-0.05PF

BYPASS=U0500.V15::10MM

2.9PF

CRITICAL

2

1

C1262

0201

MF

1/20W

5%

0

21

R1260

0201

X7R

25V

10%

BYPASS=U0500.AJ19::10MM

1000PF

2

1

C1226

0201

MF

1/20W

5%

0

NOSTUFF

21

R1251

0201

X6S-CERM

6.3V

20%

BYPASS=U0500.U11::10MM

1UF

NOSTUFF

2

1

C1251

0603

2.2UH-240MA-0.221OHM

OMIT_TABLE

21

L1254

0805

POLY-TANT

6.3V

20%

47UF

CRITICAL

NOSTUFF

2

1

C1254

0603

2.2UH-240MA-0.221OHM

OMIT_TABLE

21

L1253

0805

POLY-TANT

6.3V

20%

47UF

CRITICAL

NOSTUFF

2

1

C1253

0603

2.2UH-240MA-0.221OHM

OMIT_TABLE

21

L1252

0805

POLY-TANT

6.3V

20%

47UF

CRITICAL

NOSTUFF

2

1

C1252

0805

POLY-TANT

6.3V

20%

BYPASS=U0500.K15::3MM

47UF

CRITICAL

NOSTUFF

2

1

C1250

0603

2.2UH-240MA-0.221OHM

OMIT_TABLE

21

L1250

0201

X6S-CERM

6.3V

20%

BYPASS=U0500.AL1::3MM

1UF

2

1

C1232

0201

X5R-CERM

10V

10%

BYPASS=U0500.BB10::3MM

0.1UF

2

1

C1231

0201

X5R-CERM

10V

10%

BYPASS=U0500.AK19::3MM

0.1UF

2

1

C1228

0201

X5R-CERM

10V

10%

BYPASS=U0500.AK17::3MM

0.1UF

2

1

C1222

0805

POLY-TANT

6.3V

20%

BYPASS=U0500.N15::10MM

47UF

CRITICAL

NOSTUFF

2

1

C1203

0201

X6S-CERM

6.3V

20%

BYPASS=U0500.AA1::10MM

1UF

2

1

C1230

0201

X6S-CERM

6.3V

20%

BYPASS=U0500.AK19::3MM

1UF

2

1

C1227

0201

C0G-CERM

25V

+/-0.05PF

BYPASS=U0500.AJ19::10MM

2.9PF

CRITICAL

2

1

C1260

0201

X7R

25V

10%

BYPASS=U0500.Y16::10MM

1000PF

2

1

C1225

0201

X7R

25V

10%

BYPASS=U0500.V19::10MM

1000PF

2

1

C1224

0201

X7R

25V

10%

BYPASS=U0500.AG15::3MM

1000PF

2

1

C1223

0201

X6S-CERM

6.3V

20%

BYPASS=U0500.AK17::3MM

1UF

2

1

C1221

0201

X7R

25V

10%

BYPASS=U0500.T16::3MM

1000PF

2

1

C1220

0201

X7R

25V

10%

BYPASS=U0500.AF18::10MM

1000PF

2

1

C1210

0201

X7R

25V

10%

BYPASS=U0500.A10::3MM

1000PF

2

1

C1207

0201

X6S-CERM

6.3V

20%

BYPASS=U0500.N18::3MM

1UF

2

1

C1206

0201

X7R

25V

10%

BYPASS=U0500.AF20::10MM

1000PF

2

1

C1205

0201

X6S-CERM

6.3V

20%

1UF

2

1

C1204

0201

X6S-CERM

6.3V

20%

BYPASS=U0500.N15::3MM

1UF

2

1

C1202

0201

X6S-CERM

6.3V

20%

BYPASS=U0500.K17::3MM

1UF

2

1

C1201

0201

X7R

25V

10%

BYPASS=U0500.AB19::10MM

1000PF

2

1

C1200

69

69 8

69 8 5

69 8

69

69

69 8

8 69

69 8

72

72

8

69 8

5

69

8

69 8

69 8

69 19 8

8

5

8

8

69

69 8

69 15

69 8

69 15 14 8

8

8

69 8

64 8

69 8

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

THE POSESSOR AGREES TO THE FOLLOWING:

36

BRANCH

REVISION

DRAWING NUMBER SIZE

D

R

IV ALL RIGHTS RESERVED

SHEET

PAGE TITLE

C

A

D

2 1

PAGE

NOTICE OF PROPRIETARY PROPERTY:

A

B

C

345678

D

B

8 7 5 4 2 1

PROPRIETARY PROPERTY OF APPLE INC.

THE INFORMATION CONTAINED HEREIN IS THE

Apple Inc.

CRITICALPART NUMBER QTY BOM OPTIONREFERENCE DESDESCRIPTION

合肥怡飞苹果维修qq:82669515

qq群: 241000

(STRAP)

PCH INTERNAL PULL-UPS ARE TO 3.3V.

IO1

IO0

(STRAP)

(STRAP)

(STRAP)

(STRAP)

DESIGN: X502/MLB_CATZ

LAST CHANGE: Thu Aug 4 21:00:42 2016

(1.8V)

(STRAP)

(BSSB_DATA_IN)

(BSSB_CLK)

(1.8V)

MEMORY CONFIGURATION STRAPS.

ALL GPP_F* PINS ARE 1.8V ONLY!

13 OF 73

13 OF 500

1.0.0

051-02265

=PP3V3_SUS_PCH_VCCPGPPA

=PP3V3_S0_PCH

HDA_SYNC_R

HDA_SDOUT_R

HDA_RST_R_L

XDP_PCH_OBSDATA_C0

SML_PCH_1_DATA

HDA_BIT_CLK_R

HDA_SDIN0

LPC_AD_R<1>

=USBC_TMS_X_SWD_CLK_X

MLB_RAMCFG1

SPI_IO<2>

MLB_RAMCFG2

BT_PWRRST_L

SPI_CS0_R_L

LPC_SERIRQ

SOC_ALS_UART_D2R

PCH_BSSB_CLK

MLB_RAMCFG3

PCH_UART2_CTS_L

LCD_PSR_EN

TBT_X_CIO_PWR_EN

HDA_SDOUT

HDA_BIT_CLK

HDA_SYNC

HDA_RST_L

LPC_SERIRQ

TP_SPI_CS2_L

SPI_IO<3>

SPI_CLK_R

PU_PCH_RCIN_L

=USBC_TMS_T_SWD_DATA_X

TP_SPI_CS1_L

SPI_CS0_R_L

SPI_MISO

PCH_DDPC_CTRLDATA

MLB_RAMCFG0

PCH_BSSB_DATA

MLB_RAMCFG3

MLB_RAMCFG2

MLB_RAMCFG1

LPC_AD_R<0>

LPC_AD_R<2>

LPC_AD_R<3>

LPC_FRAME_R_L

LPC_CLK24M_SMC_R

SSD_PWR_EN_L

LPC_AD<1>

LPC_AD<2>

LPC_AD<3>

LPC_FRAME_L

LPC_CLK24M_SMC

LPC_AD<0>

PCH_DDPB_CTRLDATA

PCH_STRP_TOPBLK_SWP_L

CAMERA_PWR_EN_PCH

CAMERA_RESET_L

SOC_ALS_UART_D2R

SOC_ALS_UART_R2D

SOC_ALS_UART_R2D

PCH_UART2_CTS_L

PCH_SOC_WDOG

SD_RCOMP

PCH_STRP_BSSB_SEL_GPIO

TP_PCH_STRP_TLSCONF

TP_PCH_STRP_ESPI

SMBUS_PCH_CLK

SMBUS_PCH_DATA

SML_PCH_0_CLK

SML_PCH_0_DATA

LPC_PWRDWN_L

TP_PCH_CLKOUT_LPC1

LPC_CLKRUN_L

LCD_PSR_EN

MLB_RAMCFG4

MLB_RAMCFG0

SPI_MOSI_R

=USBC_TMS_T_SWD_DATA_X

TBT_X_CIO_PWR_EN

SOC_S2R_ACK_L

PCH_SOC_DFU_STATUS

TBT_X_USB_PWR_EN

SOC_PANIC_L

=USBC_TMS_X_SWD_CLK_X

SML_PCH_1_CLK

DEBUGUART_SEL_SOC

SOC_SLEEP_L

TBT_X_USB_PWR_EN

CAMERA_PWR_EN

BT_TIMESTAMP

=PP3V3_SUS_PCH_VCCSPI

LPC_CLKRUN_L

PU_PCH_RCIN_L

RAMCFG4_L,RAMCFG3_L,RAMCFG2_L,RAMCFG1_L,RAMCFG0_LRAMCFG_SLOT

SYNC_DATE=06/15/2015

PCH Audio/LPC/SPI/SMBus

SYNC_MASTER=PAULM

BOM_COST_GROUP=CPU & CHIPSET

201MF1/20W5%

10K

21

R1344

201MF1/20W5%

1K

21

R1343

70

70

67

201MF1/20W5%

PLACE_NEAR=U0500.AW9:38MM

22

21

R1327 39

201MF1/20W5%

10K

21

R1342

201MF1/20W5%

100K

21

R1359

201MF1/20W5%

100K

21

R1340

201MF1/20W5%

100K

21

R1341

39 13

201

MF

1/20W

5%

1K

RAMCFG4_L

2

1

R1334

201

MF

1/20W

5%

1K

RAMCFG3_L

2

1

R1333

201

MF

1/20W

5%

1K

RAMCFG2_L

2

1

R1332

201

MF

1/20W

5%

1K

RAMCFG1_L

2

1

R1331

201

MF

1/20W

5%

1K

RAMCFG0_L

2

1

R1330

201MF1/20W5%

100K

21

R1358

201MF1/20W5%

10K

21

R1356

201MF1/20W5%

100K

21

R1357

201MF1/20W5%

10K

21

R1355

201MF1/20W5%

47K

21

R1354

201MF1/20W5%

47K

21

R1353

201MF1/20W5%

47K

21

R1352

201MF1/20W5%

100K

CAMERA_PWR_EN:S0

21

R1351

201MF1/20W5%

10K

21

R1350

42

42

19 13

19 13

19 13

19 13

19

36 19

28 13

28 13

40

17

201

MF

1/20W

1%

PLACE_NEAR=U0500.AB7:12.7MM

200

2

1

R1370

70

70

47 13

47

47 17

47

47

47

39

201MF1/20W5%

33

21

R1325

42

42

42

42

201MF1/20W5%

33

21

R1320

201MF1/20W5%

33

21

R1322

201MF1/20W5%

33

21

R1321

201MF1/20W5%

33

21

R1323

39

39

39

39

39

39 13

BGA

TBD

SKL-ULT-2+3E

OMIT_TABLE

AV3

AW3

AU4

AW2

AU1

AU2

AU3

AV2

U4

U3

AD4

AD3

AD2

AD1

V3

W3

W1

W2

R9

R10

R8

R7

AM7

BA11

AY9

AW9

AW11AY11

BA12

AY12

BB13

BA13

AY13

AW13

G1

G2

G3

U0500

19

28 13

28 13

19

48

201MF1/20W5%

PLACE_NEAR=U0500.AY22:14MM

33

21

R1301

201MF1/20W5%

PLACE_NEAR=U0500.BA22:14MM

33

21

R1300

48

201MF1/20W5%

PLACE_NEAR=U0500.AW22:14MM

33

21

R1303

201MF1/20W5%

PLACE_NEAR=U0500.BB22:14MM

33

21

R1302

48

48

48

BGA

TBD

SKL-ULT-2+3E

OMIT_TABLE

AB7

AW20

AY20

BA22

BB22

AY21

BA21

AW22

AY22

AB13

AB11

AF13

AM3

AM2

AM1

AM4

AN2

AN1

N8

N7

L12

L13

D8

U2

U1

P1

P4

AW5

BA9

BB9

U0500

69 16 15 14 8

69 60 19 16 14 5

18

13

13

6

47 13

39 13

13

28 13

70

13

70

13

13

13

13

19 13

19 13

19 13

19

70

70

70

19 13

6

13

28 13

70

70

70

28 13

70

28 13

36 19

6

69 47 8

39 13

13

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

THE POSESSOR AGREES TO THE FOLLOWING:

36

BRANCH

REVISION

DRAWING NUMBER SIZE

D

R

IV ALL RIGHTS RESERVED

SHEET

PAGE TITLE

C

A

D

2 1

PAGE

NOTICE OF PROPRIETARY PROPERTY:

A

B

C

345678

D

B

8 7 5 4 2 1

PROPRIETARY PROPERTY OF APPLE INC.

THE INFORMATION CONTAINED HEREIN IS THE

Apple Inc.

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_HEAD

BOM GROUP BOM OPTIONS

IN

OUT

OUT

OUT

IN

BI

OUT

IN

IN

OUT

OUT

OUT

OUT

OUT

OUT

IN

OUT

NC

NC

NC

IN

IN

OUT

BI

BI

BI

BI

OUT

OUT

BI

OUT

BI

OUT

OUT

BI

BI

BI

BI

BI

LPC

SPI-TOUCH

SPI-FLASH

SMBUS,SMLINK

SYM 5 OF 20

C LINK

SML0BALERT*

GPP_A9/CLKOUT_LPC0/ESPI_CLK

GPP_A14/SUS_STAT*/ESPI_RESET*

GPP_B23/SML1ALERT*/PCHHOT*

GPP_A4/LAD3/ESPI_IO3

GPP_A5/LFRAME*/ESPI_CS*

GPP_A3/LAD2/ESPI_IO2

GPP_A1/LAD0/ESPI_IO0

GPP_A2/LAD1/ESPI_IO1

GPP_C6/SML1CLK

GPP_C7/SML1DATA

GPP_C5/SML0ALERT*

GPP_C3/SML0CLK

GPP_C4/SML0DATA

GPP_C0/SMBCLK

GPP_C1/SMBDATA

GPP_C2/SMBALERT*

GPP_A8/CLKRUN*

GPP_A10/CLKOUT_LPC1

SPI0_CS0*

SPI0_MISO

SPI0_CLK

SPI0_MOSI

SPI0_IO2

SPI0_IO3

SPI0_CS1*

CL_CLK

SPI0_CS2*

GPP_C21/UART2_TXD

GPP_C20/UART2_RXD

GPP_D16/ISH_UART0_CTS*/

GPP_C22/UART2_RTS*

GPP_C23/UART2_CTS*

GPP_D15/ISH_UART0_RTS*

CL_DATA

CL_RST*

GPP_A0/RCIN*

GPP_A6/SERIRQ

IN

BI

OUT

IN

NC

NC

OUT

NC

IN

OUT

OUT

OUT

AUDIO

SML0BDATA/I2C4B_SDA

SML0BCLK/I2C4B_SCL

SDIO/SDXC

SYM 7 OF 20

SD_RCOMP

GPP_F17/EMMC_DATA4

GPP_A16/SD_1P8_SEL

GPP_A17/SD_PWR_EN*/ISH_GP7

GPP_G0/SD_CMD

GPP_G1/SD_DATA0

GPP_F22/EMMC_CLK

GPP_F23

GPP_F19/EMMC_DATA6

GPP_F21/EMMC_RCLK

GPP_F20/EMMC_DATA7

GPP_F18/EMMC_DATA5HDA_SDI1/I2S1_RXD

HDA_SDI0/I2S0_RXD

HDA_SDO/I2S0_TXD

HDA_BLK/I2S0_SCLK

HDA_SYNC/I2S0_SFRM

I2S1_TXD

I2S1_SFRM

GPP_D17/DMIC_CLK1

GPP_E21/DDPC_CTRLDATA

GPP_E18/DDPB_CTRLCLK

HDA_RST*/I2S1_SCLK

GPP_E19/DDPB_CTRLDATA

GPP_E20/DDPC_CTRLCLK

GPP_D11

GPP_D12

GPP_B14/SPKR

GPP_D13/ISH_UART0_RXD/

GPP_D14/ISH_UART0_TXD/

合肥怡飞苹果维修qq:82669515

qq群: 241000

NOTE: PM_SLP_S0_L HAS INTERNAL PULL-UP BEFORE RSMRST_L IS RELEASED.

THE SIGNAL IS DRIVEN HI AFTER RSMRST_L IS RELEASED.

PCH Reset Button

R1400 kept for debug purposes.

VCCST_PWRGD 1V TOLERANT

(1.8V)

LAST CHANGE: Thu Aug 4 21:00:42 2016

DESIGN: X502/MLB_CATZ

ALL GPP_F* PINS ARE 1.8V ONLY!

(1V ONLY)

THIS CAUSES A VOLTAGE DIVIDER WITH THE PULL-DOWN HERE.

14 OF 73

14 OF 500

1.0.0

051-02265

PCH_SWD_CLK

SSD_SR_EN_L

PCIE_WAKE_L

PCH_PWRBTN_L

SMC_WAKE_SCI_L

PM_SLP_S4_L

PM_SLP_SUS_L

PCIE_WAKE_L

PCH_SOC_FORCE_DFU

TP_PCH_GPP_F8

TP_PCH_PME_L

TP_PCH_SLP_WLAN_L

PCH_SUSWARN_L

PCH_INTRUDER_L

BT_LOW_PWR_L

PCH_SWD_MUX_SEL

PM_SLP_S4_L

PM_SLP_S5_L

PM_PCH_SYS_PWROK =PP3V_G3H_PCH_VCCRTC

PM_SLP_SUS_L

=PP1V_S3_CPU_VCCST

TP_PCH_GPP_F9

TP_PCH_GPP_D0

SMC_WAKE_SCI_L

SSD_BOOT_L

EMMC_RCOMP

SSD_SR_EN_L

TP_PCH_SLP_A_L

PM_SLP_S3_L

PM_SLP_S0_L

PCH_PWRBTN_L

PM_BATLOW_L

TP_CPU_PWRGD

PM_SLP_S0_L

TP_PCH_GPD7

PCH_HSIO_PWR_ENTP_PCH_LANPHYPC

UPC_I2C_INT_L

SOC_S2R_L

CSI2_COMP

TP_PCH_GPP_F10

PCH_SWD_CLK

PCH_SWD_IO

PCH_BT_ROM_BOOT

CPU_VCCST_PWRGD

=PP3V3_S0_PCH

PCH_SUSACK_L

=PP3V3_SUS_PCH_VCCPGPPA

PCH_SWD_IO

BT_LOW_PWR_L

=PP1V8_SUS_PCH_VCCPGPPF

PM_SLP_S3_L

=PP3V3_S4_PCH

SOC_S2R_L

=PP3V3_S0_PCH

=PP3V3_S5_PCH_VCCDSW

CPU_VCCST_PWRGD_R

PM_PCH_PWROK

PM_DSW_PWRGD

PM_RSMRST_L

PM_SYSRST_L

PLT_RST_L

PM_SLP_S5_L

PM_BATLOW_L

SSD_BOOT_L

PCH_SWD_MUX_SEL

BOM_COST_GROUP=CPU & CHIPSET

SYNC_DATE=06/15/2015SYNC_MASTER=PAULM

PCH Power Management

41

BGA

TBD

SKL-ULT-2+3E

OMIT_TABLE

AN3

AP3

AP1

AP2

AP4

AD12

AD11

AF12

AF11

AH12

AH11

M1

AT1D27

B27

D28

B29

B33

B31

D33

D31

B38

D36

D38

B36

C27

A27

C28

A29

A33

A31

C33

C31

A38

C36

C38

A36

E13

A26

D29

D32

D37

B26

C29

C32

C37

U0500

BGA

TBD

SKL-ULT-2+3E

OMIT_TABLE

BB15

B65

B5

B6

AN15

AW15

AY17

A68

BA20

AP16

AN10

AT11

AM10

AM11

AP11

AR13

AU11

AW17

AY16

BB17

AT15

AN16

BA16

AP15

BA15

AM15

AY15

AU13

BB20

U0500

201

MF

1/20W

5%

2.2K

2

1

R1408

201MF1/20W5%

10K

21

R1441

70

60

72 60 39 14

201MF1/20W5%

100K

21

R1446

100K

201MF1/20W5%

21

R1445

100K

5% 1/20W MF 201

21

R1444

NOSTUFF

100K

2015% MF1/20W

21

R1443

201MF1/20W5%

100K

21

R1442

MF 2011/20W5%

100K

21

R1440

19 14

19 14

19 14

NOSTUFF

201

MF

1/20W

5%

2.2K

2

1

R1407

201 MF 1/20W

1%

PLACE_NEAR=U0500.B65:38mm

60.4

21

R1406

201

MF

1/20W

5%

1K

2

1

R1405

MF 2011/20W5%

100K

21

R1458

MF 2011/20W5%

100K

21

R1456

201MF1/20W5%

220K

21

R1457

MF 2011/20W5%

100K

21

R1454

201MF1/20W5%

100K

21

R1455

201MF1/20W5%

10K

21

R1452

10K

201MF1/20W5%

21

R1451

201MF1/20W5%

1K

21

R1450

5% 201MF1/20W

100K

21

R1453

70

67 14

35 34 14

39 14

201

MF

1/20W

1%

PLACE_NEAR=U0500.AT1:12.7MM

200

2

1

R1481

201

MF

1/20W

1%

PLACE_NEAR=U0500.E13:12.7MM

100

2

1

R1480

201

MF

1/20W

5%

1M

2

1

R1401

39 28 14

67 14

72 60 14

72 60 39 14

72 68 60 39 14

72 66

60 59 39 26 14

18 14

68 39

201

MF

1/20W

5%

100K

2

1

R1403

60

68 35 19

68 39 17

41 14

68 60 39 17

60 19

60 59 39

41

0201

MF

1/20W

5%

0

NO STUFF

1

2

R1400

19 14

67 14

18 14

41 14

39 14

72 68 60 39 14

72 60 14

70

70

70

69 15 12 8

69 59 54 19 10 8 6

70

70

72

72 60 39 14

70

70

19 14

70

70

69 60 19 16 14 13 5

69 16 15 13 8

19 14

35 34 14

69 8

72 66 60 59 39 26 14

69

19 14

69 60 19 16 14 13 5

69 8

72

72 60 39 14

39 28 14

67 14

19 14

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

THE POSESSOR AGREES TO THE FOLLOWING:

36

BRANCH

REVISION

DRAWING NUMBER SIZE

D

R

IV ALL RIGHTS RESERVED

SHEET

PAGE TITLE

C

A

D

2 1

PAGE

NOTICE OF PROPRIETARY PROPERTY:

A

B

C

345678

D

B

8 7 5 4 2 1

PROPRIETARY PROPERTY OF APPLE INC.

THE INFORMATION CONTAINED HEREIN IS THE

Apple Inc.

IN

EMMC

CSI-2

SYM 9 OF 20

CSI2_COMP

GPP_D0/SPI1_CS*

GPP_F7/I2C3_SCL

CSI2_DN8

CSI2_DP11

CSI2_DN11

CSI2_DP10

CSI2_DN10

CSI2_DP9

CSI2_DN9

CSI2_DP8

CSI2_DP7

CSI2_DN7

CSI2_DP6

CSI2_DN6

CSI2_DP5

CSI2_DN5

CSI2_DP4

CSI2_DN4

CSI2_DP3

CSI2_DN3

CSI2_DP2

CSI2_DN0

CSI2_DP0

CSI2_DN1

CSI2_DP1

CSI2_DN2

EMMC_RCOMP

GPP_F11/I2C5_SCL/ISH_I2C2_SCL

GPP_F12/EMMC_CMD

GPP_F13/EMMC_DATA0

GPP_F14/EMMC_DATA1

GPP_F15/EMMC_DATA2

GPP_F16/EMMC_DATA3

GPP_F6/I2C3_SDA

GPP_F10/I2C5_SDA/ISH_I2C2_SDA

CSI2_CLKN3

CSI2_CLKP3

CSI2_CLKP2

CSI2_CLKN2

CSI2_CLKN0

CSI2_CLKP0

CSI2_CLKP1

CSI2_CLKN1

GPP_F8/I2C4_SDA

GPP_F9/I2C4_SCL

SYSTEM POWER MANAGEMENT

SYM 11 OF 20

GPP_B12/SLP_S0*

GPD5/SLP_S4*

GPD4/SLP_S3*

GPD10/SLP_S5*

SLP_SUS*

GPD9/SLP_WLAN*

GPD6/SLP_A*

SLP_LAN*

GPD3/PWRBTN*

GPD1/ACPRESENT

GPD0/BATLOW*

GPP_A11/PME*

INTRUDER*

GPP_B11/EXT_PWR_GATE*

GPP_B2/VRALERT*

GPP_B13/PLTRST*

SYS_RESET*

RSMRST*

PROCPWRGD

SYS_PWROK

VCCST_PWRGD

DSW_PWROK

PCH_PWROK

GPP_A15/SUSACK*

GPP_A13/SUSWARN*/SUSPWRDNACK

WAKE*

GPD2/LAN_WAKE*

GPD11/LANPHYPC

GPD7/RSVD

OUT

OUT

OUT

BI

OUT

OUT

IN

OUT

NC

OUT

IN

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

IN

OUT

OUT

OUT

OUT

OUT

IN

IN

IN

OUT

IN

IN

IN

IN

IN

OUT

合肥怡飞苹果维修qq:82669515

qq群: 241000

EXT B (LS/FS/HS)

ANY CLKREQ CAN MAP TO ANY CLK.

ANY CLKREQ OR CLK CAN MAP TO ANY PCIE PORT.

UNUSED CLKREQS AND CLKS SHOULD BE DISABLED.

PCIe Port Assignments:

PER SKYLAKE PDG, SKYLAKE PCH EDS.

EXT A (LS/FS/HS)

EXT B (SS)

SSD LANE 3

SSD LANE 1

LAST CHANGE: Thu Aug 4 21:00:42 2016

DESIGN: X502/MLB_CATZ

EXT A (SS,DCI)

GROUNDED PER SKYLAKE MOW 2015WW10.

Thunderbolt X lane 0

Thunderbolt X lane 1

Thunderbolt X lane 3

Thunderbolt T lane 1

Thunderbolt T lane 0

AirPort

CAMERA

SSD LANE 2

SSD LANE 0

Thunderbolt X lane 2

15 OF 73

15 OF 500

1.0.0

051-02265

USB_EXTA_N

USB_EXTA_P

USB3_EXTB_R2D_C_P

TP_USB3_03_R2DP

TP_USB3_04_D2RN

TP_USB3_04_D2RP

NC_USB2_07P

NC_USB2_09P

NC_USB2_06P

NC_USB2_06N

PCH_USB2_COMP

TP_USB3_04_R2DP

PCIE_SSD_R2D_C_N<0>

PCIE_SSD_R2D_C_N<1>

PCIE_SSD_R2D_C_N<3>

PCIE_TBT_X_R2D_C_P<1>

TP_USB3_04_R2DN

PCIE_SSD_D2R_P<0>

XDP_PCH_OBSFN_C1

USB3_EXTB_D2R_P

NC_USB2_10P

USB3_EXTB_D2R_N

TP_USB_TESTERN

PCH_USB2_VBUSSENSE

NC_USB2_09N

NC_USB2_08N

=PP3V_G3H_PCH_VCCRTC

PCIE_TBT_X_D2R_N<1>

PCIE_TBT_X_R2D_C_P<3>

PCIE_AP_R2D_C_P

PCH_PCIE_RCOMP_P

PCIE_AP_R2D_C_N

PCIE_CAMERA_D2R_P

PCIE_CAMERA_R2D_C_N

PCH_DIFFCLK_BIASREF

PCH_SRTCRST_L

RTC_RESET_L=PP3V3_SUS_PCH_VCCPGPPA

PCH_CLK24M_XTALOUT

PCIE_SSD_D2R_N<1>

PCIE_SSD_D2R_P<1>

PCIE_SSD_D2R_N<2>

PCIE_SSD_D2R_P<3>

PCIE_TBT_X_D2R_N<2>

PCIE_TBT_X_R2D_C_N<3>

PCIE_SSD_R2D_C_P<3>

NC_USB2_08P

NC_USB2_07N

USB_CAMERA_DFR_N

NC_USB2_05N

TP_USB3_03_D2RN

TP_USB3_03_D2RP

SMC_RUNTIME_SCI_L

PCIE_SSD_R2D_C_P<0>

SPKR_ID0

PCIE_TBT_T_D2R_N<1>

PCIE_TBT_T_D2R_P<1>

PCIE_TBT_T_R2D_C_N<1>

PCIE_SSD_R2D_C_P<1>

PCIE_TBT_X_D2R_P<0>

PCIE_TBT_X_D2R_P<2>

XDP_CPU_PRDY_L

XDP_PCH_OBSDATA_A2

XDP_PCH_OBSDATA_C1

NC_USB2_10N

PCH_PCIE_RCOMP_N

PCIE_CLK100M_SSD_P

PCIE_CLK100M_SSD_N

=PP1V_SUS_PCH_VCCAPLL

PCIE_TBT_X_R2D_C_N<0>

PCIE_TBT_X_R2D_C_P<0>

PCIE_AP_D2R_P

PCIE_AP_D2R_N

PCIE_TBT_X_D2R_P<3>

PCIE_TBT_X_D2R_N<3>

PCIE_TBT_X_R2D_C_P<2>

XDP_PCH_OBSDATA_D0

XDP_PCH_OBSDATA_D1

XDP_PCH_OBSDATA_C3

XDP_PCH_OBSDATA_D3

PCIE_TBT_X_D2R_N<0>

USB_EXTB_N

PCIE_TBT_X_R2D_C_N<1>

PCIE_TBT_X_D2R_P<1>

PCIE_SSD_D2R_N<3>

PCIE_SSD_R2D_C_P<2>

PCIE_SSD_R2D_C_N<2>

PCIE_SSD_D2R_P<2>

PCIE_SSD_D2R_N<0>

PCIE_CLK100M_TBT_X_N

=TBT_X_CLKREQ_L

TP_PCH_CLKREQ5_L

TP_PCIE_CLK100M5P

TP_PCIE_CLK100M5N

PCIE_CLK100M_CAMERA_N

PCIE_CLK100M_AP_N

PCIE_CLK100M_TBT_T_N

=CAMERA_CLKREQ_L

PCIE_CLK100M_CAMERA_P

XDP_PCH_OBSDATA_C2

USB_CAMERA_DFR_P

TP_USB_TESTERP

NC_USB2_05P

USB_EXTB_P

USB3_EXTA_D2R_N

USB3_EXTA_D2R_P

USB3_EXTA_R2D_C_N

USB3_EXTA_R2D_C_P

USB3_EXTB_R2D_C_N

TP_USB3_03_R2DN

PCIE_TBT_X_R2D_C_N<2>

=AP_CLKREQ_L

PCIE_CLK100M_AP_P

=TBT_T_CLKREQ_L

PCIE_CLK100M_TBT_T_P

=SSD_CLKREQ_L

PCIE_CLK100M_TBT_X_P

XDP_JTAG_ISP_TDI

XDP_JTAG_ISP_TCK

PCIE_CAMERA_D2R_N

PCIE_CAMERA_R2D_C_P

PCH_CLK24M_XTALIN

PCH_CLK32K_RTCX2

PCH_CLK32K_RTCX1

XDP_CPU_PREQ_L

SMC_RUNTIME_SCI_L

PCIE_TBT_T_D2R_N<0>

PCIE_TBT_T_D2R_P<0>

PCIE_TBT_T_R2D_C_N<0>

PCIE_TBT_T_R2D_C_P<0>

PCIE_TBT_T_R2D_C_P<1>

TP_ITPXDP_CLK100MN

PM_CLK32K_SUSCLK_R

TP_ITPXDP_CLK100MP

BOM_COST_GROUP=CPU & CHIPSET

PCH PCIE/USB/CLKS

SYNC_MASTER=PAULM SYNC_DATE=06/15/2015

19

19

19

201MF1/20W5%

100K

21

R1550

70

70

70

70

70

70

70

70

28

28

28

28

28

28

28

28

28

28

28

28

28 19

28 19

28

28

70

70

70

26

19

26

19

67

67

19

35

35

37

19

37

17

17

17

17

17

17

17

17

17

17

72 67

72 67

72 67

72 67

72 67

72 67

72 67

72 67

72 67

72 67

72 67

72 67

72 67

72 67

72 67

72 67

37

37

37

37

72 35

72 35

72 35

72 35

39 15

70

70

201

MF

1/20W

1%

PLACE_NEAR=U0500.F5:12.7mm

100

2

1

R1504

BGA

TBD

SKL-ULT-2+3E

OMIT_TABLE

E35

E37

E42

AN18

AM20

AM18

AM16

AU7

AU8

AT10

AT8

AT7

AR10

BA17

E38

A40

C40

C41

A42

C42

E40

B40

D40

D41

B42

D42

E43

F43

U0500

201

MF

1/20W

1%

20K

2

1

R1531

201

MF

1/20W

1%

20K

2

1

R1530

0201

X6S-CERM

6.3V

20%

1UF

2

1

C1531

0201

X6S-CERM

6.3V

20%

1UF

2

1

C1530

201

MF

1/20W

1%

PLACE_NEAR=U0500.E42:2.54mm

2.7K

2

1

R1520

19

19

40

201

MF

1/20W

5%

PLACE_NEAR=U0500.AG4:12.7MM

1K

2

1

R1503

28

28

201

MF

1/20W

1%

PLACE_NEAR=U0500.AB6:12.7MM

113

2

1

R1501

70

70

28

28

28

28

70

70

70

70

72 17

72 17

BGA

TBD

SKL-ULT-2+3E

OMIT_TABLE

D15

C15

F10

E10

A15

B15

H10

J10

A13

B13

H6

J6

D13

C13

G8

H8

AH8

AG2

AF9

AH2

AF7

AJ2

AD10

AJ3

AD7

AB10

AH7

AG1

AF8

AH1

AF6

AJ1

AD9

AH3

AD6

AB9

AG4

AG3

AB6

D61

D56

E5

F5

B25

A25

F30

E30

C24

D24

E27

E28

C23

D23

E25

F25

A23

B23

E23

E22

C21

D21

F21

G21

A21

B21

E20

F20

C20

D20

F18

G18

D19

C19

E16

F16

A19

B19

F15

G15

C17

D17

G16

H16

C16

D16

F11

G11

A17

B17

G13

H13

J3

J2

J1

A6

G4

H2

J5

V2

D7

H5

C8

BB11

U0500

70

70

70

70

70

70

70

70

70

70

72

70

28

69 14 12 8

69 16 14 13 8

28

70

70

70

70

39 15

70

69 12

70

70

70

72

70

70

70

70

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

THE POSESSOR AGREES TO THE FOLLOWING:

36

BRANCH

REVISION

DRAWING NUMBER SIZE

D

R

IV ALL RIGHTS RESERVED

SHEET

PAGE TITLE

C

A

D

2 1

PAGE

NOTICE OF PROPRIETARY PROPERTY:

A

B

C

345678

D

B

8 7 5 4 2 1

PROPRIETARY PROPERTY OF APPLE INC.

THE INFORMATION CONTAINED HEREIN IS THE

Apple Inc.

IN

OUT

OUT

OUT

OUT

IN

IN

OUT

OUT

IN

IN

OUT

OUT

IN

IN

OUT

OUT

IN

IN

OUT

OUT

IN

IN

OUT

OUT

IN

IN

OUT

IN

OUT

OUT

IN

OUT

IN

OUT

OUT

IN

OUT

OUT

OUT

IN

OUT

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

OUT

IN

OUT

IN

OUT

OUT

IN

IN

OUT

OUT

IN

IN

OUT

IN

OUT

IN

OUT

OUT

IN

IN

OUT

IN

OUT

IN

IN

BI

BI

SYM 10 OF 20

CLOCK SIGNALS

CLKOUT_PCIE_P5

GPP_B10/SRCCLKREQ5*

CLKOUT_PCIE_N5

CLKOUT_PCIE_P4

GPP_B9/SRCCLKREQ4*

GPP_B8/SRCCLKREQ3*

CLKOUT_PCIE_N4

CLKOUT_PCIE_P3

CLKOUT_PCIE_N3

CLKOUT_PCIE_P2

GPP_B7/SRCCLKREQ2*

GPP_B6/SRCCLKREQ1*

CLKOUT_PCIE_N2

CLKOUT_PCIE_N1

CLKOUT_PCIE_P1

CLKOUT_PCIE_N0

GPP_B5/SRCCLKREQ0*

CLKOUT_PCIE_P0

CLKOUT_ITPXDP_N

GPD8/SUSCLK

CLKOUT_ITPXDP_P

XTAL24_OUT

XTAL24_IN

RTCX2

XCLK_BIASREF

RTCX1

SRTCRST*

RTCRST*

IN

IN

OUT

BI

BI

BI

BI

OUT

IN

IN

OUT

OUT

OUT

IN

IN

IN

OUT

SYM 8 OF 20

USB2

PCIE/USB3/SATA

SSIC/USB3

PCIE6_TXP

PCIE6_RXP

PCIE6_TXN

PCIE6_RXN

PCIE1_RXP/USB3_5_RXP

PCIE1_TXN/USB3_5_TXN

PCIE1_TXP/USB3_5_TXP

PCIE2_RXN/USB3_6_RXN

USB2N_2

USB2P_2

PCIE5_RXN

GPP_E2/SATAXPCIE2/SATAGP2

GPP_D20/DMIC_DATA0

GPP_D18/DMIC_DATA1

GPP_D19/DMIC_CLK0

GPP_E0/SATAXPCIE0/SATAGP0

GPP_D23/I2S_MCLK

GPP_E6/DEVSLP2

GPP_D22/SPI1_IO3

GPP_E4/DEVSLP0

GPP_E3/CPU_GP0

GPP_E5/DEVSLP1

USB2_ID

USB2_VBUSSENSE

USB2_COMP

USB2P_10

USB2P_9

USB2N_10

USB2N_9

USB2P_8

USB2P_7

USB2N_8

USB2N_7

USB2P_6

USB2P_5

USB2N_6

USB2N_5

USB2P_4

USB2P_3

USB2N_4

USB2N_3

USB2P_1

USB2N_1

USB3_4_TXP

USB3_4_TXN

USB3_4_RXN

USB3_4_RXP

USB3_1_TXP

USB3_1_TXN

USB3_1_RXP

USB3_1_RXNPCIE1_RXN/USB3_5_RXN

PCIE3_RXP

PCIE3_RXN

PCIE4_RXP

PCIE4_RXN

PCIE3_TXN

PCIE3_TXP

PCIE2_TXP/USB3_6_TXP

PCIE2_TXN/USB3_6_TXN

PCIE2_RXP/USB3_6_RXP

PCIE4_TXN

PCIE5_RXP

PCIE4_TXP

PCIE7_RXN/SATA0_RXN

PCIE7_RXP/SATA0_RXP

PCIE7_TXN/SATA0_TXN

PCIE7_TXP/SATA0_TXP

PCIE8_RXN/SATA1A_RXN

PCIE8_RXP/SATA1A_RXP

PCIE8_TXN/SATA1A_TXN

PCIE8_TXP/SATA1A_TXP

PCIE9_RXN

PCIE9_RXP

PCIE9_TXN

PCIE9_TXP

PCIE10_RXN

PCIE10_RXP

PCIE10_TXN

PCIE10_TXP

PCIE_RCOMPN

PCIE_RCOMPP

PROC_PRDY*

PROC_PREQ*

GPP_A7/PIRQA*

PCIE12_RXP/SATA2_RXP

PCIE12_RXN/SATA2_RXN

PCIE11_TXP/SATA1B_TXP

PCIE11_RXN/SATA1B_RXN

PCIE11_RXP/SATA1B_RXP

PCIE11_TXN/SATA1B_TXN

PCIE12_TXP/SATA2_TXP

PCIE12_TXN/SATA2_TXN

PCIE5_TXP

PCIE5_TXN

USB3_2_RXN/SSIC_RXN

USB3_2_RXP/SSIC_RXP

USB3_2_TXN/SSIC_TXN

USB3_2_TXP/SSIC_TXP

USB3_3_RXN

USB3_3_RXP

USB3_3_TXN

USB3_3_TXP

剩余72页未读,继续阅读

2023-05-28 上传

2020-02-29 上传

2011-07-01 上传

2012-10-07 上传

塘鱼

- 粉丝: 1

- 资源: 4

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- C语言快速排序算法的实现与应用

- KityFormula 编辑器压缩包功能解析

- 离线搭建Kubernetes 1.17.0集群教程与资源包分享

- Java毕业设计教学平台完整教程与源码

- 综合数据集汇总:浏览记录与市场研究分析

- STM32智能家居控制系统:创新设计与无线通讯

- 深入浅出C++20标准:四大新特性解析

- Real-ESRGAN: 开源项目提升图像超分辨率技术

- 植物大战僵尸杂交版v2.0.88:新元素新挑战

- 掌握数据分析核心模型,预测未来不是梦

- Android平台蓝牙HC-06/08模块数据交互技巧

- Python源码分享:计算100至200之间的所有素数

- 免费视频修复利器:Digital Video Repair

- Chrome浏览器新版本Adblock Plus插件发布

- GifSplitter:Linux下GIF转BMP的核心工具

- Vue.js开发教程:全面学习资源指南

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功