Xilinx Vivado IP Integrator与IP Catalog:高效整合与重用IP核心技术

需积分: 10 40 浏览量

更新于2024-07-17

1

收藏 2.3MB PPTX 举报

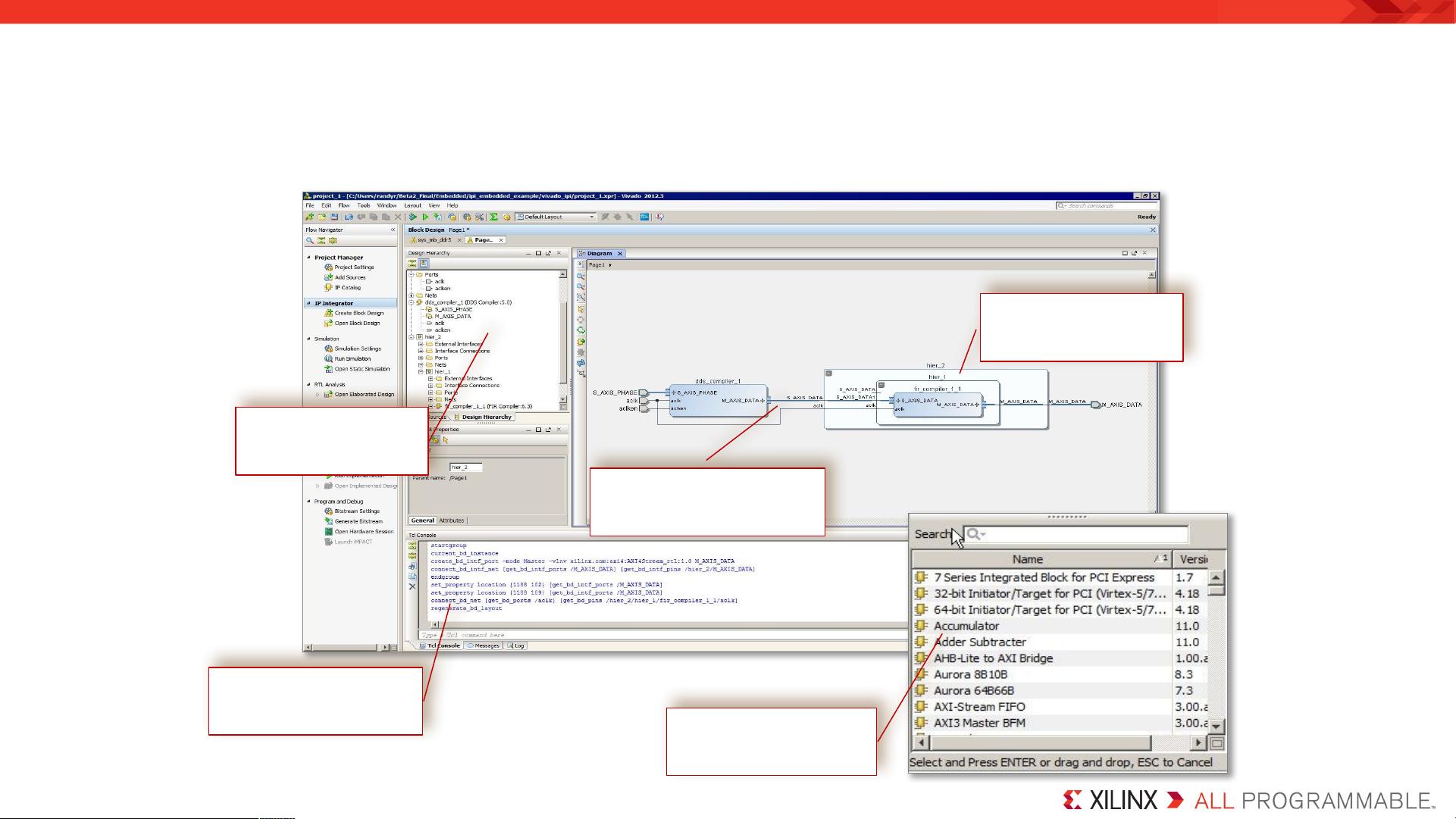

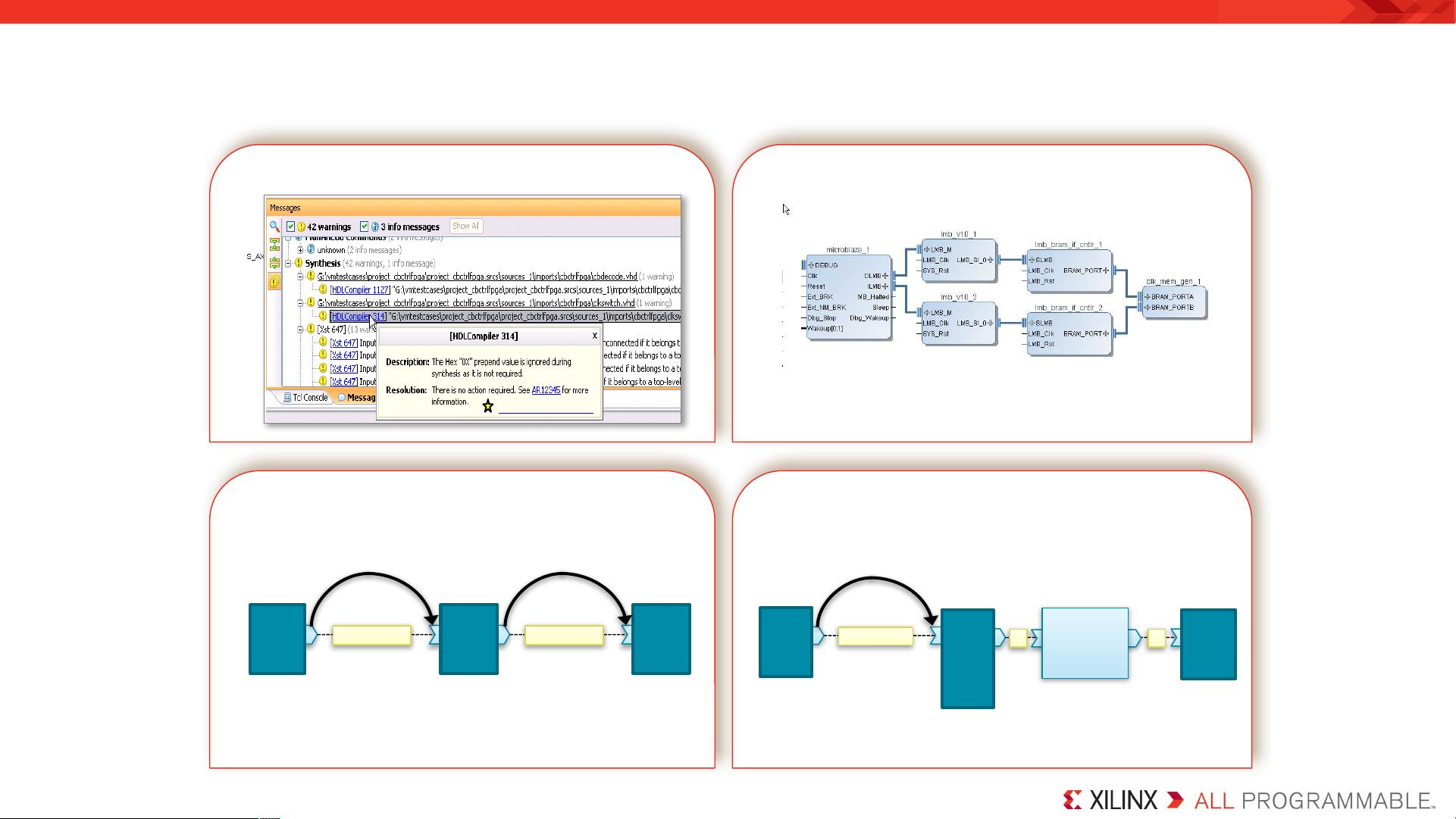

在Xilinx的设计流程中,"Xilinx-05-IPI And IP Catalog"这一教程详细探讨了如何有效地利用Xilinx Vivado 2013.4版本的IP Integrator工具和IP Catalog。此模块的主要目标是提升设计人员的工作效率,通过Vivado IP Integrator快速创建和复用子系统级别的IP,并了解IP核的封装与管理。

首先,IP Integrator是Vivado软件中的一个重要组件,它允许用户方便地集成各种预定义的IP核(如Zynq系列)到设计项目中。这些IP核通常包含了复杂的接口,如多个信号和复杂的端口映射,这在RTL设计中需要精心管理和配置。设计师需要理解这些接口的细节,确保在整个设计中保持一致性,同时处理不同IP块之间的交互。

IP Catalog是Xilinx提供的一个资源库,其中包含免费和基于评估的两种类型的IP。免费IP核可以直接用于设计,而评估版IP则可能带有使用期限或某些限制,但它们通常具有更高级的功能和特性。通过IP Catalog,设计师可以浏览、选择和导入适合他们项目的IP核,节省设计时间。

Clocking Wizard是IP Integrator中的另一个实用工具,它帮助设计师配置和添加时钟资源,这对于同步多块IP核以及确保时序完整性至关重要。通过这个工具,设计师可以轻松地管理设计中的时钟网络,避免潜在的时钟问题。

为了实现IP的高效复用,现代IP设计倾向于高度参数化,这意味着它们提供了丰富的可配置选项。然而,这也带来了挑战,因为设计师需要确保参数设置的一致性,尤其是在连接多个IP块构建复杂系统时。Vivado IP Integrator通过提供IP Packager功能,使得设计人员能够更好地组织和打包IP子系统,以便于后续的重复利用。

总结来说,"Xilinx-05-IPI And IP Catalog"教程涵盖了IP核在Xilinx设计中的关键环节,包括IP Integrator的使用技巧、IP Catalog的IP选择策略、Clocking Wizard的时钟管理,以及如何通过IP Packager来捕捉和优化IP复用。通过学习和实践这些内容,设计师将能显著提高他们的工作效率,并构建出更加模块化且易于维护的设计。

2021-10-03 上传

2021-10-02 上传

2022-08-04 上传

2022-09-21 上传

2021-03-05 上传

2021-03-19 上传

2021-02-14 上传

2021-02-13 上传

2021-04-06 上传

YanJ000

- 粉丝: 0

- 资源: 15

最新资源

- SAP BC400 课程中文自学笔记

- 北京邮电大学模拟电子技术课件

- Multi 9系列C65系列小型断路器产品目录

- TASCAM MD350快速使用手册.doc

- PLSQL教程.doc

- WAP Push SP接口协议

- Linux Socket Programming by Example [Que 2000 No-Bookmark].pdf

- oracle sql优化100条

- LPC_CAN接受滤波器AFMR设置.pdf

- ARM7数据手册.pdf

- Informix 常见问题处理

- ARM常见疑难问题答疑

- 480中文使用说明书

- 计算机二级 c++(45套试题)

- Spring 开发指南

- Direct3D9初级教程