使用Cyclone FPGA PLL在MODELSIM SE中的仿真教程

"该文介绍了Altera的Cyclone FPGA中的PLL(锁相环)在MODELSIM SE中的仿真步骤,以及PLL的基本硬件结构、功能和应用。PLL常用于同步内部和外部时钟,实现频率提升、相位偏移和时钟管理。Cyclone FPGA包含多个PLL,每个PLL有特定的时钟倍频和分频能力,可以进行精细的相位偏移调整,并能提供可编程的占空比。PLL的输出可以连接到逻辑阵列,且有锁定端口来检测是否已同步。在仿真过程中,会涉及到PLL的配置、时序分析和MegaWizard定制等功能。"

在Altera的Cyclone系列FPGA中,PLL(锁相环)是关键的时钟管理组件,它能够处理时钟倍频、分频、相位偏移以及占空比调整等任务,确保系统内部时钟与外部时钟的同步。PLL通常用于提高内部工作频率,减少时钟延迟和时钟偏移,优化时序性能。

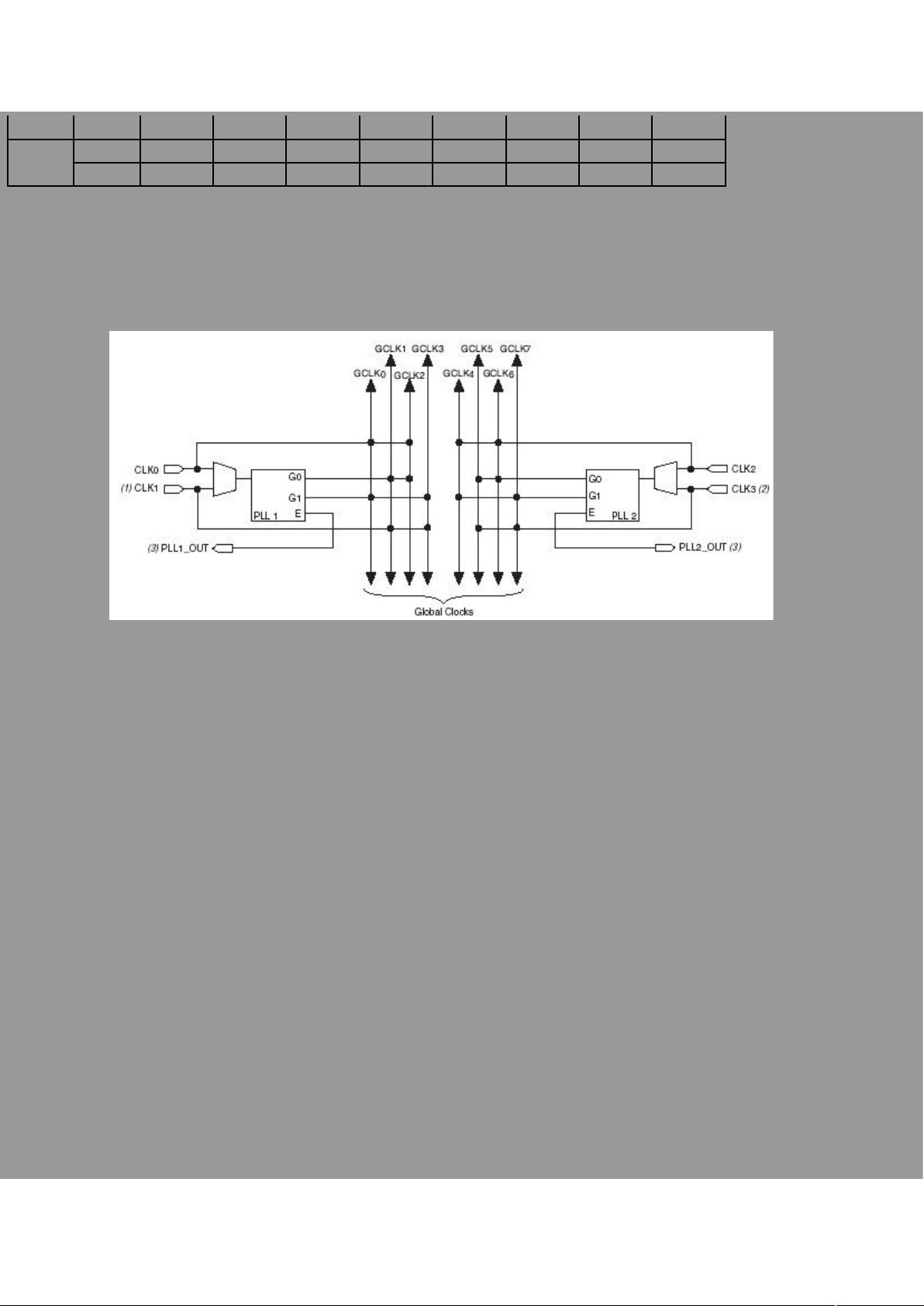

硬件结构上,每个Cyclone FPGA包含一个或两个PLL,具体数量因型号而异。PLL的功能包括时钟倍频(M/(N×后scale计数器))、相位偏移(最小156皮秒增量)、可编程占空比和多个输出。PLL的相位偏移可以精确到VCO(压控振荡器)周期的八分之一,角度调整最小增量为45º,这依赖于PLL的倍频/分频系数。每个PLL有两路内部时钟输出和一路外部时钟输出,但某些封装可能不支持所有特性,例如EP1C3不支持LVDS输出,EP1C6PLL2不支持外部时钟输出。

PLL的工作原理是通过相位频率检测器(PFD)比较参考输入时钟和反馈时钟的相位,根据两者之间的差异调整VCO的频率,从而实现相位同步。VCO产生的时钟经过分频器和倍频器调整后输出,占空比可以通过额外的控制逻辑进行编程。PLL的锁定端口用于指示系统是否已经稳定并同步到输入参考时钟。

在使用MODELSIM SE进行仿真的过程中,设计者需要了解如何配置PLL参数,如M、N和后scale计数器的值,以及如何设置相位偏移。此外,利用Altera的Quartus II软件和MegaWizard工具,可以自定义PLL的具体行为,以满足特定的设计需求。时序分析是仿真中的重要环节,它帮助验证PLL配置是否满足系统的时序约束。

理解Altera PLL在MODELSIM SE中的仿真步骤,包括其硬件结构、功能和配置方法,是成功设计和优化FPGA时钟系统的关键。通过详细的仿真和测试,设计者可以确保PLL在实际应用中能够有效地提高系统性能,同时保持时钟同步和稳定性。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2009-11-27 上传

114 浏览量

940 浏览量

1823 浏览量

863 浏览量

646 浏览量

ellvictor

- 粉丝: 0

- 资源: 3

最新资源

- HackUconn2021

- Extension Serial Gramera-crx插件

- 图像变换之小波变换.rar

- 现场监测员:Projeto desenvolvido durante o curso de Go da alura

- java笔试题算法-ARACNe-AP:通过互信息的AP推理进行网络逆向工程

- enas_model:使用ENAS自动构建深度学习模型

- Goldmine-crx插件

- 食品、百货部员工标准化服务及考核细则

- 荣誉

- 易语言源码易语言使用汇编调用子程序.rar

- laravel-wordful:只是Laravel的一个简单博客包

- Traffic-Signs-and-Object-Detection:这是我们的SIH 2018项目,可检测与交通相关的物体,例如交通标志,车辆等

- 初级java笔试题-cs-material:cs-材料

- Blogr-Landing-Page:前端导师的挑战

- 西点面包店长工作手册

- obs-studio.rar