MIPS寄存器文件设计:多路选择器与同步操作实现

需积分: 0 117 浏览量

更新于2024-06-30

收藏 2.57MB DOCX 举报

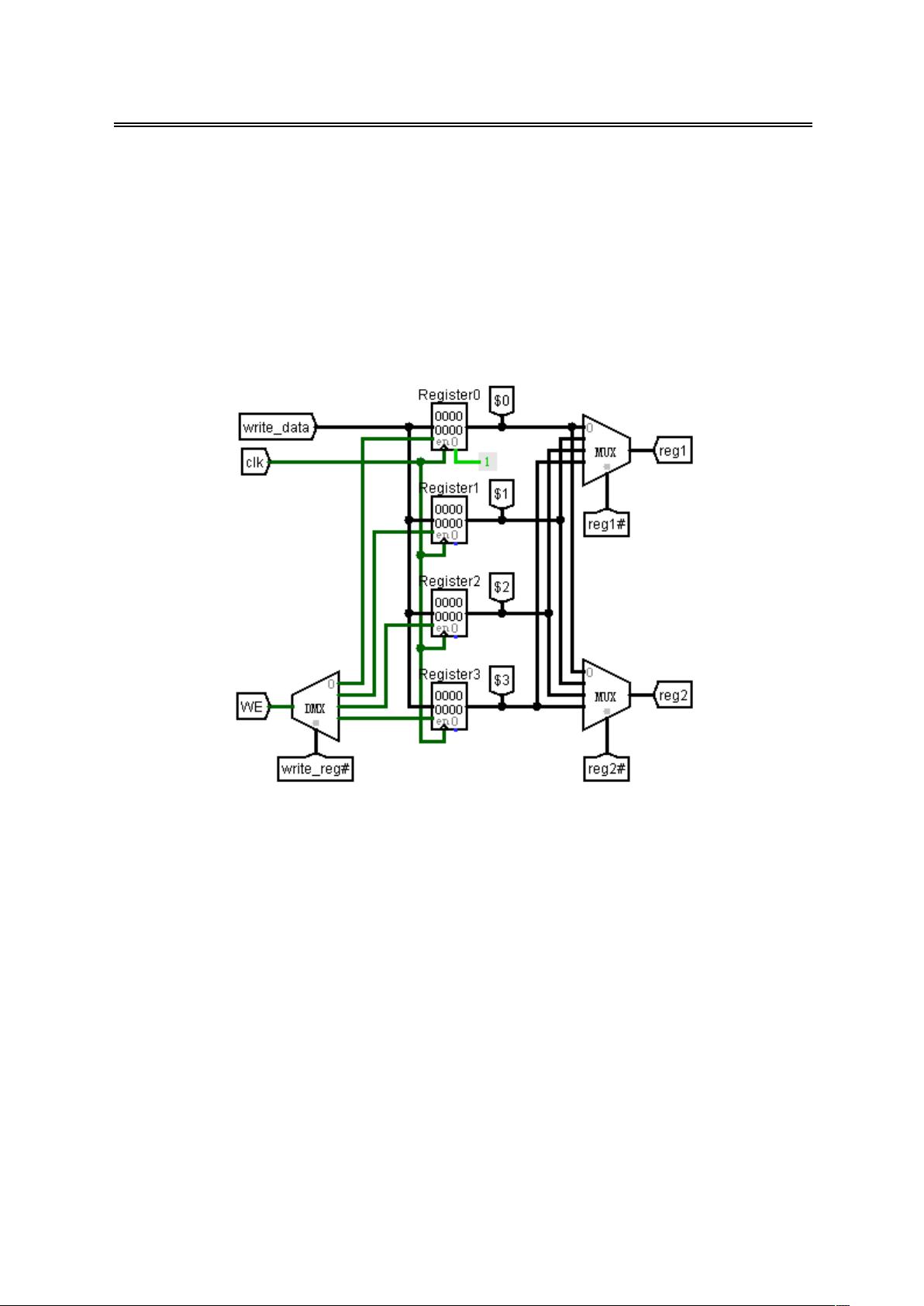

本资源主要介绍了一次MIPS寄存器文件设计实验,目标是利用Logisim平台构建一个包含4个32位寄存器的MIPS寄存器组。设计的关键点包括:

1. 寄存器结构:

实验将原始的32个寄存器简化为4个,仅使用低2位作为寄存器的片选信号,其余高位被忽略。这样做的目的是为了简化设计并提高效率。

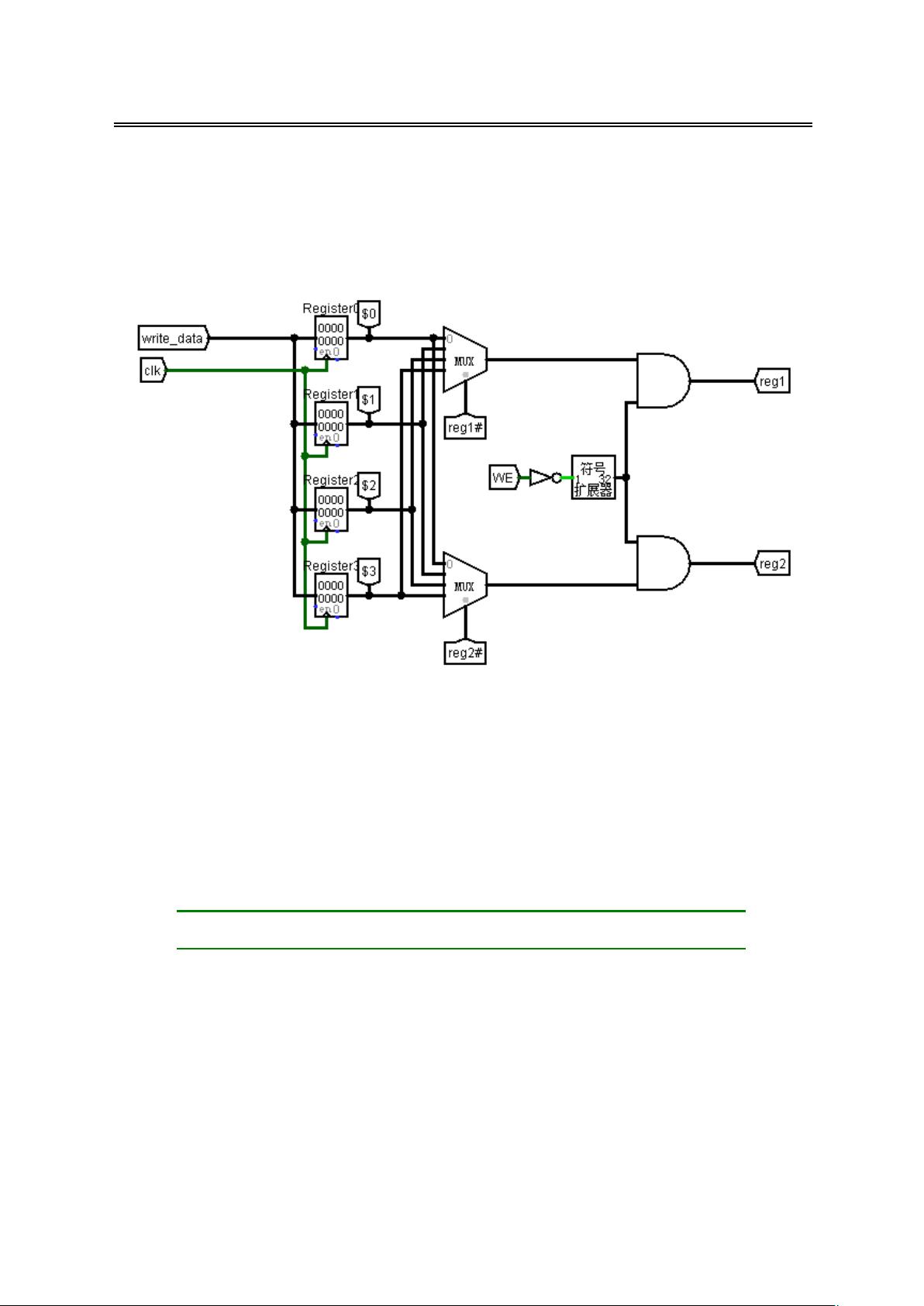

2. 功能实现:

- 读取操作:允许同时读取两个寄存器的值,通过读寄存器编号(R1#和R2#)选择相应的寄存器输出,例如,当reg1#为00、01、10或11时,分别对应0、1、2和3号寄存器。

- 写入操作:写使能WE信号控制数据写入,根据写寄存器编号W#决定将WE信号分配给相应寄存器,其他寄存器的写使能保持为0,防止意外写入。

- 特殊处理:零号寄存器始终保持值为0,通过将其清零端设置为恒1信号实现。

3. 输入输出处理:

- 输入信号处理:为了适应4个寄存器的设计,原5位片选信号被转换为两位。读写信号(如R1#、R2#和W#)的高位被丢弃,低两位用于实际操作。

- 隧道技术:实验中使用隧道连接,避免了过多的连线,提高了信号的复用性。

4. 同步与异步:

所有的读写操作都确保同步进行,通过始终信号保证所有操作在时钟信号clk下完成,避免了异步操作可能带来的问题。

5. 逻辑选择器应用:

读寄存器和写寄存器的操作分别使用了多路选择器,选择器的选择信号(如reg1#和reg2#)与写使能信号的分配是相反的过程,体现了逻辑设计中的互补关系。

这个实验着重于理解MIPS寄存器文件的基本原理,涉及数字逻辑设计、信号处理以及多路选择器的应用,同时也锻炼了学生的逻辑分析和电路实现能力。

2022-08-08 上传

2022-08-04 上传

2022-08-08 上传

2008-10-01 上传

2011-07-26 上传

天眼妹

- 粉丝: 28

- 资源: 332

最新资源

- SSM动力电池数据管理系统源码及数据库详解

- R语言桑基图绘制与SCI图输入文件代码分析

- Linux下Sakagari Hurricane翻译工作:cpktools的使用教程

- prettybench: 让 Go 基准测试结果更易读

- Python官方文档查询库,提升开发效率与时间节约

- 基于Django的Python就业系统毕设源码

- 高并发下的SpringBoot与Nginx+Redis会话共享解决方案

- 构建问答游戏:Node.js与Express.js实战教程

- MATLAB在旅行商问题中的应用与优化方法研究

- OMAPL138 DSP平台UPP接口编程实践

- 杰克逊维尔非营利地基工程的VMS项目介绍

- 宠物猫企业网站模板PHP源码下载

- 52简易计算器源码解析与下载指南

- 探索Node.js v6.2.1 - 事件驱动的高性能Web服务器环境

- 找回WinSCP密码的神器:winscppasswd工具介绍

- xctools:解析Xcode命令行工具输出的Ruby库