轻量级UVM寄存器模型框架

需积分: 13 139 浏览量

更新于2024-09-08

1

收藏 370KB PDF 举报

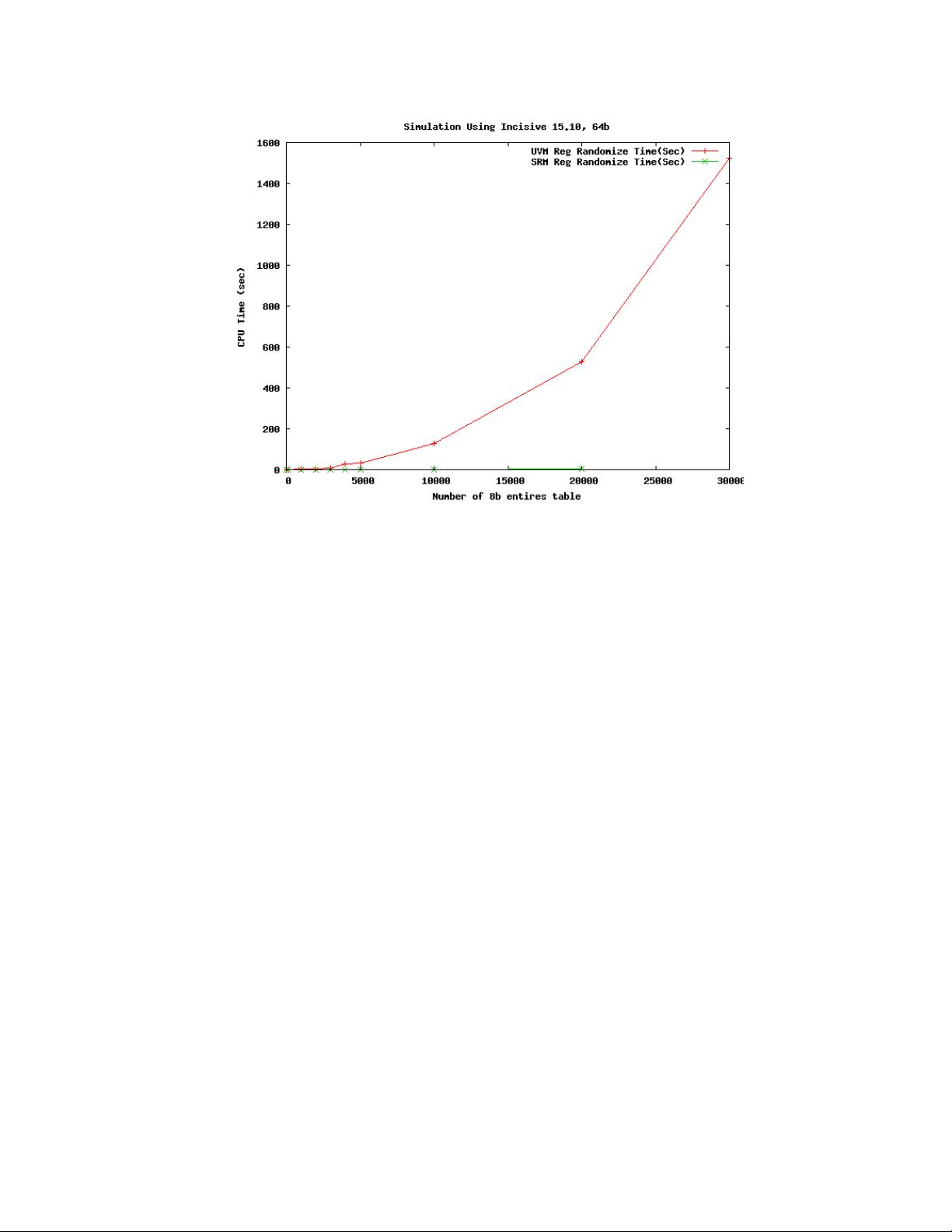

"本文档介绍了一种用于UVM测试平台的简化寄存器模型包,旨在解决UVM自带的UVM_register包在处理大量寄存器和嵌入式内存时性能下降以及API使用复杂的问题。"

在IC数字设计验证领域,UVM(Universal Verification Methodology)是一种广泛使用的系统级验证框架。UVM Register Package是UVM标准库的一部分,它提供了一套工具来建模和管理设计中的软件可见寄存器和内存。然而,对于大型系统级测试平台来说,这个包可能会导致显著的加载和构建时间延迟,特别是在处理数千个寄存器和内存的情况下。此外,UVM的当前寄存器访问API混合了随机化和访问策略等独立关注点,使得使用起来较为困惑。

为了解决这些问题,文档的作者Sanjeev Singh提出了一种开源、简洁的寄存器模型(Simpler Register Model, SRM)框架。SRM的目标是轻量级且具有更清晰的API,以改善测试编写者的体验。该框架的源代码遵循MIT许可证发布,并可在GitHub上获取。

I. 引言部分强调了当前UVM寄存器模型的问题,并提出了开发SRM的动机。SRM不仅减轻了性能负担,而且通过提供更简单的API,使得测试开发者能够更高效、更直观地处理寄存器操作。

II. 背景与动机

在深入理解SRM之前,理解UVM Register Package的基本概念至关重要。UVM_register包提供了类和方法,如`uvm_reg_block`、`uvm_reg`和`uvm_reg_field`,用于构建层次化的寄存器结构,并支持模拟期间的读写操作、随机化和覆盖检查。这些功能虽然强大,但在大规模设计中可能导致效率问题。

III. SRM框架的关键特性

SRM的核心目标是提供一个更高效的替代方案,它可能包括以下特性:

1. **轻量级设计**:通过减少不必要的复杂性和依赖,提高构建和运行测试的速度。

2. **清晰的API**:使测试编写者更容易理解和使用,避免了当前API中的混淆元素。

3. **独立的关注点**:将随机化逻辑和访问策略分离,使得代码更易于维护和扩展。

4. **可扩展性**:允许添加自定义的访问策略和随机化规则,适应不同的设计需求。

IV. 实现与应用

SRM的实现可能包括重新设计寄存器类和方法,以及优化数据结构以提高性能。同时,它可能提供了转换工具,方便将现有基于UVM_register的模型迁移到新的SRM框架。

V. 结论

SRM的出现是为了应对UVM_register在大型验证环境中的挑战,它有望提供一种更有效、更易用的解决方案。通过采用SRM,验证工程师可以更专注于验证逻辑,而不是底层模型的复杂性,从而提高整个验证流程的效率。

Simpler Register Model Package for UVM TB是一个针对UVM测试平台寄存器建模的改进方案,它致力于解决性能和使用便利性问题,为IC数字设计验证带来更高效的工具。

2024-08-31 上传

2022-02-05 上传

2021-04-09 上传

2021-05-11 上传

2021-05-02 上传

2021-05-26 上传

2017-08-02 上传

paullucas

- 粉丝: 2

- 资源: 4

最新资源

- MATLAB实现小波阈值去噪:Visushrink硬软算法对比

- 易语言实现画板图像缩放功能教程

- 大模型推荐系统: 优化算法与模型压缩技术

- Stancy: 静态文件驱动的简单RESTful API与前端框架集成

- 掌握Java全文搜索:深入Apache Lucene开源系统

- 19计应19田超的Python7-1试题整理

- 易语言实现多线程网络时间同步源码解析

- 人工智能大模型学习与实践指南

- 掌握Markdown:从基础到高级技巧解析

- JS-PizzaStore: JS应用程序模拟披萨递送服务

- CAMV开源XML编辑器:编辑、验证、设计及架构工具集

- 医学免疫学情景化自动生成考题系统

- 易语言实现多语言界面编程教程

- MATLAB实现16种回归算法在数据挖掘中的应用

- ***内容构建指南:深入HTML与LaTeX

- Python实现维基百科“历史上的今天”数据抓取教程