FPGA时序分析与约束实战:七天掌握Altera技术

需积分: 10 169 浏览量

更新于2024-07-26

收藏 16.33MB PDF 举报

“通向FPGA之路---七天玩转Altera之时序篇V1.0”是一份关于FPGA设计中的时序分析和约束的详细教程。这份文档深入讲解了时序分析的基本概念,包括同步逻辑时延模型、时序分析公式以及在Altera器件中的应用。它还介绍了如何使用Timequest时序分析器进行设计约束和分析。

时序分析是FPGA设计中的核心部分,确保电路在指定的时钟周期内正确工作。文档首先介绍了时序分析的基本概念,如时钟抖动与偏斜,这两个因素会影响时钟信号的稳定性和精度。建立时间和保持时间是确保数据在正确时钟边沿捕获的关键,而恢复时间和移除时间则关乎数据在传输过程中的稳定性。LaunchEdge和LatchEdge定义了数据与时钟的关系,Data&ClockTime则进一步解释了这些概念。

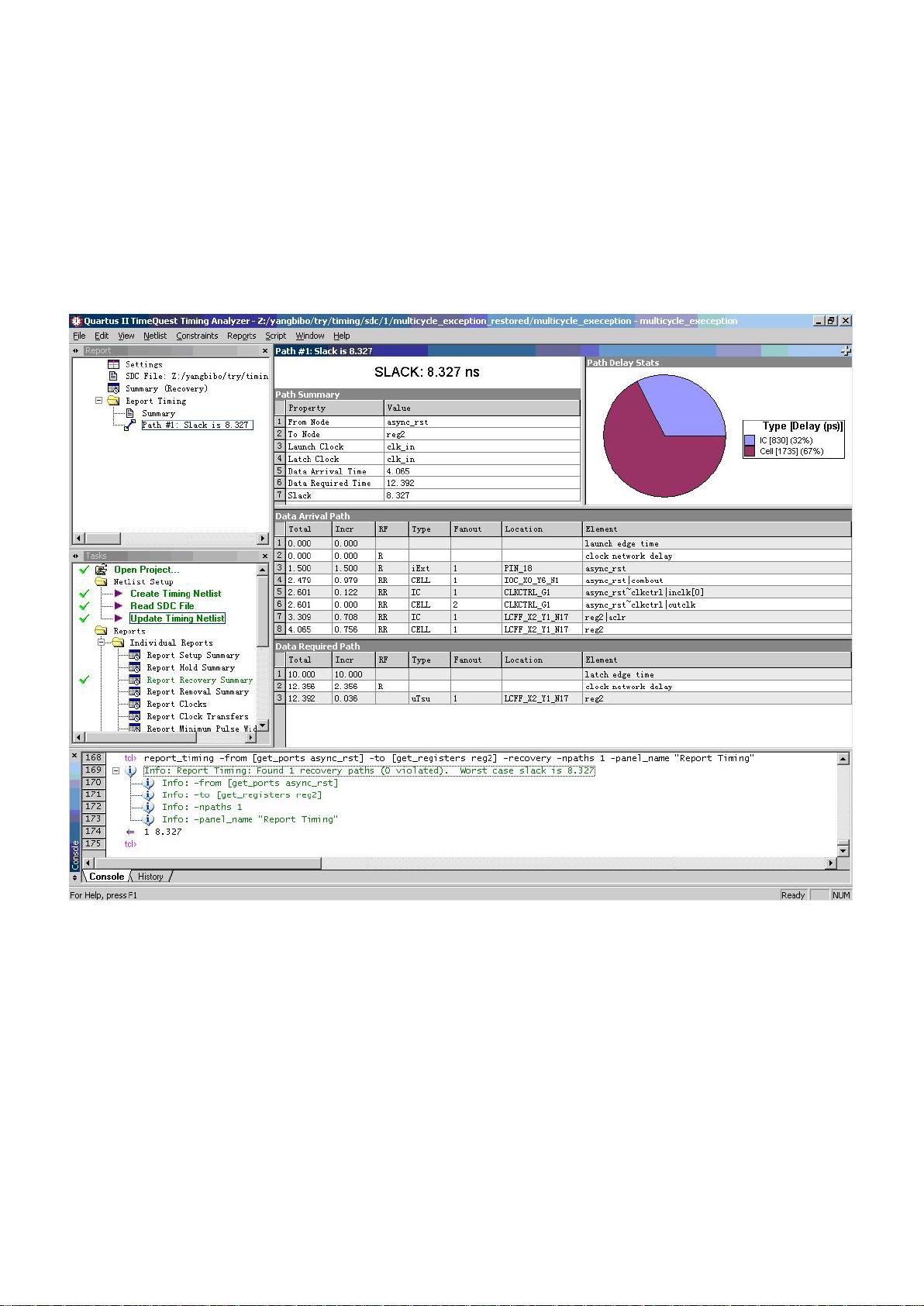

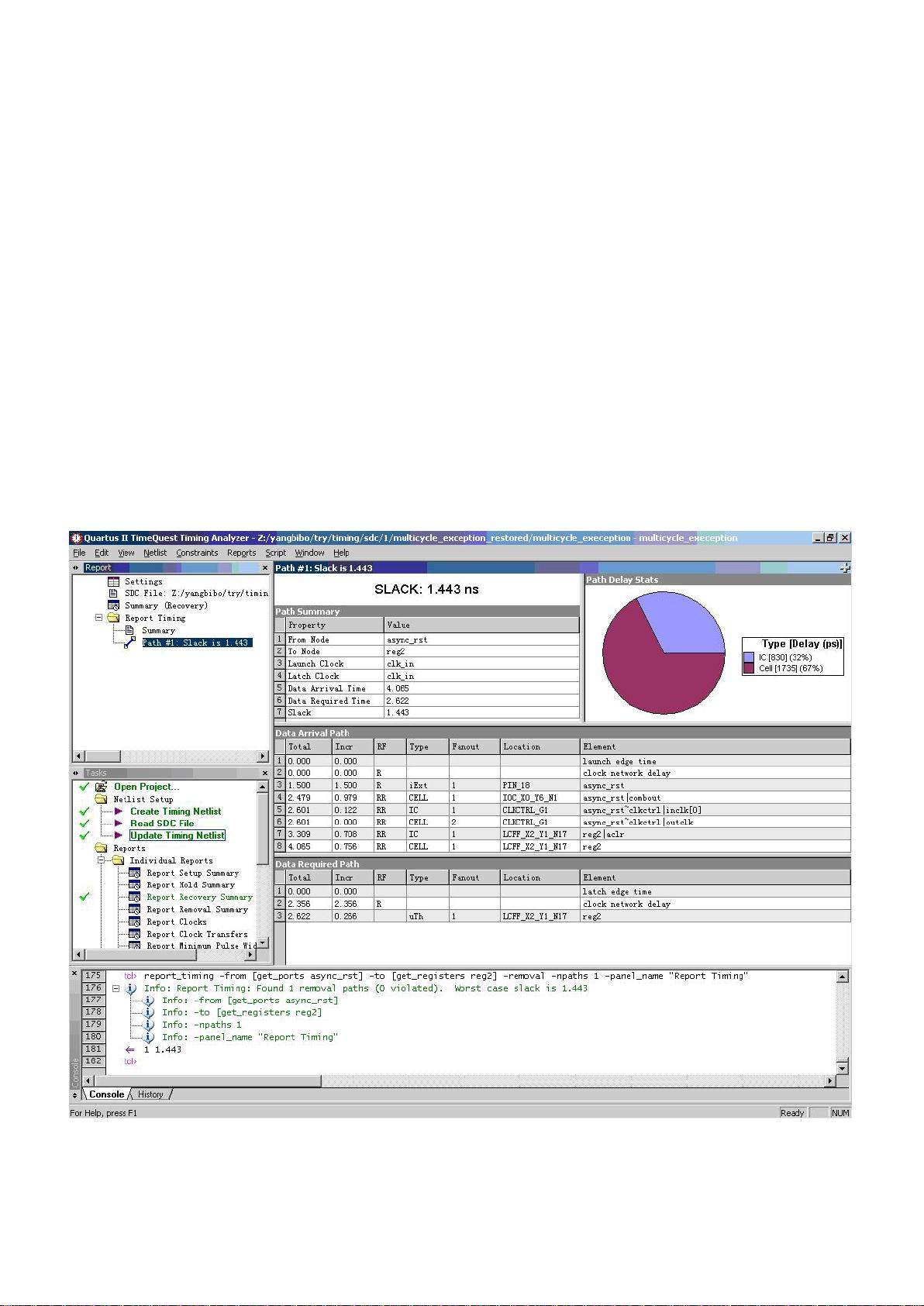

接着,文档详细阐述了时序分析的基本公式,包括设置时间、保持时间、恢复时间和移除时间的检查,这些都是确保电路时序正确的关键指标。多周期路径检查允许在特定路径上放宽时序要求,提高设计灵活性。

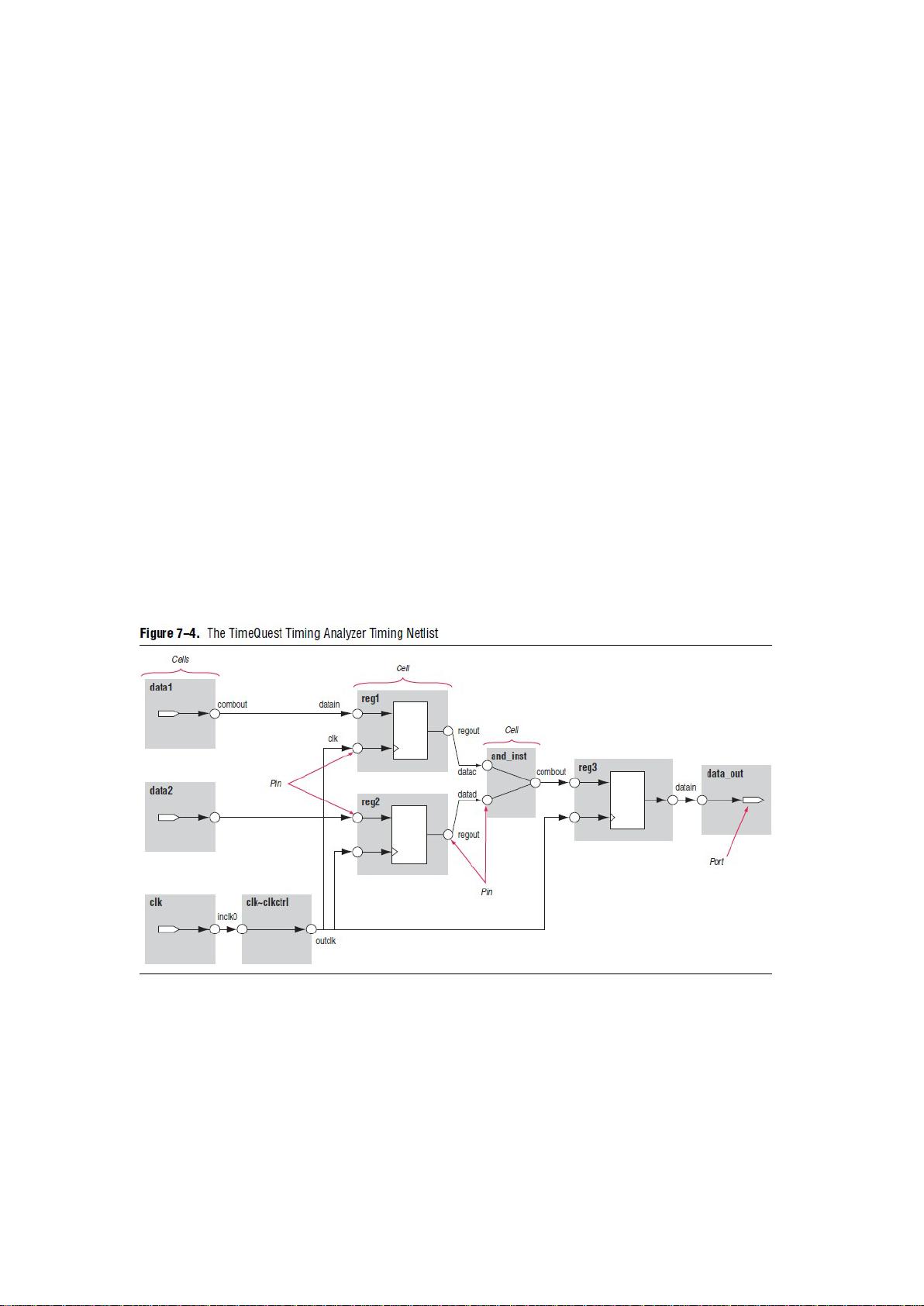

文档还涵盖了Altera器件的时序模型,解释了基本单元和路径如何影响整体时序性能,并讨论了关键路径与时序优化方法。FPGA时序约束的几种方法被提及,这对于确保设计满足时序要求至关重要。

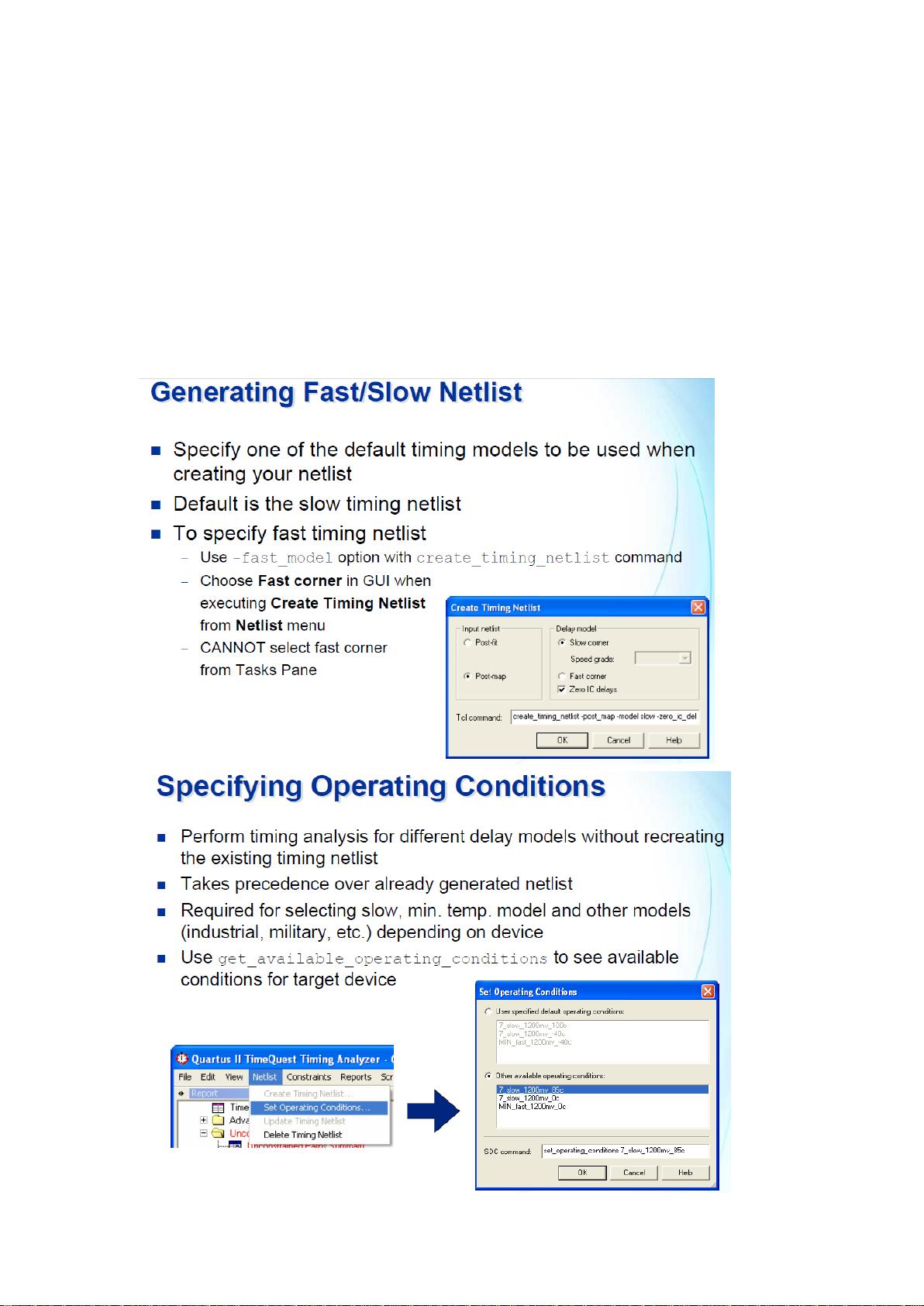

在使用Timequest时序分析器方面,文档提供了基础操作指南,包括约束和分析流程,Timequest的用户界面,以及如何解读时序波形图。此外,还详细讲解了各种时序约束,如时钟约束(创建时钟、生成时钟、PLL时钟、自动检测和创建时钟),以及I/O约束(组合逻辑I/O接口和同步I/O接口)。最后,文档提到了消除时钟延迟、时钟不确定性以及共同时钟路径悲观消除等高级概念,这些都是确保时序分析准确性的关键步骤。

通过这份文档,读者将能够掌握FPGA设计中的时序分析基础,理解Altera器件的时序特性,并学会使用Timequest工具进行有效的时序约束和分析,从而实现高效、可靠的FPGA设计。

2014-06-01 上传

2015-10-08 上传

2022-04-22 上传

2021-10-14 上传

2022-04-22 上传

2012-08-16 上传

2014-06-01 上传

2020-03-13 上传

lvjing_1

- 粉丝: 0

- 资源: 5