掌握L5时序逻辑电路:Verilog设计基础与触发器原理

版权申诉

46 浏览量

更新于2024-07-03

收藏 3.97MB PDF 举报

本资源《数字集成电路原理与设计:L5 时序逻辑电路 verilog.pdf》是一份针对时序逻辑电路深入讲解的文档,由主讲人姜小波提供。主要内容包括:

1. 时序逻辑电路概述:时序逻辑电路是数字电路的重要分类之一,与组合逻辑电路相对,其输出不仅依赖于当前输入,还与其之前的状态有关,因为这类电路通常包含反馈机制,比如通过触发器和寄存器实现状态的存储。这种记忆功能使得时序电路能够在时间和状态上呈现出动态行为。

2. 时序逻辑与组合逻辑区别:时序逻辑电路的特点是具有记忆性,即使在没有外部输入的情况下,其内部状态会保持不变,而组合逻辑电路则没有这种特性,它们的输出只取决于当前的输入。

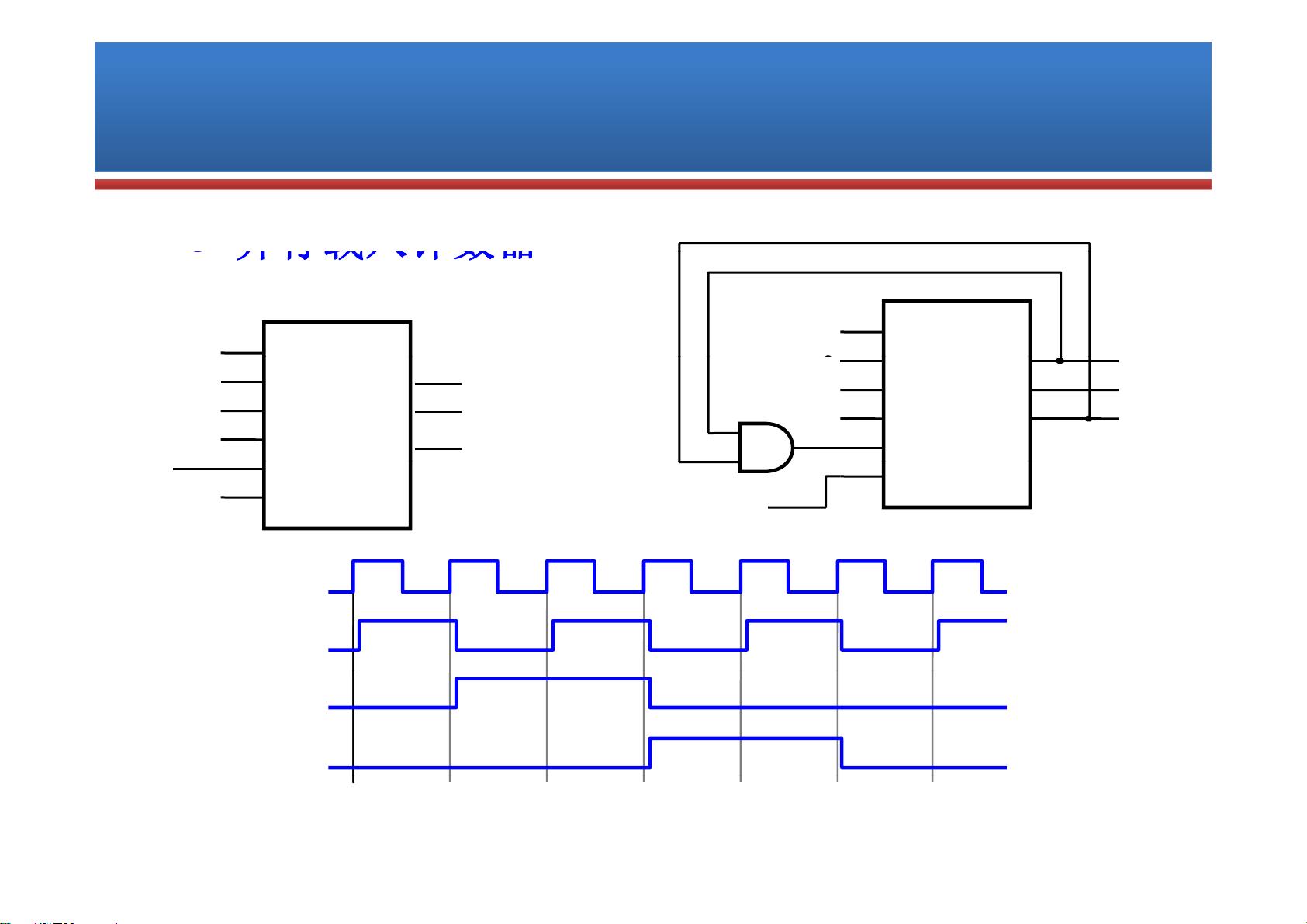

3. 基本组件:时序逻辑电路中的关键组件包括触发器,如D触发器,它是一个具有两个稳定状态(0和1)的逻辑电路,能在输入信号作用下置位并保持新状态。此外,锁存器也是一种重要的存储单元,它会在特定电平触发下改变状态,并且能够反映时间上的变化。

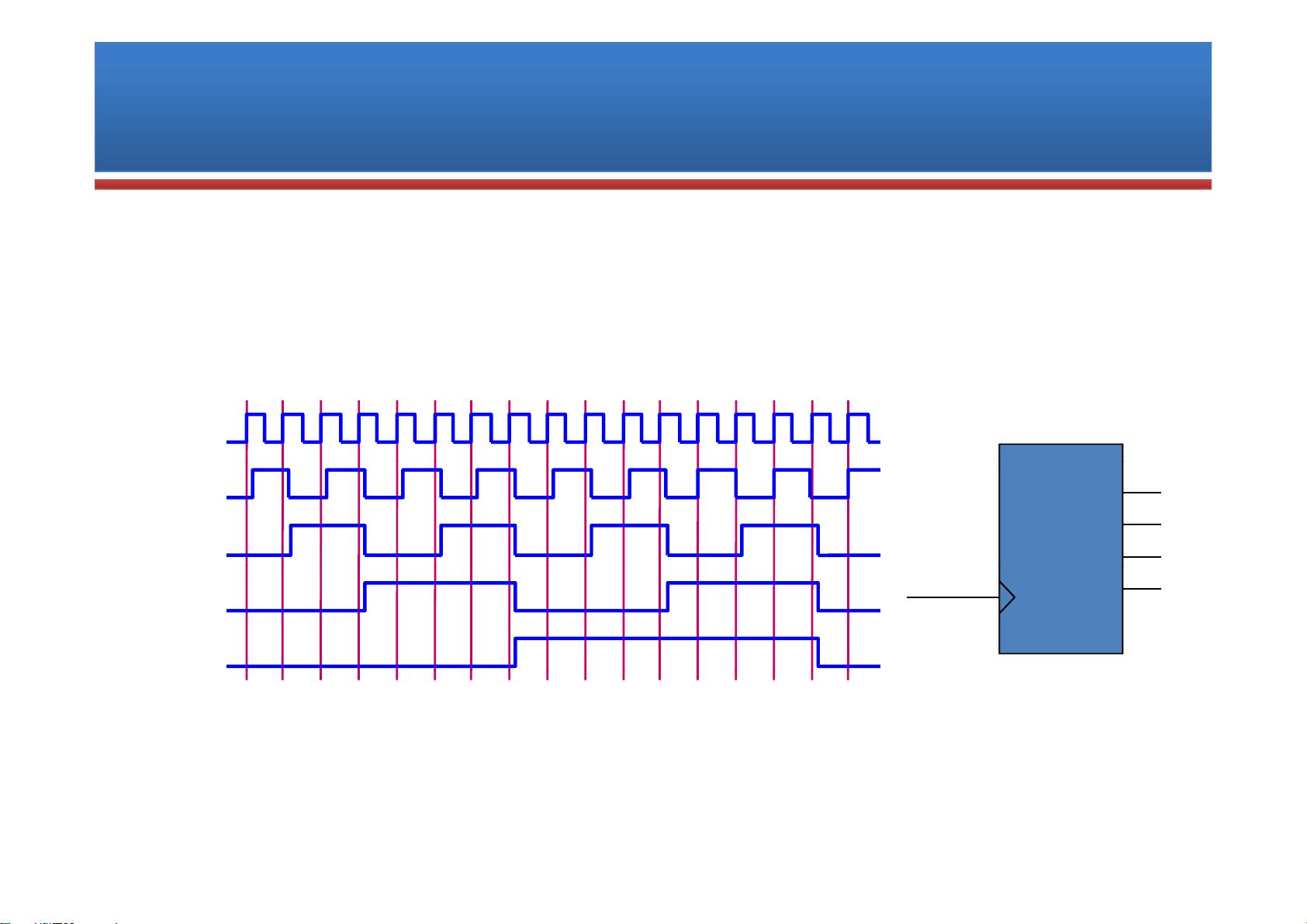

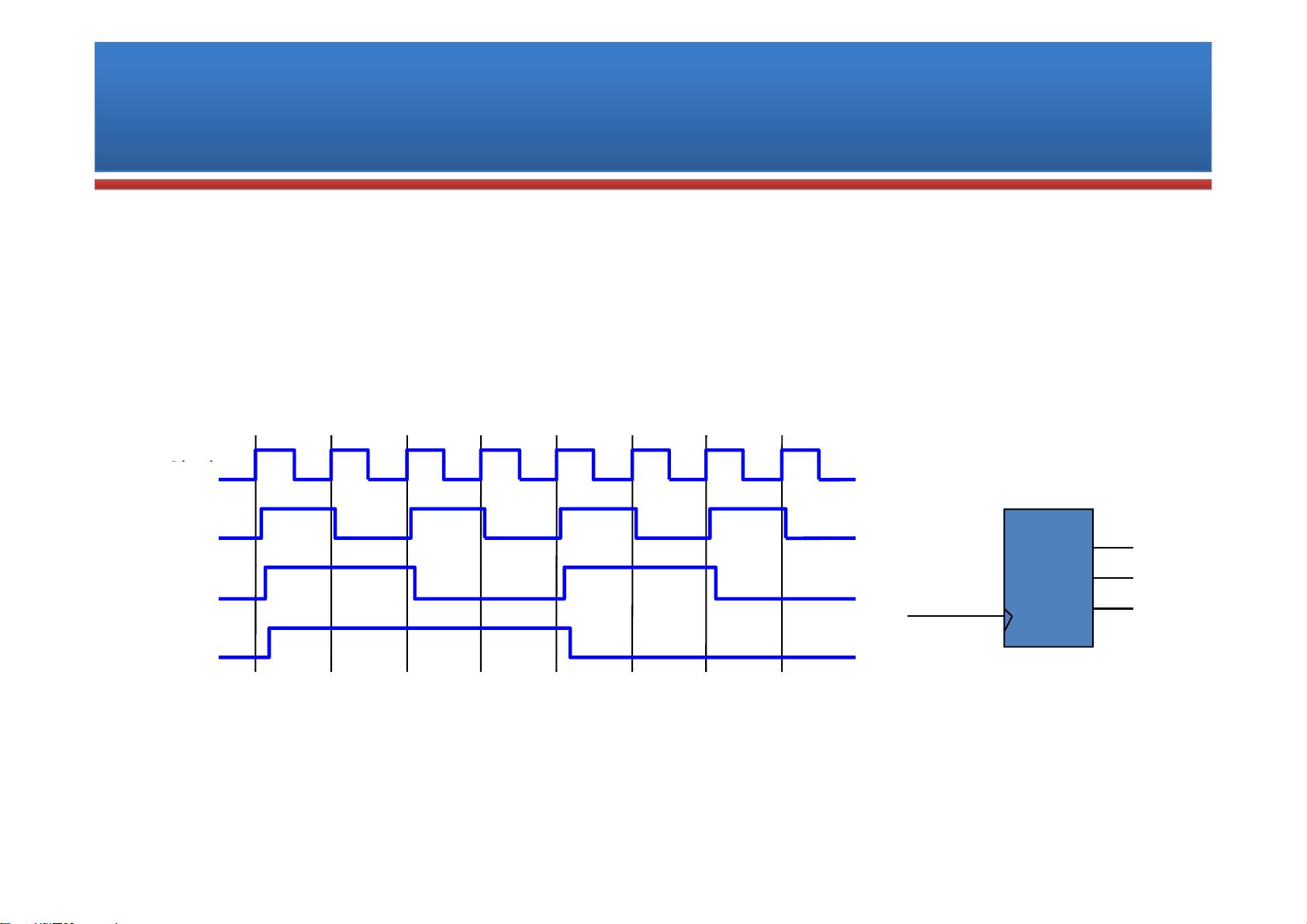

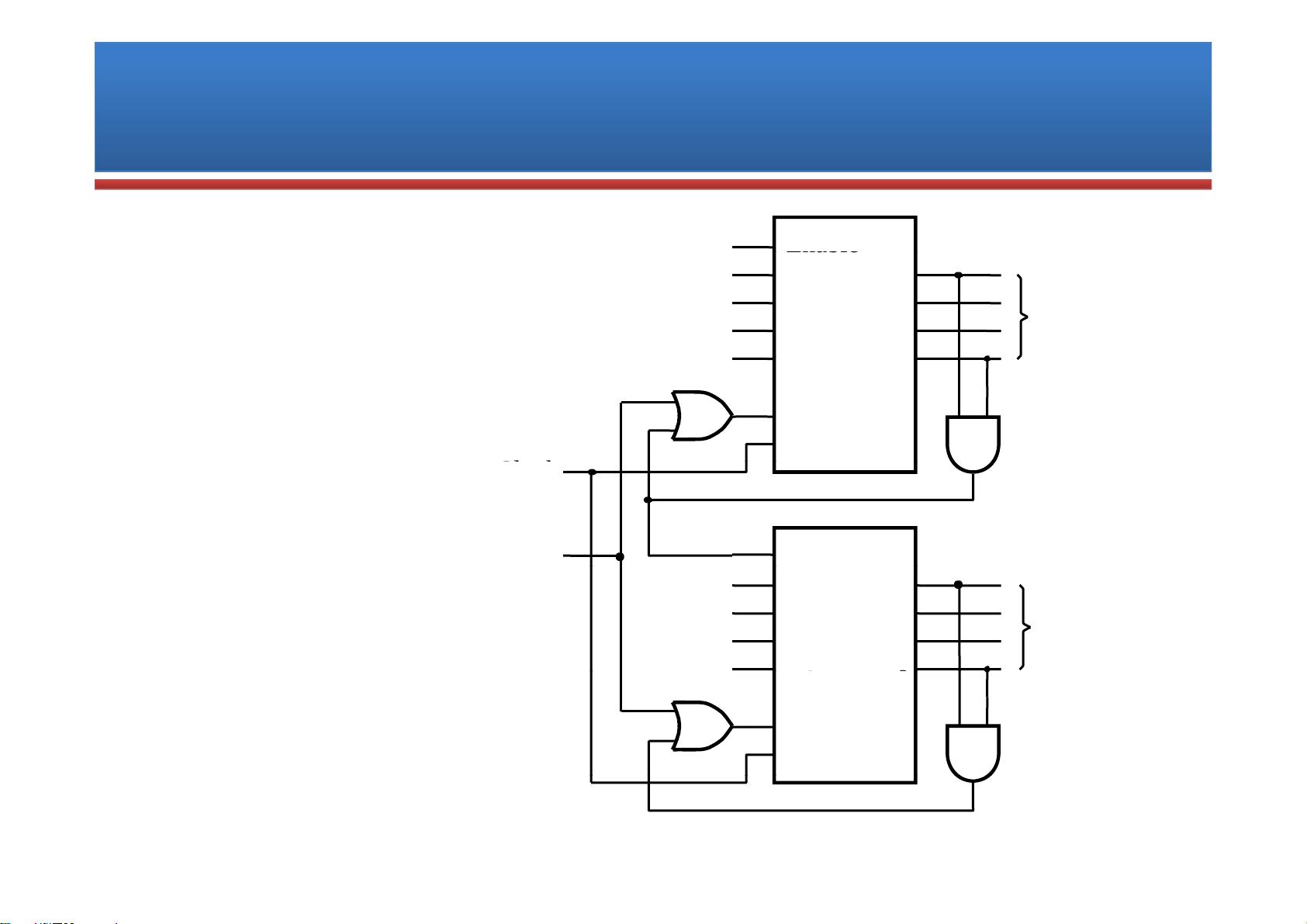

4. 电路结构与符号:文档中展示了时序逻辑电路的框图和真值表,以及对应的时序图,通过这些视觉工具,读者可以更好地理解电路的工作原理和信号传输过程。逻辑符号如触发器和锁存器的图形表示也在此部分呈现。

5. 触发器的特性和类型:D触发器是基础的时序逻辑元件,文档还介绍了负跳变和正跳变D触发器等不同类型的触发器,它们在电路设计中各有其应用场景。

这份文档对于学习和理解数字集成电路设计中的时序逻辑原理,特别是使用Verilog语言进行电路设计的学生来说,是一份宝贵的参考资料,它详尽地阐述了时序逻辑的基本概念、工作原理和实际应用。

2021-09-20 上传

2021-09-20 上传

2022-06-16 上传

2022-06-16 上传

2021-09-20 上传

点击了解资源详情

点击了解资源详情

2021-09-19 上传

2022-07-13 上传