ALTERA FPGA实现DDS信号发生器设计详解

需积分: 5 104 浏览量

更新于2024-08-04

收藏 192KB PDF 举报

"基于ALTERA实现的DDS信号发生器设计"

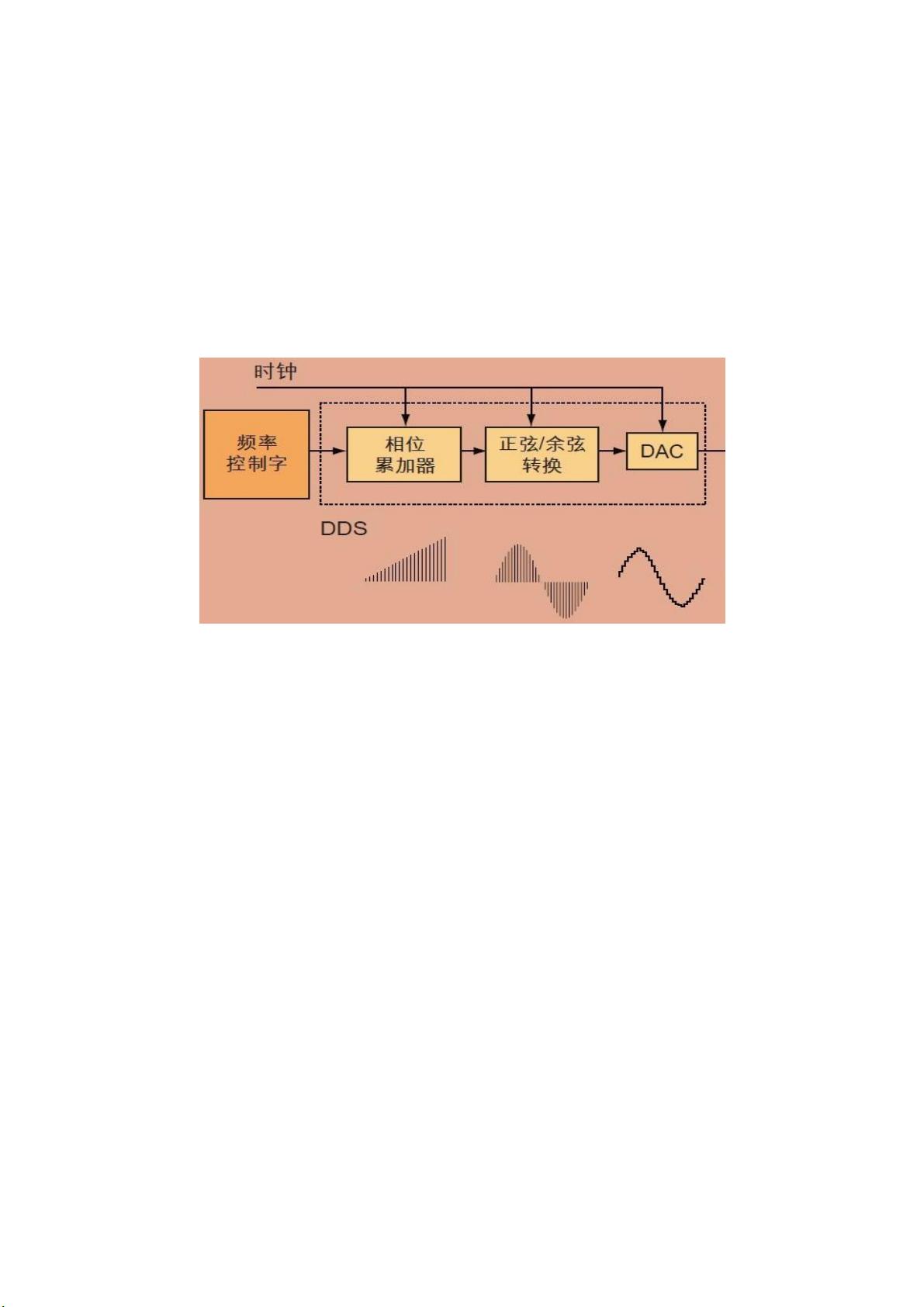

DDS(直接数字频率合成)是一种高效的方法,用于生成高精度、高稳定性的模拟信号。在本文中,我们将深入探讨如何利用ALTERA FPGA实现DDS信号发生器。这个设计的核心是通过相位累加器、相位幅度转换器和数模转换器(DAC)来生成正弦波和余弦波。

1. **DDS系统组成**:

- **相位累加器**:相位累加器是DDS的核心部件,它接收一个相位控制字(FCW),并在这个字上进行累加。累加的结果作为ROM的索引地址,ROM中存储了正弦波的样本点。通常,相位累加器的宽度决定了频率分辨率,而其高位用于ROM的地址选择。

2. **波形调制**:

- 波形的生成是通过对正弦波进行采样和存储实现的。在这个例子中,正弦波被采样了1024个点,并存储在一个8比特、1024深度的ROM中。通过改变相位控制字FCW和时序,可以生成不同频率的波形。频率公式为:FO = TCLK * FCW / 655360,其中TCLK是模块的工作时钟周期,FCW是相位控制字,FO是生成的信号频率。

3. **应用实例**:

- 设定FCW为128时,随着时钟频率CLK的不同,我们可以计算出不同的输出频率。例如,当CLK=50MHz时,计算得到的频率为10kHz;CLK=5MHz时,频率为1kHz;而CLK=100MHz时,频率为0.2MHz。这些实例展示了如何通过调整FCW和CLK来控制输出信号的频率。

4. **实现步骤**:

- 实现DDS信号发生器时,首先要定义工程的输入输出信号。例如,包括系统工作时钟clk,复位信号rst_n,以及其他可能的控制信号。接着,设计相位累加器,根据需要的频率范围确定其位宽。然后,设计相位幅度转换器,这通常是一个查找表(LUT),根据相位累加器的输出选择相应的幅度值。最后,通过数模转换器(DAC)将数字信号转换为模拟信号输出。

5. **平台与结果**:

- 设计完成后,需要在ALTERA FPGA平台上进行硬件验证。通过观察和分析输出波形,确保其频率和理论计算一致,从而验证DDS信号发生器设计的正确性。

通过这样的设计,我们可以灵活地生成各种频率的正弦波,这对于通信、测试和测量以及许多其他应用来说都是极其重要的。ALTERA FPGA的高速处理能力和丰富的资源使得DDS信号发生器的实现变得更加高效和可靠。

123 浏览量

2020-06-19 上传

点击了解资源详情

点击了解资源详情

2020-11-03 上传

2019-09-04 上传

2012-01-31 上传

2021-02-03 上传

2018-04-24 上传

weixin_43453163

- 粉丝: 0

- 资源: 6

最新资源

- 图形演示系统matlab代码-LinkLevelMCSim:该课程项目的目的是执行链接级别的蒙特卡洛模拟,以研究无线信道上卷积码的性能

- 轻公主项目

- Get Cookie For HL.VN-crx插件

- WayneHillsNow:新泽西州FBLA州移动应用开发竞赛第一名

- alexalemi.github.io:个人网站

- Appium-Inspector

- 单片机C语言实例--21-8位数码管显示其中之一.zip

- nginxconfig.io::gear:类固醇上的NGINX配置生成器:syringe:

- GitJasmine-crx插件

- jade-email-builder:http

- penguin-tracking-antarctica:该演示包含阿德利企鹅在小鸡饲养期间在 Antactica 的觅食行为。 曲目录制于2018年

- voila-heroku-secure:一种模板配置,用于承载在heroku上认证的voila密码

- 图形演示系统matlab代码-PalEx:派克斯

- 常用AD元件库、封装库、3D封装库.zip

- xluo ajax+ASP.NET文章系统 v1.0

- windows mysqldump.zip