基于CPLD/FPGA的出租车计费系统设计

需积分: 9 192 浏览量

更新于2024-09-20

1

收藏 102KB DOC 举报

"基于CPLD/FPGA的出租车计费器设计"

基于CPLD/FPGA的出租车计费器是利用现代电子设计自动化(EDA)技术,特别是可编程逻辑器件的优势,构建的一种高效、灵活且成本效益高的电子系统。CPLD(复杂可编程逻辑器件)和FPGA(现场可编程门阵列)是这种技术的核心,它们允许设计者根据需求定制电路,缩短开发周期,提高系统的可靠性和知识产权保护。

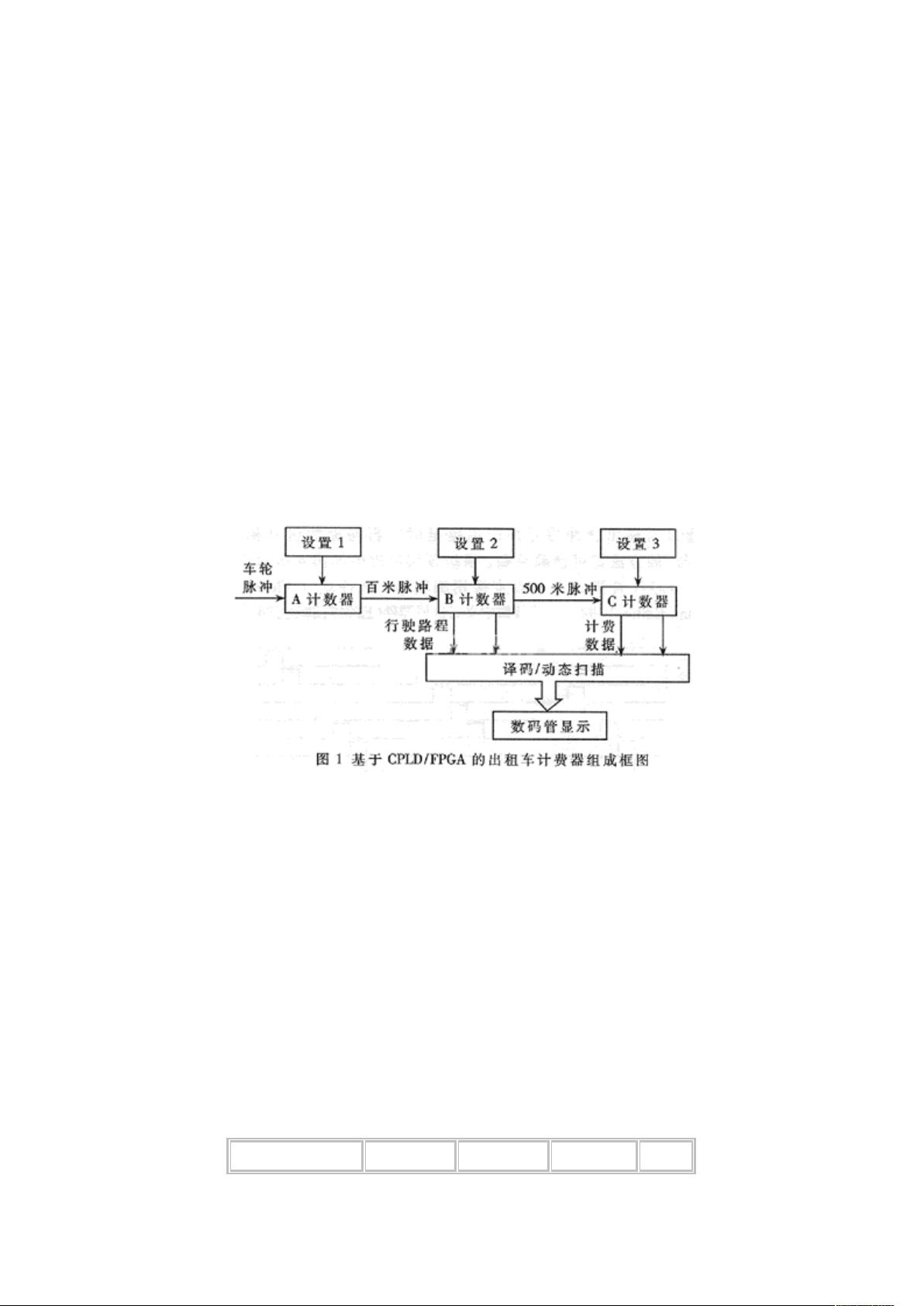

本文中,设计者采用了Altera公司的EPM7128SLC84-15作为核心控制器,这是一个CPLD芯片,用于处理出租车计费的各种逻辑运算和控制任务。该计费器系统由多个关键部分组成:

1. **车型调整模块**:由于不同出租车的车轮直径不同,此模块通过DIP开关设置来适应不同车型。系统根据设定的分频系数(例如61、59、57、55),确保每100米行程产生一个脉冲,以保持计程的准确性。

2. **计程模块**:包括A计数器,它接收车轮传感器的脉冲信号并计数。每转一圈车轮发送一个脉冲,根据车型设置进行修正。B计数器则对这些脉冲进行累加,以计算实际行驶的公里数,并通过译码器动态扫描模块输出BCD码。

3. **计费模块**:C计数器在此阶段发挥作用,根据预设的步长(即单价)进行累加计数,通常每500米计费一次。此外,它还支持起步价和超价加费的设定,这些功能可以通过“设置3”进行调整。

4. **译码/动态扫描模块**:将计算的公里数和费用转换为数字信号,然后利用动态扫描技术驱动LED数码管显示。显示内容包括三位整数和一位小数的公里数和计费金额。

5. **数码管显示模块**:四组LED数码管分别显示公里数和费用,提供清晰直观的读数。

设计过程中,所有功能模块都使用硬件描述语言VHDL进行编写,然后在顶层原理图中将它们集成在一起。这种模块化设计方法使得代码可重用,易于调试和维护。

总结来说,基于CPLD/FPGA的出租车计费器利用了现代电子技术的先进性,实现了高度定制化和灵活性,确保了计费的精确性,同时降低了开发成本。其设计过程展示了EDA技术在解决实际问题中的应用,以及VHDL编程在实现复杂逻辑功能方面的强大能力。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2020-10-26 上传

2020-12-13 上传

2021-02-01 上传

2021-01-19 上传

2020-12-08 上传

2021-05-18 上传

jinboking

- 粉丝: 0

- 资源: 2

最新资源

- JHU荣誉单变量微积分课程教案介绍

- Naruto爱好者必备CLI测试应用

- Android应用显示Ignaz-Taschner-Gymnasium取消课程概览

- ASP学生信息档案管理系统毕业设计及完整源码

- Java商城源码解析:酒店管理系统快速开发指南

- 构建可解析文本框:.NET 3.5中实现文本解析与验证

- Java语言打造任天堂红白机模拟器—nes4j解析

- 基于Hadoop和Hive的网络流量分析工具介绍

- Unity实现帝国象棋:从游戏到复刻

- WordPress文档嵌入插件:无需浏览器插件即可上传和显示文档

- Android开源项目精选:优秀项目篇

- 黑色设计商务酷站模板 - 网站构建新选择

- Rollup插件去除JS文件横幅:横扫许可证头

- AngularDart中Hammock服务的使用与REST API集成

- 开源AVR编程器:高效、低成本的微控制器编程解决方案

- Anya Keller 图片组合的开发部署记录