掌握FPGA时序分析:共同时钟系统与信号完整性

需积分: 9 107 浏览量

更新于2024-09-14

收藏 282KB DOC 举报

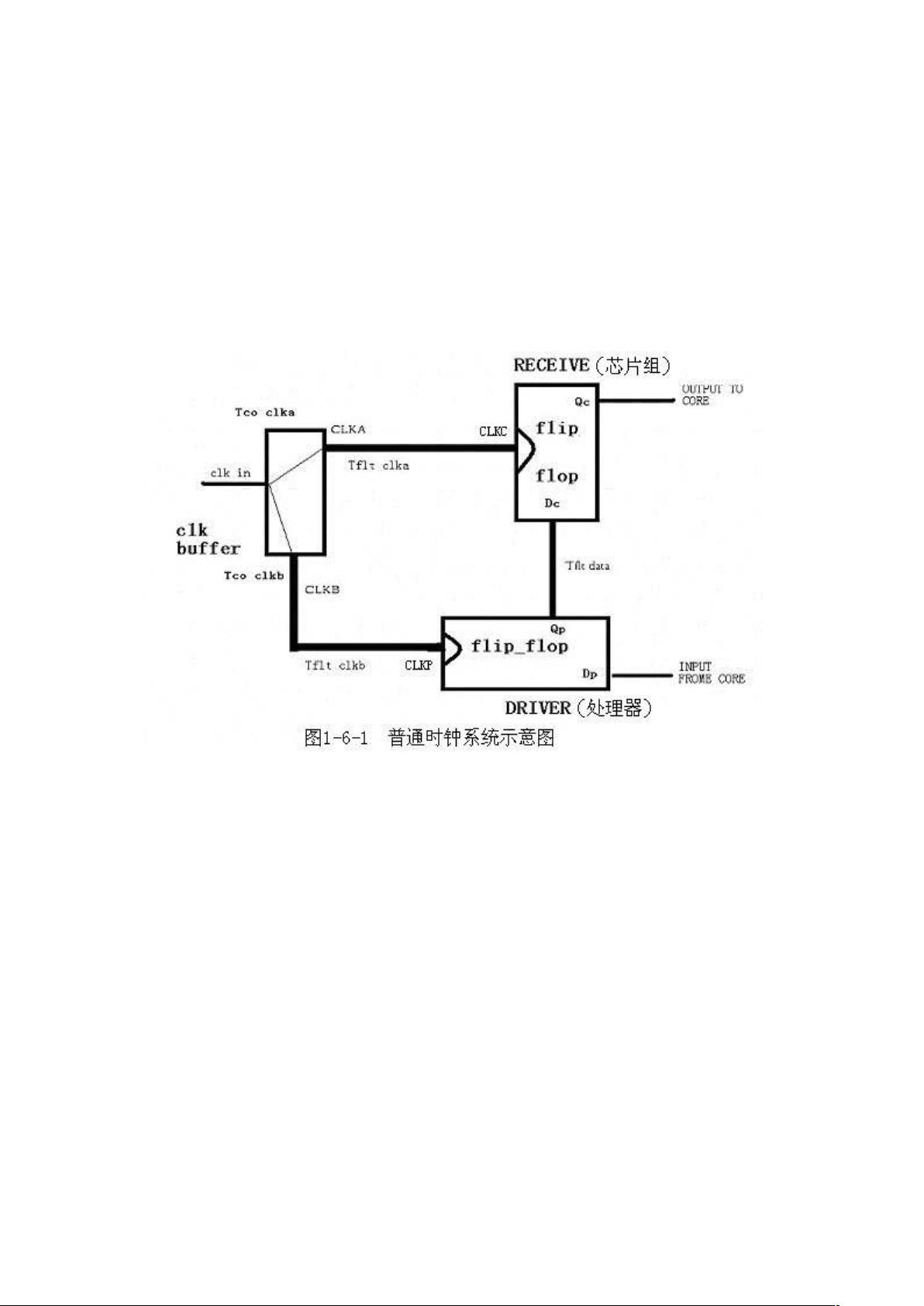

FPGA时序分析是系统设计中至关重要的部分,特别是在高速应用中,如计算机系统的前端总线设计。它涉及到如何在有限的时间窗口内确保数据准确无误的传输,以维持系统稳定性。在FPGA设计中,时序分析主要关注两个关键方面:普通时序系统(共同时钟系统)和源同步系统时序。

普通时序系统,如处理器与芯片组间的连接,依赖于单一的系统时钟。在这种体系中,发送者(处理器)在时钟上升沿将数据锁存并发送,接收者(芯片组)在下一个时钟上升沿接收数据。数据传输需要连续两个时钟周期,如果传输延迟超过这个周期,会导致数据错误。由于频率提升会限制传输线上的延时,普通时钟系统的频率通常受限在200-300MHz,这是由时序约束决定的。

时序参数的确定是时序分析的核心,主要包括建立时间和保持时间。建立时间是从时钟上升沿到数据稳定输出所需的时间,保持时间则是数据在输出端保持稳定的时间。这两个时间参数必须被严格遵守,以防止数据丢失或错误。保持时间过短可能导致数据在接收前消失,而建立时间不足则会导致接收端错过正确的数据。

源同步系统时序则是另一个关键概念,它涉及数据发送者根据接收者的需求来调整其发送时钟,确保数据接收的一致性和准确性。这种系统能够更好地管理时序,尤其是在多时钟域设计中,但设计更为复杂,需要额外的逻辑来协调不同时钟的交互。

FPGA时序分析不仅关注信号完整性的维护,还涉及到电路设计的优化,包括选择合适的布线策略、使用适当的速度等级、合理安排逻辑单元,以减小延迟并确保满足设计规范。此外,现代FPGA工具如ModelSim、Xilinx ISE或Vivado等提供了强大的时序分析工具,设计师可以利用这些工具进行详细的仿真和验证,确保设计的正确性和性能。

总结来说,FPGA时序分析是设计过程中的重要环节,它决定了系统的可靠性和性能极限。掌握时序参数、理解和应用不同的时序模型,如普通时钟系统和源同步系统,是每个FPGA工程师必备的技能。同时,深入理解信号完整性和有效的时序设计策略是确保高质量FPGA设计的关键。

212 浏览量

150 浏览量

246 浏览量

141 浏览量

2009-04-11 上传

380 浏览量

点击了解资源详情

点击了解资源详情

a245313109a

- 粉丝: 0

最新资源

- 掌握PerfView:高效配置.NET程序性能数据

- SQL2000与Delphi结合的超市管理系统设计

- 冲压模具设计的高效拉伸计算器软件介绍

- jQuery文字图片滚动插件:单行多行及按钮控制

- 最新C++参考手册:包含C++11标准新增内容

- 实现Android嵌套倒计时及活动启动教程

- TMS320F2837xD DSP技术手册详解

- 嵌入式系统实验入门:掌握VxWorks及通信程序设计

- Magento支付宝接口使用教程

- GOIT MARKUP HW-06 项目文件综述

- 全面掌握JBossESB组件与配置教程

- 古风水墨风艾灸养生响应式网站模板

- 讯飞SDK中的音频增益调整方法与实践

- 银联加密解密工具集 - Des算法与Bitmap查看器

- 全面解读OA系统源码中的权限管理与人员管理技术

- PHP HTTP扩展1.7.0版本发布,支持PHP5.3环境