"本文主要介绍了如何使用74LS161同步四位二进制计数器构建从0开始的十进制计数器,并探讨了如何通过改变输入信号实现不同进制计数的方法。74LS161是一种中规模集成电路,具有同步并行置数功能,通常用于实现二进制加法计数。通过分析其逻辑功能、外部引脚、逻辑符号、功能表和时序图,我们可以理解其工作原理。此外,文中还提到了脉冲反馈法在构建任意进制计数器中的应用,以及如何利用与非门拾取特定状态来实现特定进制计数。"

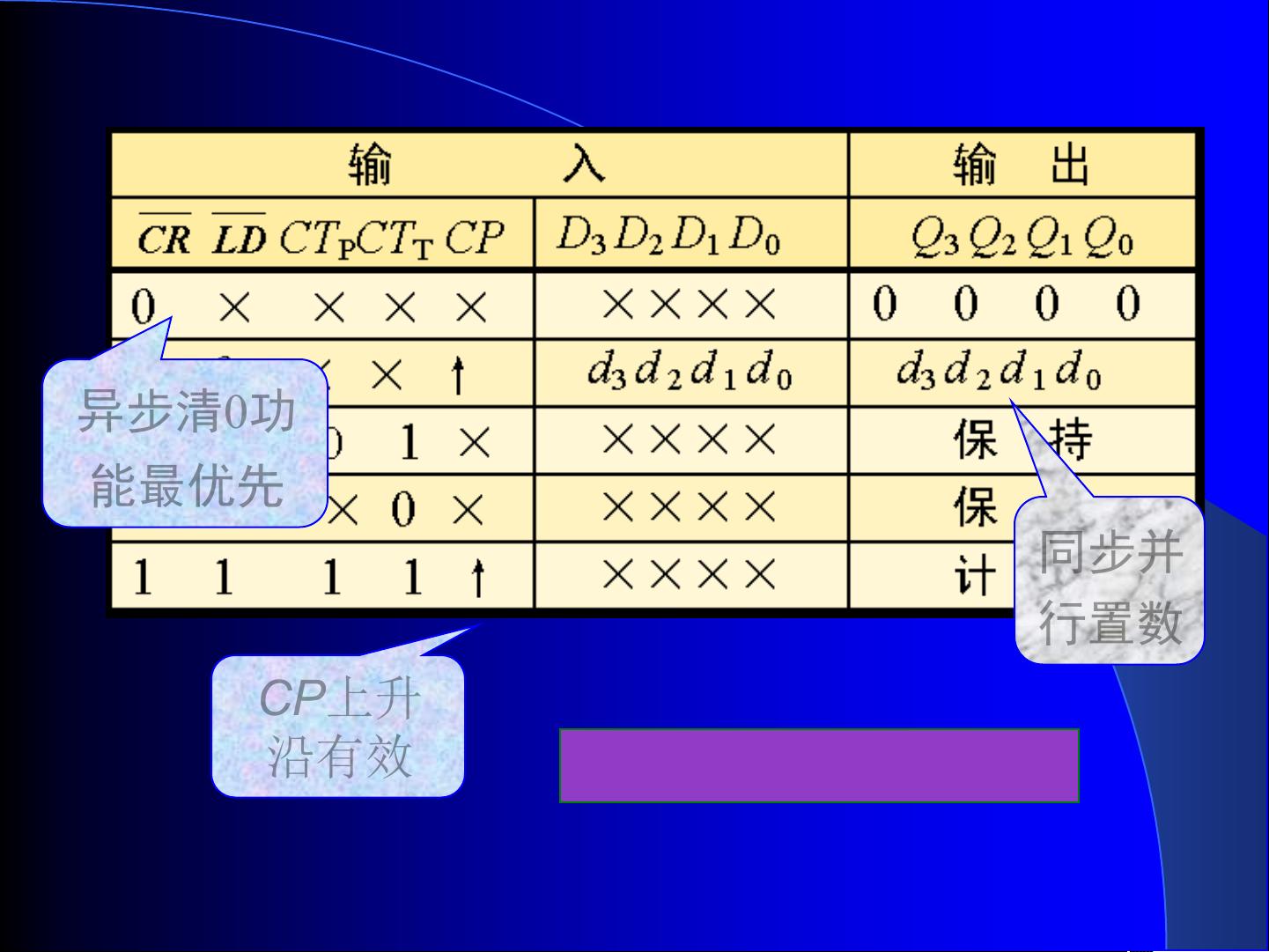

74LS161是一个同步四位二进制计数器,它在每个时钟脉冲的上升沿有效时进行计数,支持异步清零和同步并行置数功能。该芯片的外部引线包括输入时钟脉冲(CP)、异步清零(CLR)、同步并行置数输入(D3D2D1D0)以及进位输出(CO)。74LS161的功能表展示了在不同的输入条件下,输出状态(Q3Q2Q1Q0)的变化情况。

为了实现从0开始的十进制计数,我们可以利用74LS161的并行置数功能,设置D3D2D1D0的初始状态为0000。随着时钟脉冲的增加,计数器将依次经过0000、0001、0010、0011、0100、0101、0110、0111、1000、1001这十个状态,形成0到9的十进制计数。进位输出CO在达到最大计数值(1001)时变为高电平,可用于触发下一个计数周期。

除了二进制计数,74LS161还可以通过调整预置数(D3D2D1D0)和使用脉冲反馈法构建任意进制的计数器。例如,要实现十进制计数,我们可以设定D3D2D1D0 = 0110,并利用与非门拾取状态1010(在十进制计数器中对应1001,因为是二进制表示),当计数器到达这个状态时,通过反馈信号重置计数器回到初始状态,从而实现0到9的循环计数。

脉冲反馈法的关键在于确定何时发出置数信号。对于异步置数,置数信号在接收到第N个计数脉冲后产生,使计数器返回到预置状态SM;而对于同步置数,置数信号在第N-1个脉冲后产生,确保在第N个脉冲时生效,使得计数器能够准确回到SM状态,完成SM到SN-1的计数。

74LS161构成的十进制计数器电路通常包括与非门等逻辑门电路,用于捕获特定状态的输出,如1010,以便在适当的时候触发置数操作。通过改变这些与非门的输入配置,我们可以构建计数不同进制的计数器,例如二进制、八进制或十六进制。

74LS161是一个强大的计数器集成电路,不仅适用于基本的二进制计数,还能通过巧妙设计实现更复杂的计数需求。理解和掌握它的逻辑功能、置数机制和脉冲反馈法,对于设计和实现数字系统中的计数模块至关重要。